## AH212-EG (Lead-Free QFN 4x5 mm Package) Mechanical Information

This package is lead-free/green/RoHS-compliant. The plating material on the leads is Matte Tin. It is compatible with both lead-free (maximum 260 °C reflow temperature) and lead (maximum 245 °C reflow temperature) soldering processes.

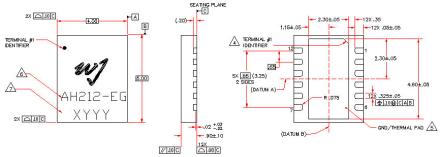

### **Outline Drawing**

#### NOTES

- EXCEPT WHERE NOTED, THIS PART OUTLINE CONFORMS TO JEDEC STANDARD MO—229, ISSUE C (VARIATION VJGC) FOR THERMALLY ENHANCED PLASTIC VERY THIN FINE PITCH QUAD FLAT NO LEAD PACKAGE (QFN).

- DIMENSIONING & TOLERANGING CONFORM TO ASME Y14.4M-1994.

- ALL DIMENSIONS ARE IN MILLIMETERS. ANGLES ARI IN DEGREES.

- THE TERMINAL # IDENTIFIER AND TERMINAL NUMBERING CONVENTION CONFORM TO JESD 95-1 SPP-012.

- COPLANARITY APPLIES TO THE EXPOSED GROUND/THERMAI PAD AS WELL AS THE TERMINALS.

- 6 PART NUMBER

- ALPHA-NUMERIC LOT CODE.

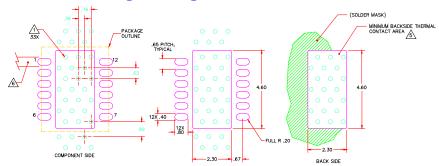

## **Mounting Configuration / Land Pattern**

# **Thermal Specifications**

| Parameter                    | Rating        |

|------------------------------|---------------|

| Operating Case Temperature   | -40 to +85 °C |

| Thermal Resistance (1), Rth  | 33 °C / W     |

| Junction Temperature (2), Tj | 156 °C        |

### Notes:

1. The thermal resistance is referenced from the junction-to-case at a case, temperature of 85  $^\circ\text{C}$ . Tj is a function of the voltage and the current applied. It can be calculated by:

Tjc = Tcase + Rth \* Vcc \* Icc

This corresponds to the typical biasing condition of +5V, 400 mA at an 85° C case temperature.

### **Product Marking**

The component will be marked with an "AH212-EG" designator with an alphanumeric lot code on the top surface of the package.

Tape and reel specifications for this part are located on the website in the "Application Notes" section.

### **ESD / MSL Information**

Caution! ESD sensitive device.

ESD Rating: Class 1B

Value: Passes ≥ 500V to <1000V

Test: Human Body Model (HBM)

Standard: JEDEC Standard JESD22-A114

ESD Rating: Class IV

Value: Passes ≥ 2000 V min.

Test: Charged Device Model (CDM)

Standard: JEDEC Standard JESD22-C101

MSL Rating: Level 2 at +260 °C convection reflow Standard: JEDEC Standard J-STD-020

## **Mounting Config. Notes**

- A heatsink underneath the area of the PCB for the mounted device is recommended for proper thermal operation. Damage to the device can occur without the use of one.

- Ground / thermal vias are critical for the proper performance of this device. Vias should use a .35mm (#80 / .0135") diameter drill and have a final plated thru diameter of .25 mm (.010").

- Add as much copper as possible to inner and outer layers near the part to ensure optimal thermal performance.

Mounting screws can be added near the part to fasten the board to a

- Mounting screws can be added near the part to fasten the board to a heatsink. Ensure that the ground / thermal via region contacts the heatsink.

- Do not put solder mask on the backside of the PC board in the region where the board contacts the heatsink.

RF trace width depends upon the PC board material and

- RF trace width depends upon the PC board material and construction.

- 7. Use 1 oz. Copper minimum.

- 8. All dimensions are in millimeters

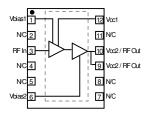

## **Functional Pin Layout**

| Function     | Pin No.           |

|--------------|-------------------|

| Vcc1         | 12                |

| Input        | 3                 |

| Output /Vcc2 | 9, 10             |

| Vbias1       | 1                 |

| Vbias2       | 6                 |

| GND          | Backside Paddle   |

| N/C or GND   | 2, 4, 5, 7, 8, 11 |

Specifications and information are subject to change without notice