Rev. 1 — 14 June 2024

Product data sheet

## 1 General description

The AFSC5G40E38 is a fully integrated Doherty power amplifier module designed for wireless infrastructure applications that demand high performance in the smallest footprint. Ideal for applications in massive MIMO systems, outdoor small cells and low power remote radio heads. The field–proven LDMOS power amplifiers are designed for TDD and FDD LTE systems.

## 2 Typical performance

Table 1. 3700-4000 MHz — Typical LTE Performance

Pout = 6.3 W Avg., VDD = 28 Vdc, 1 × 20 MHz LTE, Input Signal PAR = 8 dB @ 0.01% Probability on CCDF. (1)

| Carrier Center<br>Frequency | Gain<br>(dB) | ACPR<br>(dBc) | PAE<br>(%) |

|-----------------------------|--------------|---------------|------------|

| 3710 MHz                    | 26.1         | -27.2         | 38.3       |

| 3800 MHz                    | 26.6         | -26.7         | 39.5       |

| 3900 MHz                    | 27.5         | -25.7         | 39.3       |

| 3990 MHz                    | 28.5         | -23.9         | 37.6       |

<sup>1.</sup> All data measured with device soldered in NXP reference circuit.

### 3 Features and benefits

- Frequency: 3700–4000 MHz

- Advanced high performance in-package Doherty

- Fully matched (50 ohm input/output, DC blocked)

- · Designed for low complexity analog or digital linearization systems

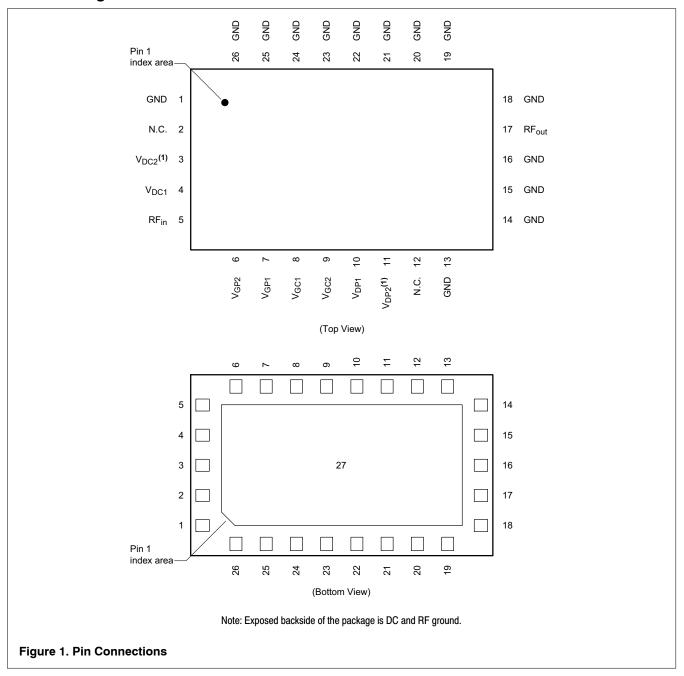

## 4 Pinning information

### 4.1 Pinning

1.  $V_{DC2}$  and  $V_{DP2}$  are DC coupled internal to the package and must be powered by a single DC power supply.

## 4.2 Functional pin description

### **Table 2. Functional Pin Description**

| Pin Number                                                | Pin Function      | Pin Description               |

|-----------------------------------------------------------|-------------------|-------------------------------|

| 1, 13, 14, 15, 16, 18, 19, 20, 21, 22, 23, 24, 25, 26, 27 | GND               | Ground                        |

| 2, 12                                                     | N.C.              | No Connection                 |

| 3                                                         | V <sub>DC2</sub>  | Carrier Drain Supply, Stage 2 |

| 4                                                         | V <sub>DC1</sub>  | Carrier Drain Supply, Stage 1 |

| 5                                                         | RF <sub>in</sub>  | RF Input                      |

| 6                                                         | V <sub>GP2</sub>  | Peaking Gate Supply, Stage 2  |

| 7                                                         | V <sub>GP1</sub>  | Peaking Gate Supply, Stage 1  |

| 8                                                         | V <sub>GC1</sub>  | Carrier Gate Supply, Stage 1  |

| 9                                                         | V <sub>GC2</sub>  | Carrier Gate Supply, Stage 2  |

| 10                                                        | V <sub>DP1</sub>  | Peaking Drain Supply, Stage 1 |

| 11                                                        | V <sub>DP2</sub>  | Peaking Drain Supply, Stage 2 |

| 17                                                        | RF <sub>out</sub> | RF Output                     |

## 5 Maximum ratings

### **Table 3. Maximum Ratings**

| Rating                                                                 | Symbol           | Value       | Unit |

|------------------------------------------------------------------------|------------------|-------------|------|

| Gate-Bias Voltage Range                                                | V <sub>G</sub>   | -0.5 to +10 | Vdc  |

| Operating Voltage Range                                                | $V_{DD}$         | 24 to 30    | Vdc  |

| Storage Temperature Range                                              | T <sub>stg</sub> | -65 to +150 | °C   |

| Case Operating Temperature                                             | T <sub>C</sub>   | 125         | °C   |

| Peak Input Power<br>(3950 MHz, Pulsed CW, 10 μsec(on), 10% Duty Cycle) | P <sub>in</sub>  | 25          | dBm  |

### 6 Lifetime

### Table 4. Lifetime

| Characteristic                                                     | Symbol | Value | Unit  |

|--------------------------------------------------------------------|--------|-------|-------|

| Mean Time to Failure<br>Case Temperature 125°C, 6.3 W Avg., 30 Vdc | MTTF   | > 10  | Years |

# 7 ESD protection characteristics

#### **Table 5. ESD Protection Characteristics**

| Test Methodology                      | Class |

|---------------------------------------|-------|

| Human Body Model (per JS-001-2017)    | 1A    |

| Charge Device Model (per JS-002-2014) | C2b   |

## 8 Moisture sensitivity level

### **Table 6. Moisture Sensitivity Level**

| Test Methodology                     | Rating | Package Peak Temperature | Unit |

|--------------------------------------|--------|--------------------------|------|

| Per JESD22-A113, IPC/JEDEC J-STD-020 | 3      | 260                      | °C   |

## 9 Electrical characteristics

### 9.1 DC characteristics

### **Table 7. DC Characteristics**

$(T_A = 25^{\circ}C \text{ unless otherwise noted})$

| Characteristic                                                                                                         | Symbol              | Тур      | Range | Unit     |

|------------------------------------------------------------------------------------------------------------------------|---------------------|----------|-------|----------|

| Carrier Stage 1 — On Characteristics                                                                                   |                     | •        |       |          |

| Gate Threshold Voltage (1) $(V_{DS} = 10 \text{ Vdc}, I_D = 1.6 \mu\text{Adc})$                                        | V <sub>GS(th)</sub> | 1.2      | ±0.4  | Vdc      |

| Gate Quiescent Voltage<br>(V <sub>DS</sub> = 28 Vdc, I <sub>DQ1A</sub> = 15 mAdc)                                      | V <sub>GS(Q)</sub>  | 1.9      | ±0.4  | Vdc      |

| Fixture Gate Quiescent Voltage<br>(V <sub>DD</sub> = 28 Vdc, I <sub>DQ1A</sub> = 15 mAdc, Measured in Functional Test) | V <sub>GG(Q)</sub>  | 4.8      | ±1.4  | Vdc      |

| Carrier Stage 2 — On Characteristics                                                                                   |                     |          |       |          |

| Gate Threshold Voltage (1) $(V_{DS} = 10 \text{ Vdc}, I_D = 14.4 \mu\text{Adc})$                                       | V <sub>GS(th)</sub> | 1.2      | ±0.4  | Vdc      |

| Gate Quiescent Voltage<br>(V <sub>DS</sub> = 28 Vdc, I <sub>DQ2A</sub> = 50 mAdc)                                      | V <sub>GS(Q)</sub>  | 1.8      | ±0.4  | Vdc      |

| Fixture Gate Quiescent Voltage<br>(V <sub>DD</sub> = 28 Vdc, I <sub>DQ2A</sub> = 50 mAdc, Measured in Functional Test) | $V_{GG(Q)}$         | 2.7      | ±1.2  | Vdc      |

| Peaking Stage 1 — On Characteristics <sup>(1)</sup>                                                                    | - 1                 | <u> </u> |       | <b>,</b> |

| Gate Threshold Voltage $(V_{DS} = 10 \text{ Vdc}, I_D = 2.0 \mu\text{Adc})$                                            | V <sub>GS(th)</sub> | 1.2      | ±0.4  | Vdc      |

| Gate Quiescent Voltage<br>(V <sub>DS</sub> = 28 Vdc, I <sub>DQ1A</sub> = 5.1 μAdc)                                     | V <sub>GS(Q)</sub>  | 1.2      | ±0.4  | Vdc      |

| Fixture Gate Quiescent Voltage (V <sub>DD</sub> = 28 Vdc, I <sub>DQ1A</sub> = 5.1 μAdc, Measured in Functional Test)   | V <sub>GG(Q)</sub>  | 1.2      | ±0.4  | Vdc      |

| Peaking Stage 2 — On Characteristics (1)                                                                               | <u> </u>            | •        |       | •        |

| Gate Threshold Voltage $(V_{DS} = 10 \text{ Vdc}, I_D = 27.2 \mu\text{Adc})$                                           | V <sub>GS(th)</sub> | 1.2      | ±0.4  | Vdc      |

| Gate Quiescent Voltage<br>(V <sub>DS</sub> = 28 Vdc, I <sub>DQ2A</sub> = 16.7 μAdc)                                    | V <sub>GS(Q)</sub>  | 1.2      | ±0.4  | Vdc      |

| Fixture Gate Quiescent Voltage (V <sub>DD</sub> = 28 Vdc, I <sub>DQ2A</sub> = 16.7 μAdc, Measured in Functional Test)  | V <sub>GG(Q)</sub>  | 1.2      | ±0.4  | Vdc      |

<sup>1.</sup> Each side of device measured separately.

### 9.2 Functional tests

#### Table 8. Functional Tests — 3800 MHz (1)

(In NXP Doherty Production ATE  $^{(2)}$  Test Fixture,  $T_A=25^{\circ}C$  unless otherwise noted, 50 ohm system)  $V_{DD}=28$  Vdc,  $I_{DQ1A}=15$  mA,  $I_{DQ2A}=50$  mA,  $V_{GS1B}=(V_t-0.21)$  Vdc,  $V_{GS2B}=(V_t-0.20)$  Vdc,  $P_{out}=6.3$  W Avg., 1-tone CW, f=3800 MHz.

| Characteristic                                                          | Symbol     | Min  | Тур  | Max | Unit |

|-------------------------------------------------------------------------|------------|------|------|-----|------|

| Gain                                                                    | G          | 24.8 | 26.7 | _   | dB   |

| Drain Efficiency                                                        | $\eta_{D}$ | 34.5 | 43.5 | _   | %    |

| P <sub>out</sub> @ 3 dB Compression Point<br>(Pulsed CW, 5% Duty Cycle) | P3dB       | 43.6 | 44.4 | _   | dBm  |

### Table 9. Functional Tests — 4000 MHz (1)

(In NXP Doherty Production ATE  $^{(2)}$  Test Fixture,  $T_A$  = 25°C unless otherwise noted, 50 ohm system)  $V_{DD}$  = 28 Vdc,  $I_{DQ1A}$  = 15 mA,  $I_{DQ2A}$  = 50 mA,  $V_{GS1B}$  = ( $V_t$  - 0.21) Vdc,  $V_{GS2B}$  = ( $V_t$  - 0.20) Vdc,  $P_{out}$  = 6.3 W Avg., 1-tone CW, f = 4000 MHz.

| Characteristic                                                          | Symbol     | Min  | Тур  | Max | Unit |

|-------------------------------------------------------------------------|------------|------|------|-----|------|

| Gain                                                                    | G          | 27.1 | 28.8 | _   | dB   |

| Drain Efficiency                                                        | $\eta_{D}$ | 33.0 | 38.0 | _   | %    |

| P <sub>out</sub> @ 3 dB Compression Point<br>(Pulsed CW, 5% Duty Cycle) | P3dB       | 42.9 | 43.7 | _   | dBm  |

### 9.3 Wideband ruggedness

#### Table 10. Wideband Ruggedness (3)

(In NXP Doherty Power Amplifier Module Reference Circuit,  $T_A = 25^{\circ}$ C unless otherwise noted, 50 ohm system)  $I_{DQ1A} = 15$  mA,  $I_{DQ2A} = 50$  mA,  $V_{GSP1} = 1.3$  Vdc,  $V_{GSP2} = 1.3$  Vdc, f = 3900 MHz, Additive White Gaussian Noise (AWGN) with 10 dB PAR

| Characteristic                                                                         | Test Results          |

|----------------------------------------------------------------------------------------|-----------------------|

| ISBW of 400 MHz at 30 Vdc, 3 dB Input Overdrive from 6.3 W Avg. Modulated Output Power | No Device Degradation |

- 1. Part input and output matched to 50 ohms.

- 2. ATE is a socketed test environment.

- 3. All data measured in fixture with device soldered in NXP reference circuit.

### 9.4 Typical performance

### Table 11. Typical Performance (1)

In NXP Doherty Power Amplifier Module Reference Circuit,  $T_A = 25^{\circ}\text{C}$  unless otherwise noted, 50 ohm system)  $V_{DD} = 28 \text{ Vdc}$ ,  $I_{DQ1A} = 15 \text{ mA}$ ,  $I_{DQ2A} = 50 \text{ mA}$ ,  $V_{GSP1} = 1.3 \text{ Vdc}$ ,  $V_{GSP2} = 1.3 \text{ Vdc}$ ,  $P_{Out} = 6.3 \text{ W Avg.}$ , 3900 MHz

| Characteristic                                                                                                                                                                | Symbol             | Min    | Тур        | Max    | Unit  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|--------|------------|--------|-------|

| VBW Resonance Point, 2-tone, 1 MHz Tone Spacing (IMD Third Order Intermodulation Inflection Point)                                                                            | VBW <sub>res</sub> | _      | 241        | _      | MHz   |

| Quiescent Current Accuracy over Temperature (2) with 2.2 k $\Omega$ Gate Feed Resistors (–40 to 105°C) Stage 1 with 2.2 k $\Omega$ Gate Feed Resistors (–40 to 105°C) Stage 2 | $\Delta I_{QT}$    | _<br>_ | 1.0<br>6.0 | _<br>_ | %     |

| 1-carrier 20 MHz LTE, 8 dB Input Signal PAR                                                                                                                                   |                    |        |            |        |       |

| Gain                                                                                                                                                                          | G                  | _      | 27.5       | _      | dB    |

| Power Added Efficiency                                                                                                                                                        | PAE                | =      | 39.3       | =      | %     |

| Adjacent Channel Power Ratio                                                                                                                                                  | ACPR               | =      | -25.7      | =      | dBc   |

| Adjacent Channel Power Ratio                                                                                                                                                  | ALT1               | =      | -38.8      | =      | dBc   |

| Adjacent Channel Power Ratio                                                                                                                                                  | ALT2               | =      | -44.8      | =      | dBc   |

| Gain Flatness (3)                                                                                                                                                             | G <sub>F</sub>     | =      | 2.4        | =      | dB    |

| Fast CW, 27 ms Sweep                                                                                                                                                          |                    |        |            |        |       |

| Pout @ 3 dB Compression Point                                                                                                                                                 | P3dB               | _      | 45.5       | _      | dBm   |

| AM/PM @ P3dB                                                                                                                                                                  | Φ                  | _      | -46        | _      | ٥     |

| Gain Variation @ Avg. Power over Temperature (-40°C to +105°C)                                                                                                                | ΔG                 | _      | 0.025      | _      | dB/°C |

| P3dB Variation over Temperature (-40°C to +105°C)                                                                                                                             | ΔP3dB              | _      | 0.014      | _      | dB/°C |

## 10 Ordering information

### **Table 12. Ordering Information**

| Device        | Tape and Reel Information                               | Package             |

|---------------|---------------------------------------------------------|---------------------|

| AFSC5G40E38T2 | T2 Suffix = 2,000 Units, 24 mm Tape Width, 13-inch Reel | 10 mm × 6 mm Module |

- 1. All data measured in fixture with device soldered in NXP reference circuit.

- 2. Refer to AN1977, Quiescent Current Thermal Tracking Circuit in the RF Integrated Circuit Family, and to AN1987, Quiescent Current Control for the RF Integrated Circuit Device Family. Go to http://www.nxp.com/RF and search for AN1977 or AN1987.

- 3. Gain flatness =  $Max(G(f_{Low} \text{ to } f_{High})) Min(G(f_{Low} \text{ to } f_{High}))$

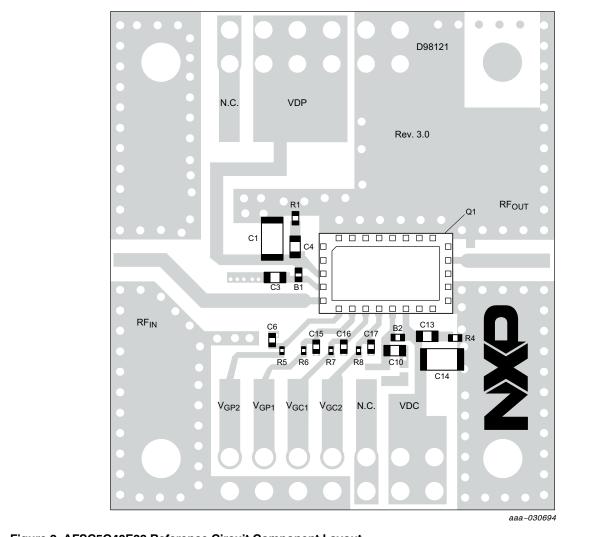

## 11 Component layout and parts list

## 11.1 Component layout

Figure 2. AFSC5G40E38 Reference Circuit Component Layout

### 11.2 Component designations and values

Table 13. AFSC5G40E38 Reference Circuit Component Designations and Values

| Part              | Description                                                 | Part Number       | Manufacturer |

|-------------------|-------------------------------------------------------------|-------------------|--------------|

| B1, B2            | 30 $\Omega$ Ferrite Bead                                    | BLM15PD300SN1     | Murata       |

| C1, C14           | 10 μF Chip Capacitor                                        | CL31A106KBHNNNE   | Samsung      |

| C3, C4, C10, C13  | 1 μF Chip Capacitor                                         | 06035D105KAT2A    | AVX          |

| C6, C15, C16, C17 | 0.1 μF Chip Capacitor                                       | GRM155R61H104KE14 | Murata       |

| Q1                | Power Amplifier Module                                      | AFSC5G40E38       | NXP          |

| R1, R4            | 5.1 Ω, 1/10 W Chip Resistor                                 | ERJ-2GEJ5R1X      | Panasonic    |

| R5, R6, R7, R8    | 2.2 kΩ, 1/20 W Chip Resistor                                | ERJ-1GNJ222C      | Panasonic    |

| PCB               | Rogers RO4350B, 0.020", $\varepsilon_{\rm r}$ = 3.67 D98121 |                   | MTL          |

Note: Component numbers C2, C5, C7, C8, C9, C11, C12, R2 and R3 are intentionally omitted.

AFSC5G40E38

Airfast Power Amplifier Module

## 12 Product marking

Figure 3. Product Marking

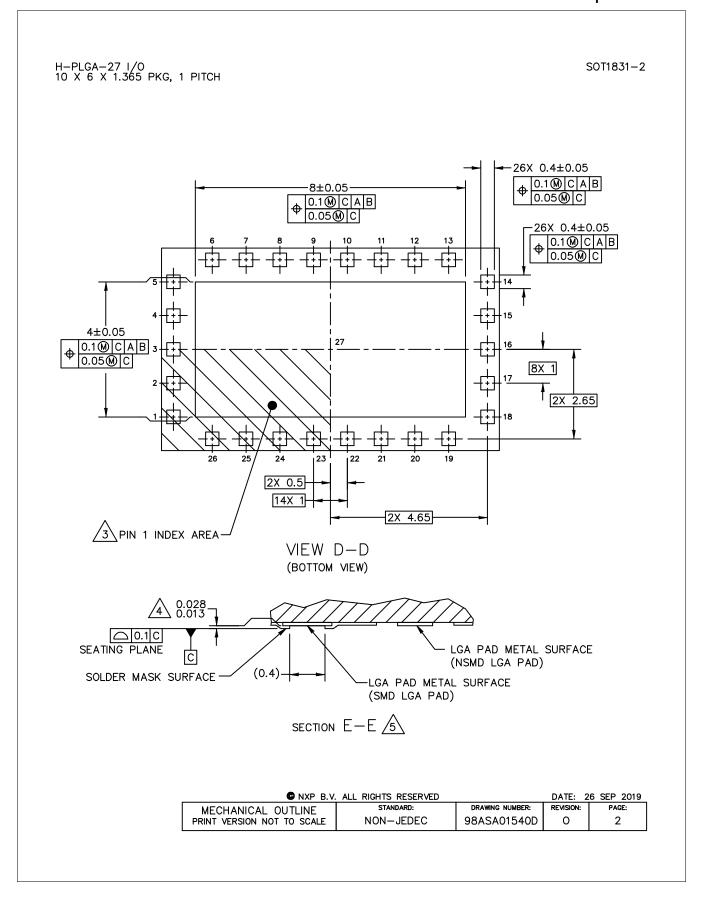

## 13 Package information

Product data sheet

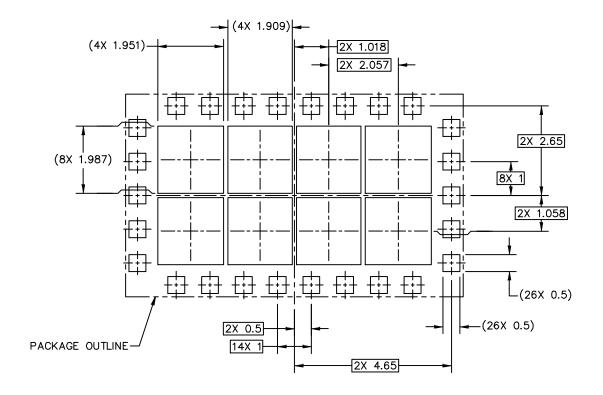

H-PLGA-27 I/O 10 X 6 X 1.365 PKG, 1 PITCH

SOT1831-2

### PCB DESIGN GUIDELINES - SOLDER MASK OPENING PATTERN

THIS SHEET SERVES ONLY AS A GUIDELINE TO HELP DEVELOP A USER SPECIFIC SOLUTION. DEVELOPMENT EFFORT WILL STILL BE REQUIRED BY END USERS TO OPTIMIZE PCB MOUNTING PROCESSES AND BOARD DESIGN IN ORDER TO MEET INDIVIDUAL/SPECIFIC REQUIREMENTS.

| ● NXP B.V. ALL RIGHTS RESERVED DATE: 26 SEP 2019 |           |                 |           |       |

|--------------------------------------------------|-----------|-----------------|-----------|-------|

| MECHANICAL OUTLINE                               | STANDARD: | DRAWING NUMBER: | REVISION: | PAGE: |

| PRINT VERSION NOT TO SCALE                       | NON-JEDEC | 98ASA01540D     | 0         | 3     |

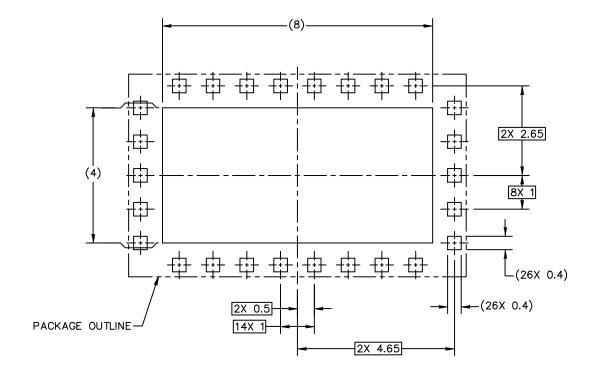

H-PLGA-27 I/O 10 X 6 X 1.365 PKG, 1 PITCH

SOT1831-2

## PCB DESIGN GUIDELINES - I/O PADS AND SOLDERABLE AREAS

THIS SHEET SERVES ONLY AS A GUIDELINE TO HELP DEVELOP A USER SPECIFIC SOLUTION. DEVELOPMENT EFFORT WILL STILL BE REQUIRED BY END USERS TO OPTIMIZE PCB MOUNTING PROCESSES AND BOARD DESIGN IN ORDER TO MEET INDIVIDUAL/SPECIFIC REQUIREMENTS.

| ● NXP B.V. ALL RIGHTS RESERVED DATE: 26 SEP 2019 |           |                 |           |       |

|--------------------------------------------------|-----------|-----------------|-----------|-------|

| MECHANICAL OUTLINE                               | STANDARD: | DRAWING NUMBER: | REVISION: | PAGE: |

| PRINT VERSION NOT TO SCALE                       | NON-JEDEC | 98ASA01540D     | 0         | 4     |

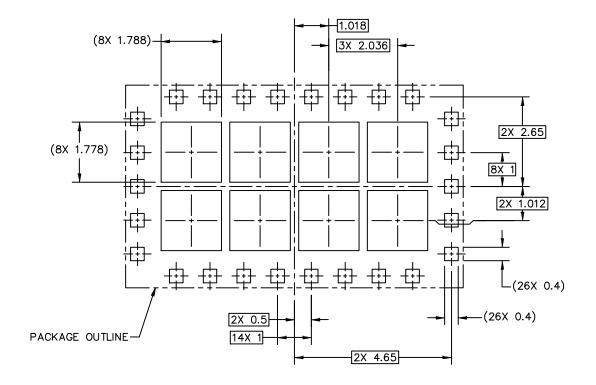

H-PLGA-27 I/O 10 X 6 X 1.365 PKG, 1 PITCH

SOT1831-2

### RECOMMENDED STENCIL THICKNESS 0.125

### PCB DESIGN GUIDELINES - SOLDER PASTE STENCIL

THIS SHEET SERVES ONLY AS A GUIDELINE TO HELP DEVELOP A USER SPECIFIC SOLUTION. DEVELOPMENT EFFORT WILL STILL BE REQUIRED BY END USERS TO OPTIMIZE PCB MOUNTING PROCESSES AND BOARD DESIGN IN ORDER TO MEET INDIVIDUAL/SPECIFIC REQUIREMENTS.

| NXP B.V. ALL RIGHTS RESERVED DATE: 26 SEP 2019 |           |                 |           |       |

|------------------------------------------------|-----------|-----------------|-----------|-------|

| MECHANICAL OUTLINE                             | STANDARD: | DRAWING NUMBER: | REVISION: | PAGE: |

| PRINT VERSION NOT TO SCALE                     | NON-JEDEC | 98ASA01540D     | 0         | 5     |

# AFSC5G40E38

### **Airfast Power Amplifier Module**

H-PLGA-27 I/O 10 X 6 X 1.365 PKG, 1 PITCH

SOT1831-2

### NOTES:

- 1. ALL DIMENSIONS IN MILLIMETERS.

- 2. DIMENSIONING AND TOLERANCING PER ASME Y14.5M-1994.

<u>/3.\</u>

PIN 1 FEATURE SHAPE, SIZE AND LOCATION MAY VARY.

4.

DIMENSION APPLIES TO ALL LEADS AND FLAG.

5.

THE BOTTOM VIEW SHOWS THE SOLDERABLE AREA OF THE PADS. THE CENTER PAD (PIN 27) IS SOLDER MASK DEFINED. SOME PERIPHERAL PADS ARE SOLDER MASK DEFINED (SMD) AND OTHERS ARE NON-SOLDERMASK DEFINED (NSMD).

© NXP B.V. ALL RIGHTS RESERVED DATE: 26 SEP 2019

| MECHANICAL OUTLINE         | STANDARD: | DRAWING NUMBER: | REVISION: | PAGE: |

|----------------------------|-----------|-----------------|-----------|-------|

| PRINT VERSION NOT TO SCALE | NON-JEDEC | 98ASA01540D     | 0         | 6     |

### 14 Product documentation and tools

Refer to the following resources to aid your design process.

### **Application Notes**

- AN1977: Quiescent Current Thermal Tracking Circuit in the RF Integrated Circuit Family

- AN1987: Quiescent Current Control for the RF Integrated Circuit Device Family

### **Development Tools**

• Printed Circuit Boards

## 15 Failure analysis

At this time, because of the physical characteristics of the part, failure analysis is limited to electrical signature analysis. In cases where NXP is contractually obligated to perform failure analysis (FA) services, full FA may be performed by third party vendors with moderate success. For updates contact your local NXP Sales Office.

### 16 Revision history

The following table summarizes revisions to this document.

### **Table 14. Revision History**

| Document ID        | Release Date      | Description                                                                                        |

|--------------------|-------------------|----------------------------------------------------------------------------------------------------|

| AFSC5G40E38 Rev. 1 | 14 June 2024      | Tables 8 and 9, Functional Tests, 3800 MHz and 4000 MHz: updated output power test condition, p. 6 |

| AFSC5G40E38 Rev. 0 | 24 September 2020 | Initial release of product data sheet                                                              |

### Legal information

### Data sheet status

| Document status [1][2]         | Product status [3] | Definition                                                                            |

|--------------------------------|--------------------|---------------------------------------------------------------------------------------|

| Objective [short] data sheet   | Development        | This document contains data from the objective specification for product development. |

| Preliminary [short] data sheet | Qualification      | This document contains data from the preliminary specification.                       |

| Product [short] data sheet     | Production         | This document contains the product specification.                                     |

- Please consult the most recently issued document before initiating or completing a design.

- The term 'short data sheet' is explained in section "Definitions".

- The product status of device(s) described in this document may have changed since this document was published and may differ in case of multiple devices. The latest product status information is available on the Internet at URL https://www.nxp.com. [3]

### **Definitions**

Draft — A draft status on a document indicates that the content is still under internal review and subject to formal approval, which may result in modifications or additions. NXP Semiconductors does not give any representations or warranties as to the accuracy or completeness of information included in a draft version of a document and shall have no liability for the consequences of use of such information.

Short data sheet — A short data sheet is an extract from a full data sheet with the same product type number(s) and title. A short data sheet is intended for guick reference only and should not be relied upon to contain detailed and full information. For detailed and full information see the relevant full data sheet, which is available on request via the local NXP Semiconductors sales office. In case of any inconsistency or conflict with the short data sheet, the full data sheet shall prevail.

**Product specification** — The information and data provided in a Product data sheet shall define the specification of the product as agreed between NXP Semiconductors and its customer, unless NXP Semiconductors and customer have explicitly agreed otherwise in writing. In no event however, shall an agreement be valid in which the NXP Semiconductors product is deemed to offer functions and qualities beyond those described in the Product data sheet.

### **Disclaimers**

Limited warranty and liability - Information in this document is believed to be accurate and reliable. However, NXP Semiconductors does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information. NXP Semiconductors takes no responsibility for the content in this document if provided by an information source outside of NXP Semiconductors.

In no event shall NXP Semiconductors be liable for any indirect, incidental, punitive, special or consequential damages (including - without limitation lost profits, lost savings, business interruption, costs related to the removal or replacement of any products or rework charges) whether or not such damages are based on tort (including negligence), warranty, breach of contract or any other legal theory.

Notwithstanding any damages that customer might incur for any reason whatsoever, NXP Semiconductors' aggregate and cumulative liability towards customer for the products described herein shall be limited in accordance with the Terms and conditions of commercial sale of NXP Semiconductors.

Right to make changes - NXP Semiconductors reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.

Suitability for use — NXP Semiconductors products are not designed, authorized or warranted to be suitable for use in life support, life-critical or safety-critical systems or equipment, nor in applications where failure or malfunction of an NXP Semiconductors product can reasonably be expected to result in personal injury, death or severe property or environmental damage. NXP Semiconductors and its suppliers accept no liability for inclusion and/or use of NXP Semiconductors products in such equipment or applications and therefore such inclusion and/or use is at the customer's own risk.

Applications — Applications that are described herein for any of these products are for illustrative purposes only. NXP Semiconductors makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

Customers are responsible for the design and operation of their applications and products using NXP Semiconductors products, and NXP Semiconductors accepts no liability for any assistance with applications or customer product design. It is customer's sole responsibility to determine whether the NXP Semiconductors product is suitable and fit for the customer's applications and products planned, as well as for the planned application and use of customer's third party customer(s). Customers should provide appropriate design and operating safeguards to minimize the risks associated with their applications and products.

NXP Semiconductors does not accept any liability related to any default, damage, costs or problem which is based on any weakness or default in the customer's applications or products, or the application or use by customer's third party customer(s). Customer is responsible for doing all necessary testing for the customer's applications and products using NXP Semiconductors products in order to avoid a default of the applications and the products or of the application or use by customer's third party customer(s). NXP does not accept any liability in this respect.

Limiting values — Stress above one or more limiting values (as defined in the Absolute Maximum Ratings System of IEC 60134) will cause permanent damage to the device. Limiting values are stress ratings only and (proper) operation of the device at these or any other conditions above those given in the Recommended operating conditions section (if present) or the Characteristics sections of this document is not warranted. Constant or repeated exposure to limiting values will permanently and irreversibly affect the quality and reliability of the device.

Terms and conditions of commercial sale — NXP Semiconductors products are sold subject to the general terms and conditions of commercial sale, as published at https://www.nxp.com/profile/terms, unless otherwise agreed in a valid written individual agreement. In case an individual agreement is concluded only the terms and conditions of the respective agreement shall apply. NXP Semiconductors hereby expressly objects to applying the customer's general terms and conditions with regard to the purchase of NXP Semiconductors products by customer.

No offer to sell or license — Nothing in this document may be interpreted or construed as an offer to sell products that is open for acceptance or the grant, conveyance or implication of any license under any copyrights, patents or other industrial or intellectual property rights.

Export control — This document as well as the item(s) described herein may be subject to export control regulations. Export might require a prior authorization from competent authorities

Suitability for use in non-automotive qualified products — Unless this document expressly states that this specific NXP Semiconductors product is automotive qualified, the product is not suitable for automotive use. It is neither qualified nor tested in accordance with automotive testing or application requirements. NXP Semiconductors accepts no liability for inclusion and/or use of non-automotive qualified products in automotive equipment or applications.

# AFSC5G40E38

### **Airfast Power Amplifier Module**

In the event that customer uses the product for design–in and use in automotive applications to automotive specifications and standards, customer (a) shall use the product without NXP Semiconductors' warranty of the product for such automotive applications, use and specifications, and (b) whenever customer uses the product for automotive applications beyond NXP Semiconductors' specifications such use shall be solely at customer's own risk, and (c) customer fully indemnifies NXP Semiconductors for any liability, damages or failed product claims resulting from customer design and use of the product for automotive applications beyond NXP Semiconductors' standard warranty and NXP Semiconductors' product specifications.

**Translations** — A non–English (translated) version of a document, including the legal information in that document, is for reference only. The English version shall prevail in case of any discrepancy between the translated and English versions.

Security — Customer understands that all NXP products may be subject to unidentified vulnerabilities or may support established security standards or specifications with known limitations. Customer is responsible for the design and operation of its applications and products throughout their lifecycles to reduce the effect of these vulnerabilities on customer's applications and products. Customer's responsibility also extends to other open and/or proprietary technologies supported by NXP products for use in customer's applications. NXP accepts no liability for any vulnerability. Customer should regularly check security updates from NXP and follow up appropriately.

Customer shall select products with security features that best meet rules, regulations, and standards of the intended application and make the ultimate design decisions regarding its products and is solely responsible for compliance with all legal, regulatory, and security related requirements concerning its products, regardless of any information or support that may be provided by NXP.

NXP has a Product Security Incident Response Team (PSIRT) (reachable at PSIRT@nxp.com) that manages the investigation, reporting, and solution release to security vulnerabilities of NXP products.

$\ensuremath{\mathsf{NXP}}\xspace\,\ensuremath{\mathsf{B.V.}}\xspace - \ensuremath{\mathsf{NXP}}\xspace\,\ensuremath{\mathsf{B.V.}}\xspace$  is not an operating company and it does not distribute or sell products.

#### **Trademarks**

Notice: All referenced brands, product names, service names, and trademarks are the property of their respective owners.

NXP — wordmark and logo are trademarks of NXP B.V.

Airfast — is a trademark of NXP B.V.

Freescale — is a trademark of NXP B.V.

Please be aware that important notices concerning this document and the product(s) described herein, have been included in section 'Legal information'.