# 8-Channel Variable-Gain Amplifier (VGA) With Octal High-Speed ADC

Check for Samples: AFE5801

#### **FEATURES**

- Eight Variable-Gain Amplifiers (VGA)

- Eight Differential Buffered Inputs With 2Vpp Maximum Swing

- 5.5nV/√Hz VCA Input Noise (31dB Gain)

- Variable Gain, –5dB to 31dB With 0.125dB or 1dB Steps

- Digital Gain Control

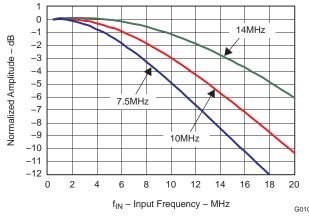

- Third-Order Antialiasing Filter With Programmable Cutoff Frequency (7.5, 10, or 14MHz)

- Clamping

- Analog-to-Digital Converter (ADC)

- Octal Channel, 12Bit, 65MSPS

- Internal and External Reference Support

- No External Decoupling Required for References

- Serial LVDS Outputs

- 1.8V and 3.3V Supplies

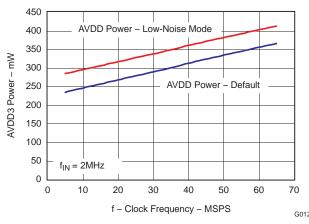

- 50mW Total Power per Channel at 30MSPS

- 58mW Total Power per Channel at 50MSPS

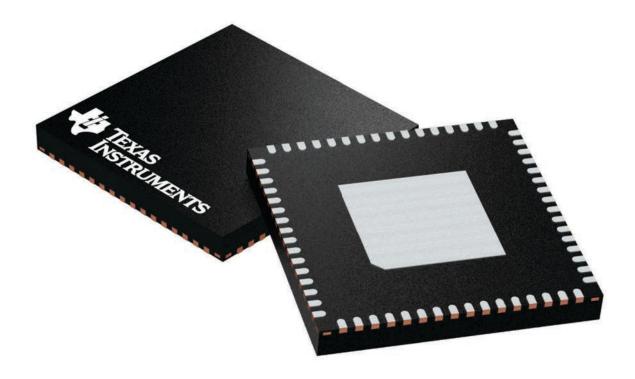

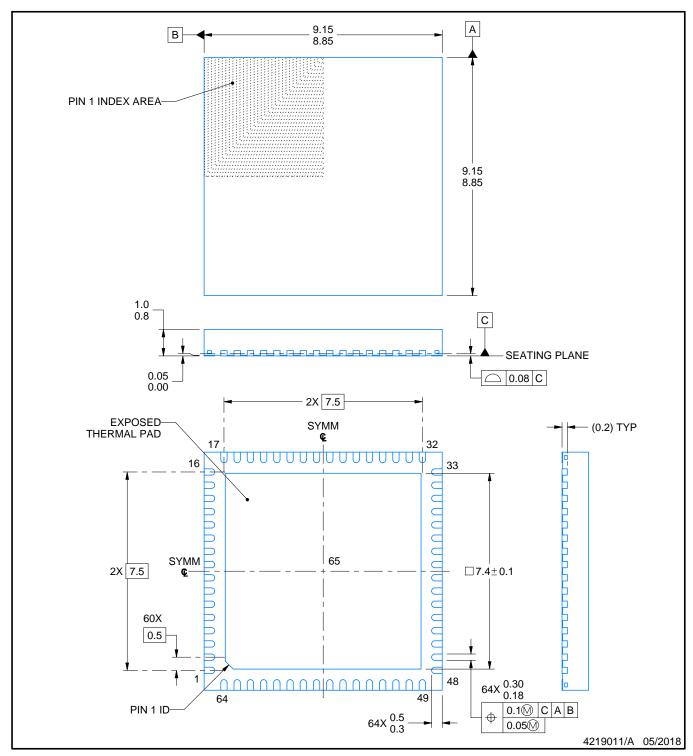

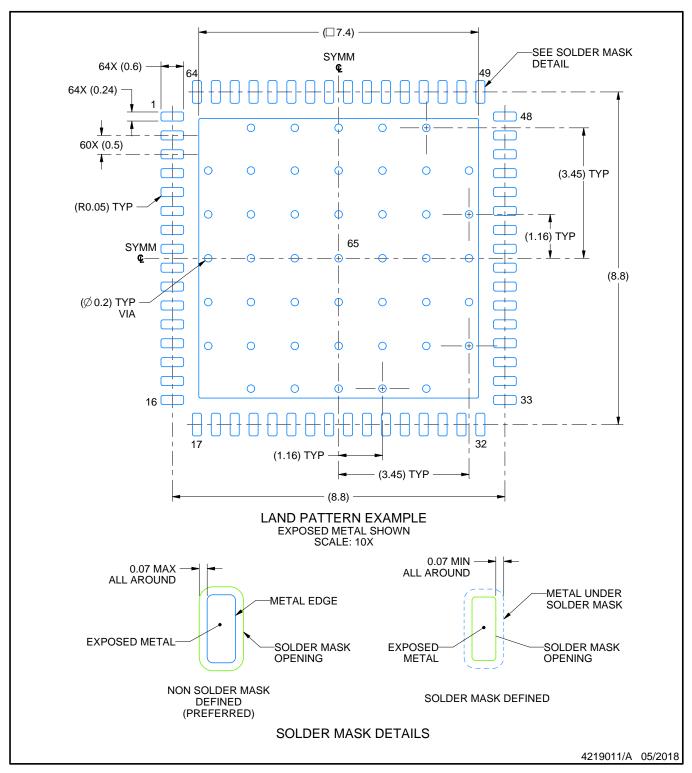

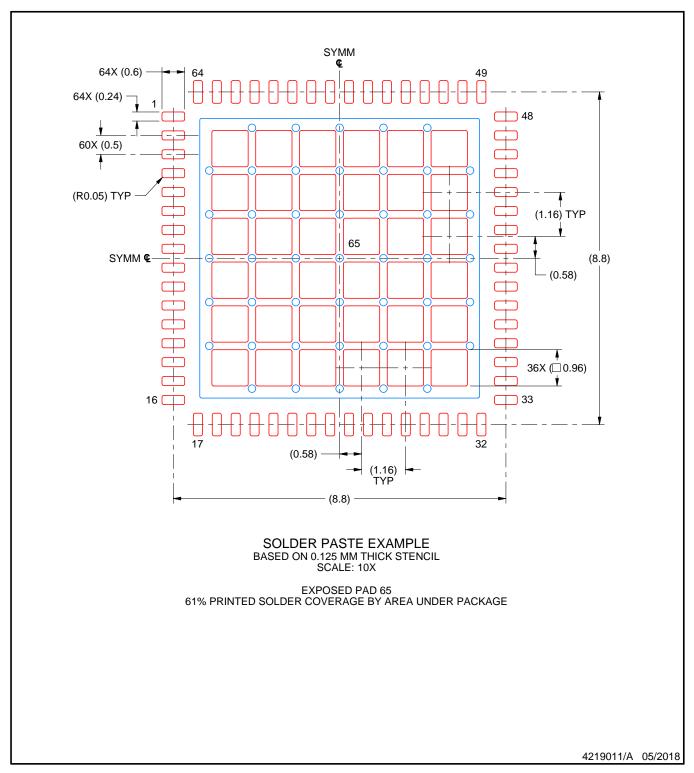

- 64QFN Package (9mm × 9mm)

### **APPLICATIONS**

· Imaging: Ultrasound, PET

#### RELATED DEVICES

AFE5851: 16-Channel VGA + ADC, 32.5MSPS/Channel

### **DESCRIPTION**

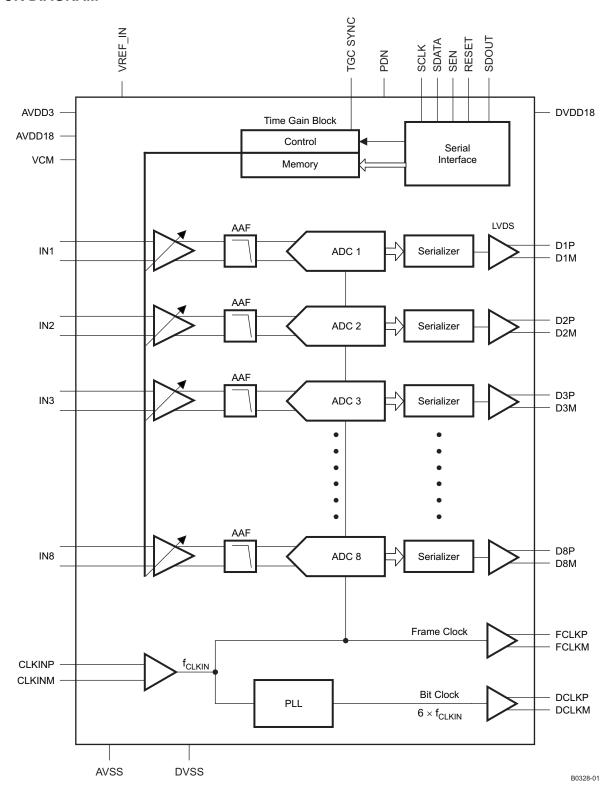

The AFE5801 is an analog front end, targeting applications where the power and level of integration are critical. The device contains eight variable-gain amplifiers (VGA), each followed by a high-speed (up to 65MSPS) ADC, for a total of eight ADCs per device.

Each of the eight differential inputs is buffered, accepts up to 2Vpp maximum input swing, and is followed by a VGA with a gain range from -5dB to 31dB. The VGA gain is digitally controlled, and the gain curves versus time can be stored in memory integrated within the device using the serial interface.

A selectable clamping and antialias low-pass filter (with 3dB attenuation at 7.5, 10, or 14MHz) is also integrated between VGA and ADC, for every channel.

The VGA/antialias filter outputs are differential (limited to 2Vpp) and drive the onboard 12bit, 65MSPS ADC. The ADC also scales down its power consumption should a lower sampling rate be selected. The ADC outputs are serialized in LVDS streams, which further minimizes power and board area.

The AFE5801 is available in a 64-pin QFN package (9mm  $\times$  9mm) and is specified over the full industrial temperature range ( $-40^{\circ}$ C to 85°C).

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

#### **BLOCK DIAGRAM**

### **PINOUT**

### **TERMINAL FUNCTIONS**

| Name           | NUMBER                     | DESCRIPTION                                                                                               |

|----------------|----------------------------|-----------------------------------------------------------------------------------------------------------|

| AVSS           | 20, 23, 61, 63             | Analog ground                                                                                             |

| AVDD18         | 19, 24, 62                 | 1.8V analog supply voltage                                                                                |

| AVDD3          | 18                         | 3.3V analog supply voltage                                                                                |

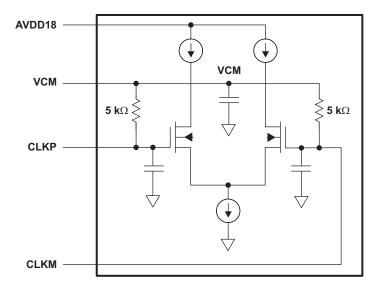

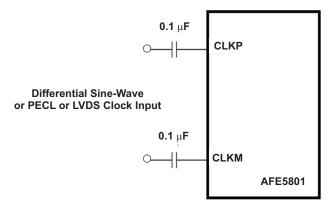

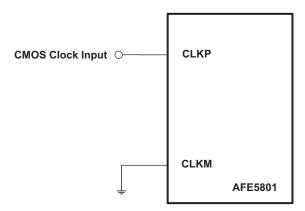

| CLKINP, CLKINM | 21, 22                     | Differential clock input pins. Single-ended clock is also supported. See the <i>Clock Inputs</i> section. |

| D1P/M-D8P/M    | 50–43, 38–31               | LVDS outputs for channels 1 to 8                                                                          |

| DCLKM, DCLKP   | 41, 42                     | LVDS bit clock output                                                                                     |

| DVSS           | 29, 52                     | Digital ground                                                                                            |

| DVDD18         | 28 <sup>(1)</sup> , 30, 51 | 1.8V LVDS buffer supply voltage                                                                           |

| FCLKM, FCLKP   | 39, 40                     | LVDS frame clock output                                                                                   |

| IN1P/M-IN8P/M  | 1–16                       | Differential analog input pins for channels 1 to 8                                                        |

| NC             | 26, 27, 60                 | Do not connect                                                                                            |

| PDN            | 59                         | Global power-down control input (active-high). 100kΩ pulldown resistor                                    |

| RESET          | 57                         | Hardware reset pin (active-high). 100kΩ pulldown resistor                                                 |

| SCLK           | 56                         | Serial interface clock input. 100kΩ pulldown resistor                                                     |

| SDATA          | 55                         | Serial interface data input. 100kΩ pulldown resistor                                                      |

| SDOUT          | 53                         | Serial interface data readout                                                                             |

| SEN            | 54                         | Serial interface enable. 100kΩ pullup resistor                                                            |

| SYNC           | 58                         | TGC/VGA synchronization signal input. 100kΩ pulldown resistor                                             |

| VCM            | 17, 64                     | Common-mode output pins for possible bias of the analog input signals                                     |

| VREF_IN        | 25                         | Reference input in the external reference mode                                                            |

| Thermal pad    | Bottom of package          | Connect to AVSS                                                                                           |

(1) Pin 28 can be connected to the 1.8V or 3.3V supply, whichever is easier for user. It does not affect the performance.

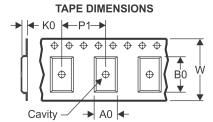

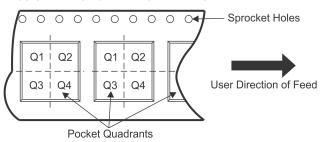

### PACKAGING/ORDERING INFORMATION(1)

| PRODUCT | PACKAGE-LEAD          | PACKAGE<br>DESIGNATOR | SPECIFIED<br>TEMPERATURE<br>RANGE | PACKAGE<br>MARKING | ORDERING<br>NUMBER | TRANSPORT<br>MEDIA,<br>QUANTITY |

|---------|-----------------------|-----------------------|-----------------------------------|--------------------|--------------------|---------------------------------|

| AFE5801 | QFN-64 <sup>(2)</sup> | RGC                   | -40°C to 85°C                     | AFE5801            | AFE5801IRGCT       | Tape/reel, 250                  |

| AFE5801 | QFN-64 <sup>(2)</sup> | RGC                   | -40°C to 85°C                     | AFE5801            | AFE5801IRGCR       | Tape/reel, 2000                 |

- (1) For the most-current package and ordering information, see the Package Option Addendum at the end of this document, or see the TI Web site at www.ti.com.

- (2) For the thermal pad size on the package, see the mechanical drawings at the end of this document.

# **ABSOLUTE MAXIMUM RATINGS**(1)

over operating free-air temperature range (unless otherwise noted)

|                  |                                                                  | VALUE                             | UNIT |

|------------------|------------------------------------------------------------------|-----------------------------------|------|

|                  | AVDD3 to AVSS                                                    | -0.3 to 3.8                       | V    |

|                  | AVDD18 to AVSS                                                   | -0.3 to 2.2                       | V    |

|                  | DVDD18 to DVSS                                                   | -0.3 to 2.2                       | V    |

|                  | Voltage between AVSS and DVSS                                    | -0.3 to 0.3                       | V    |

|                  | Analog input pins (IN <sub>i</sub> P, IN <sub>i</sub> M) to AVSS | -0.3V to MIN (3.6V, AVDD3 + 0.3V) | V    |

|                  | VREF_IN to AVSS                                                  | -0.3 to 2.2                       | V    |

|                  | V <sub>CLKP</sub> , V <sub>CLKM</sub> to AVSS                    | -0.3 to 2.2                       | V    |

|                  | Digital control pins to DVSS: PDN, RESET, SCLK, SDATA, SEN, SYNC | -0.3 to 3.6                       | V    |

| $T_{J}$          | Maximum operating junction temperature                           | 125                               | °C   |

| T <sub>stg</sub> | Storage temperature range                                        | -60 to 150                        | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

### THERMAL CHARACTERISTICS

| PARAMETER         | TEST CONDITIONS                                                                                                                    | TYP   | UNIT |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------|-------|------|

| $\theta_{\sf JA}$ | 0 LFM air flow                                                                                                                     | 23.17 | °C/W |

| $\theta_{\sf JC}$ | 2-oz. (0.071-mm thick) copper trace and pad soldered directly to a JEDEC-standard four-layer 3-in. x 3-in. (7.62-cm x7.62-cm) PCB. | 22.1  | °C/W |

#### RECOMMENDED OPERATING CONDITIONS

|                                      |                                    | MIN       | TYP | MAX       | UNIT |

|--------------------------------------|------------------------------------|-----------|-----|-----------|------|

| T <sub>A</sub>                       | Ambient temperature                | -40       |     | 85        | °C   |

| SUPPLIES                             |                                    | •         |     |           |      |

| AVDD3                                | Analog supply voltage (VGA)        | 3         | 3.3 | 3.6       | V    |

| AVDD18                               | Analog supply voltage (ADC)        | 1.7       | 1.8 | 1.9       | V    |

| DVDD18                               | Digital supply voltage (ADC, LVDS) | 1.7       | 1.8 | 1.9       | V    |

| ANALOG IN                            | PUTS                               | •         |     |           |      |

| IN <sub>i</sub> P, IN <sub>i</sub> M | Input voltage range to AVSS        | VCM - 0.5 |     | VCM + 0.5 | V    |

|                                      | VREF_IN in external reference mode | 1.35      | 1.4 | 1.45      | V    |

|                                      | VCM load                           |           | 3   |           | mA   |

**RECOMMENDED OPERATING CONDITIONS (continued)**

|                    |                                                                       | MIN           | TYP | MAX           | UNIT |

|--------------------|-----------------------------------------------------------------------|---------------|-----|---------------|------|

| CLOCK INP          | UT                                                                    |               |     |               | •    |

| f <sub>CLKIN</sub> | Input clock frequency                                                 | 5             |     | 65            | MSPS |

|                    | Input clock duty cycle                                                | 40%           | 50% | 60%           |      |

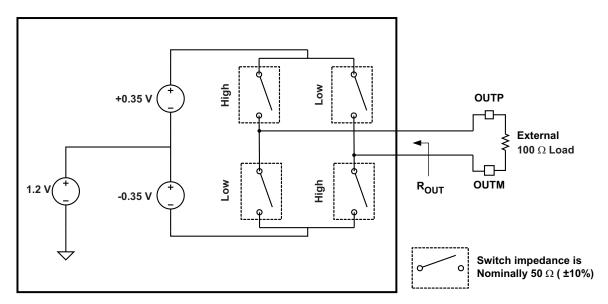

|                    | Sine wave, ac-coupled                                                 | 0.5           |     |               | Vpp  |

| $V_{CLKP-CLKM}$    | LVPECL, ac-coupled                                                    |               | 1.6 |               | Vpp  |

|                    | LVDS, ac-coupled                                                      | 0.25          | 0.7 |               | Vpp  |

| $V_{CLKP}$         | LVCMOS, single-ended, V <sub>CLKM</sub> to AVSS                       |               | 1.8 |               | Vpp  |

| $V_{IH}$           | High-level input voltage                                              | 0.75 × AVDD18 |     |               | V    |

| $V_{IL}$           | Low-level input voltage                                               |               |     | 0.25 × AVDD18 | V    |

| DIGITAL OU         | TPUT                                                                  | •             |     |               | ,    |

| C <sub>LOAD</sub>  | External load capacitance from each output pin to DVSS                |               | 5   |               | pF   |

| R <sub>LOAD</sub>  | Differential load resistance (external) between the LVDS output pairs |               | 100 |               | Ω    |

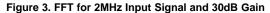

### **ELECTRICAL CHARACTERISTICS**

Typical values are at 25°C, MIN and MAX values are across the full temperature range of  $T_{min} = -40$ °C to  $T_{max} = 85$ °C, AVDD3 = 3.3V, AVDD18 = 1.8V, DVDD18 = 1.8V, -1dBFS analog input ac-coupled with 0.1μF, internal reference mode, maximum-rated sampling frequency (65MSPS), LVCMOS (single-ended) clock, 50% duty cycle, antialiasing filter set at 14MHz (3dB corner), output clamp disabled<sup>(1)</sup> and analog high-pass filter enabled, unless otherwise noted.

|         | PARAMETER                     | TEST CO                     | ONDITIONS | MIN  | TYP           | MAX  | UNIT |

|---------|-------------------------------|-----------------------------|-----------|------|---------------|------|------|

| VARIABI | LE GAIN AMPLIFIER (VGA)       |                             |           |      |               |      |      |

|         | Maximum input voltage swing   | Linear operation, from IN   | P to INM  |      | 2             |      | Vpp  |

| VCM     | Common-mode voltage           |                             |           |      | 1.6           |      | V    |

|         | Gain range                    | Maximum gain – minimur      | n gain    |      | 36            |      | dB   |

|         | Maximum gain                  |                             |           | 29.5 | 31            | 32.5 | dB   |

|         | Gain resolution               |                             |           |      | 0.125<br>or 1 |      | dB   |

|         | Input resistance              | From each input to dc bia   | is level  |      | 5             |      | kΩ   |

|         | Input capacitance             | Differential between the in | nputs     |      | 2             |      | pF   |

| ANTIALI | AS FILTER (AAF)               |                             |           | •    |               |      |      |

|         |                               | 7.5MHz filter selected      |           |      | 7.5           |      |      |

|         | AAF cutoff frequency          | 10MHz filter selected       | –3dB      |      | 10            |      | MHz  |

|         |                               | 14MHz filter selected       |           |      | 14            |      |      |

|         |                               | 7.5MHz filter selected      |           |      | 10            |      |      |

|         |                               | 10MHz filter selected       | –6dB      |      | 14            |      | MHz  |

|         | ^ ^ C atom board attanceation | 14MHz filter selected       |           |      | 20            |      |      |

|         | AAF stop-band attenuation     | 7.5MHz filter selected      |           |      | 18            |      |      |

|         |                               | 10MHz filter selected       | -12dB     |      | 24            |      | MHz  |

|         |                               | 14MHz filter selected       |           |      | 30            |      |      |

|         |                               | 7.5MHz filter selected      |           |      | 1.2           |      |      |

|         | In-band attenuation           | 10MHz filter selected       | At 3.2MHz |      | 0.5           |      | dB   |

|         |                               | 14MHz filter selected       |           |      | 0.2           |      |      |

<sup>(1)</sup> Enabling clamping increases distortion values at high swings by about 2dB.

Submit Documentation Feedback Product Folder Link(s): AFE5801

Typical values are at 25°C, MIN and MAX values are across the full temperature range of  $T_{min} = -40$ °C to  $T_{max} = 85$ °C, AVDD3 = 3.3V, AVDD18 = 1.8V, DVDD18 = 1.8V, -1dBFS analog input ac-coupled with 0.1 $\mu$ F, internal reference mode, maximum-rated sampling frequency (65MSPS), LVCMOS (single-ended) clock, 50% duty cycle, antialiasing filter set at 14MHz (3dB corner), output clamp disabled <sup>(1)</sup> and analog high-pass filter enabled, unless otherwise noted.

|                     | PARAMETER                             | TEST CONDITIONS                                                                                                                                                             | MIN  | TYP  | MAX | UNIT               |

|---------------------|---------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-----|--------------------|

| FULL-CHAN           | NNEL CHARACTERISTICS                  |                                                                                                                                                                             | ·    |      |     | •                  |

|                     | Gain matching                         | Across channels and parts                                                                                                                                                   |      | 0.1  | 0.6 | dB                 |

|                     | 0-1                                   | -5dB to 28dB gain                                                                                                                                                           | -1.2 | ±0.3 | 1.2 | -ID                |

|                     | Gain error                            | Gain > 28dB                                                                                                                                                                 | -1.8 | ±0.5 | 1.8 | dB                 |

|                     | Offset error                          | 31dB gain                                                                                                                                                                   | -50  |      | 50  | LSB                |

|                     | land the reference of the contract of | 5MHz, 31dB VGA gain, low-noise mode                                                                                                                                         |      | 5    | 6.5 | nV/√ <del>Hz</del> |

|                     | Input-referred noise voltage          | 5MHz, 31dB VGA gain, default noise mode                                                                                                                                     |      | 5.5  |     | nV/√Hz             |

| SNR                 | Signal-to-noise ratio                 | -1dBFS ADC input, 6dB gain                                                                                                                                                  |      | 66   |     | dBc                |

| HD2                 | On any difference of a distantian     | -1dBFS ADC input, 17dB gain, f <sub>in</sub> = 2MHz                                                                                                                         |      | -75  | -60 | JD -               |

|                     | Second-harmonic distortion            | -1dBFS ADC input, 31dB gain, f <sub>in</sub> = 2MHz                                                                                                                         |      | -75  | -60 | dBc                |

| LIDO                | Think have a feet attention           | -1dBFS ADC input, 17dB gain, f <sub>in</sub> = 2MHz                                                                                                                         |      | -65  | -55 | JD -               |

| HD3                 | Third-harmonic distortion             | -1dBFS ADC input, 31dB gain, f <sub>in</sub> = 2MHz                                                                                                                         |      | -60  | -52 | dBc                |

| SFDR                | Spurious-free dynamic range           | -1dBFS ADC input, 17dB gain, f <sub>in</sub> = 2MHz                                                                                                                         |      | 65   |     | dBc                |

| THD                 | Total harmonic distortion             | -1dBFS ADC input, 17dB gain, f <sub>in</sub> = 2MHz                                                                                                                         |      | 64   |     | dBc                |

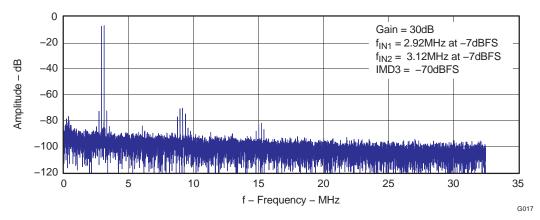

| IMD                 | Intermodulation distortion            | $f_{in1}$ = 1MHz, $f_{in2}$ = 2MHz, $A_{in1, in2}$ = -7dBFS, 30dB VGA gain                                                                                                  |      | -70  |     | dBFS               |

|                     | Group delay variation                 | f = 100kHz to 14MHz, across gain settings and channels                                                                                                                      |      | ±3.5 |     | ns                 |

|                     |                                       | f = 100kHz to 14MHz, across channels                                                                                                                                        |      | ±1.5 |     |                    |

|                     | Input overload recovery               | ≤ 6dB overload to within 1%                                                                                                                                                 |      | 1    |     | Clock<br>cycle     |

|                     | Clamp level                           | After amplification. Clamp enabled by default                                                                                                                               |      | 3    |     | dB                 |

|                     | ADC number of bits                    |                                                                                                                                                                             |      | 12   |     |                    |

|                     | Crosstalk                             | Aggressor: f <sub>in</sub> = 3MHz, 1dB below ADC full-scale Victims (channel next to aggressor channel): 50Ω differential (between IN <sub>i</sub> P and IN <sub>i</sub> M) |      | 92   |     | dB                 |

| POWER               |                                       | ,                                                                                                                                                                           |      |      |     | I                  |

|                     |                                       | Default noise mode                                                                                                                                                          |      | 522  | 600 | 144                |

|                     | Total power dissipation               | Low-noise mode                                                                                                                                                              |      | 561  | 636 | mW                 |

| I <sub>AVDD3</sub>  | AVDD3 current consumption             |                                                                                                                                                                             |      | 6    | 9   | mA                 |

| I <sub>AVDD18</sub> | AVDD18 current consumption            | Default noise mode                                                                                                                                                          |      | 198  | 222 | 0                  |

|                     |                                       | Low-noise mode                                                                                                                                                              |      | 220  | 244 | mA                 |

| I <sub>DVDD18</sub> | DVDD18 current consumption            | See (2)                                                                                                                                                                     |      | 81   | 100 | mA                 |

|                     | Davis davis                           | Standby mode                                                                                                                                                                |      | 64   |     | mW                 |

|                     | Power down                            | Full power-down mode                                                                                                                                                        |      | 8    | 25  | mW                 |

| AC PSRR             | Power-supply rejection ratio          |                                                                                                                                                                             |      | 30   |     | dBc                |

<sup>(2)</sup> Using digital modes like averaging, digital gain, digital HPF, etc., (see the *Application Information* section) might increase the DVDD18 current by about 60mA.

# DIGITAL CHARACTERISTICS(1)

The dc specifications refer to the condition where the digital outputs are not switching, but permanently at a valid logic level 0 or 1. Typical values are at 25°C, min and max values are across the full temperature range of  $T_{min} = -40$ °C to  $T_{max} = 85$ °C, AVDD3 = 3.3V, AVDD18 = 1.8V, DVDD18 = 1.8V, external differential load resistance between the LVDS output pair  $R_{LOAD} = 100\Omega$ .

| PARAMETER                                            | TEST CONDITIONS                                                   | MIN | TYP     | MAX | UNIT |

|------------------------------------------------------|-------------------------------------------------------------------|-----|---------|-----|------|

| DIGITAL INPUTS (PDN, RESET, S                        | SCLK, SDATA, SEN, SYNC)                                           |     |         | '   |      |

| High-level input voltage                             |                                                                   | 1.4 |         | 3.6 | V    |

| Low-level input voltage                              |                                                                   |     |         | 0.8 | V    |

| High-level input current                             |                                                                   |     | 10      |     | μΑ   |

| Low-level input current                              |                                                                   |     | 10      |     | μΑ   |

| Input capacitance                                    |                                                                   |     | 4       |     | pF   |

| DIGITAL OUTPUTS (D <sub>i</sub> P, D <sub>i</sub> M) |                                                                   |     |         |     |      |

| High-level output voltage                            |                                                                   |     | 1375    |     | mV   |

| Low-level output voltage                             |                                                                   |     | 1025    |     | mV   |

| Output differential voltage  V <sub>OD</sub>         |                                                                   | 270 | 380     | 490 | mV   |

| Output offset voltage V <sub>OS</sub>                | Common-mode voltage of D <sub>i</sub> P and D <sub>i</sub> M      | 0.9 | 1.15    | 1.5 | V    |

| Output capacitance                                   | Output capacitance inside the device, from either output to DVSS. |     | 2       |     | pF   |

| DIGITAL OUTPUTS (SDOUT)                              |                                                                   |     |         |     |      |

| High-level output voltage                            |                                                                   | 1.6 | 1.8     |     | V    |

| Low-level output voltage                             |                                                                   |     | 0       | 0.2 | V    |

| Output impedance                                     |                                                                   |     | 50 ±25% |     | Ω    |

<sup>(1)</sup> All LVDS specifications have been characterized but not tested at production. For clock input levels, see the *Recommended Operating Conditions* table.

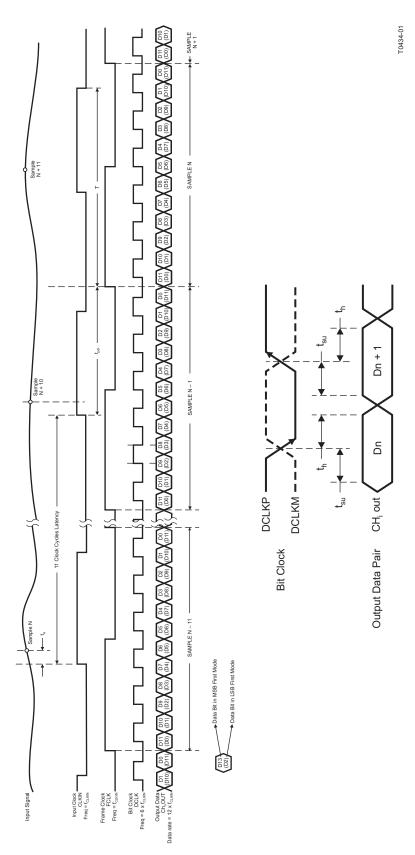

### **OUTPUT INTERFACE TIMING**

Typical values are at 25°C, AVDD3 = 3.3V, AVDD18 = DVDD = 1.8V, LVCMOS (single ended) clock,  $C_{LOAD}$  = 5pF,  $R_{LOAD}$  = 100 $\Omega$ ,  $I_O$  = 3.5mA, unless otherwise noted. Minimum and maximum values are across the full temperature range  $T_{MIN}$  = -40°C to  $T_{MAX}$  = 85°C.

|                       | PARAMETER                                      | TEST CONDITIONS                                                                                                        | MIN | TYP  | MAX  | UNIT                     |

|-----------------------|------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|-----|------|------|--------------------------|

| t <sub>a</sub>        | Aperture delay                                 | The delay in time between the rising edge of the input sampling clock and the actual time at which the sampling occurs | 0.7 | 3    |      | ns                       |

|                       | Aperture delay matching                        | Across channels within the same device                                                                                 |     | ±150 |      | ps                       |

| tj                    | Aperture jitter                                |                                                                                                                        |     | 450  |      | fs rms                   |

|                       |                                                | Time to valid data after coming out of STANDBY mode                                                                    |     | 10   | 50   |                          |

|                       | Wake-up time                                   | Time to valid data after coming out of PDN GLOBAL mode                                                                 |     | 50   | 200  | μS                       |

|                       |                                                | Time to valid data after stopping and restarting the input clock                                                       |     | 30   | 200  |                          |

|                       | ADC latency                                    | Default, after reset                                                                                                   |     | 11   |      | Input<br>clock<br>cycles |

| t <sub>delay</sub>    | Data and frame clock delay                     | Input clock rising edge (zero cross) to frame clock rising edge (zero cross) minus half the input clock period (T).    | 3   | 4.7  | 6.4  | ns                       |

| Δt <sub>delay</sub>   | Delay variation                                | At fixed supply and 20°C T difference                                                                                  | -1  |      | 1    | ns                       |

| t <sub>RISE</sub>     | Data rise time<br>Data fall time               | Rise time measured from –100mV to 100mV Fall time measured from 100mV to –100mV 10MHz < f <sub>CLKIN</sub> < 65MHz     | 0.1 | 0.25 | 0.4  | ns                       |

| t <sub>FCLKRISE</sub> | Frame clock rise time<br>Frame clock fall time | Rise time measured from -100mV to 100mV Fall time measured from 100mV to -100mV 10MHz < f <sub>CLKIN</sub> < 65MHz     | 0.1 | 0.25 | 0.4  | ns                       |

|                       | Frame clock duty cycle                         | Zero crossing of the rising edge to zero crossing of the falling edge                                                  | 48% | 50%  | 52%  |                          |

| t <sub>DCLKRISE</sub> | Bit clock rise time<br>Bit clock fall time     | Rise time measured from –100mV to 100mV Fall time measured from 100mV to –100mV 10MHz < f <sub>CLKIN</sub> < 65MHz     | 0.1 | 0.2  | 0.35 | ns                       |

|                       | Bit clock duty cycle                           | Zero crossing of the rising edge to zero crossing of the falling edge 10MHz < f <sub>CLKIN</sub> < 65MHz               | 44% | 50%  | 56%  |                          |

# Output Interface Timing(1)

| f <sub>CLKIN</sub> , Input Clock Frequency | Period (T) | Setup                                               | Time (t <sub>su</sub> ),<br>ns |     | Hold | d Time (t <sub>h</sub> ),<br>ns |     | t <sub>pdi</sub> = 0.5 | $t_{pdi} = 0.5 \times T + t_{delay}$ , ns                                 |     |

|--------------------------------------------|------------|-----------------------------------------------------|--------------------------------|-----|------|---------------------------------|-----|------------------------|---------------------------------------------------------------------------|-----|

| MHz                                        | ns         | Zero-Cross Data to Zero-Cross<br>Clock (both edges) |                                |     |      |                                 |     | edge) to Fram          | Input Clock Zero-Cross (ri<br>edge) to Frame Clock Zero-<br>(rising edge) |     |

|                                            |            | MIN                                                 | TYP                            | MAX | MIN  | TYP                             | MAX | MIN                    | TYP                                                                       | MAX |

| 65                                         | 15         | 0.35                                                | 0.6                            |     | 0.3  | 0.6                             |     |                        | 12.3                                                                      |     |

| 50                                         | 20         | 0.5                                                 | 0.8                            |     | 0.5  | 0.8                             |     |                        | 14.6                                                                      | •   |

| 40                                         | 25         | 0.75                                                | 1                              |     | 0.75 | 1                               |     |                        | 17                                                                        |     |

| 30                                         | 33         | 1                                                   | 1.4                            |     | 1    | 1.4                             |     |                        | 21.2                                                                      | •   |

| 20                                         | 50         | 1.7                                                 | 2.1                            |     | 1.7  | 2.1                             |     |                        | 29.5                                                                      |     |

| 10                                         | 100        | 3.8                                                 | 4.2                            |     | 3.8  | 4.2                             |     |                        | 54.7                                                                      |     |

<sup>(1)</sup> FCLK timing is the same as for the output data lines. It has the same relation to DCLK as the data pins. Setup and hold are the same for the data and the frame clock.

Figure 1. Timing Diagram

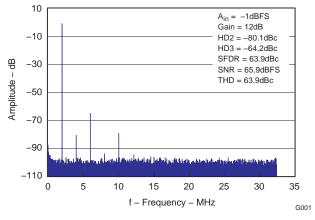

### TYPICAL CHARACTERISTICS

10  $A_{in} = -1dBFS$ Gain = 30dB-10 HD2 = -69.8dBcHD3 = -59.5dBcSFDR = 59.5dBc – dB -30 SNR = 58.8dBFSTHD = 58.9dBc Amplitude -50 -70 -90 0 5 10 20 25 30 35 f - Frequency - MHz

Figure 2. FFT for 2MHz Input Signal and 12dB Gain

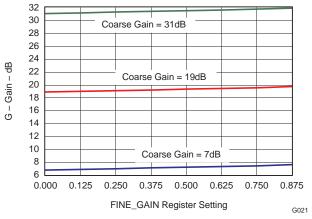

Figure 4. Fine Gain vs Gain Code

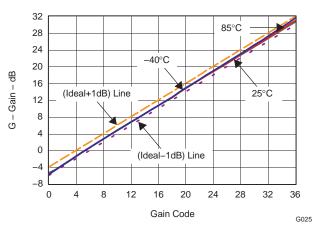

Figure 5. Gain vs Gain Code and Temperature

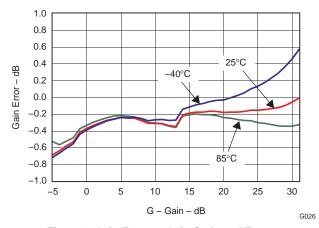

Figure 6. Gain Error vs Gain Code and Temperature

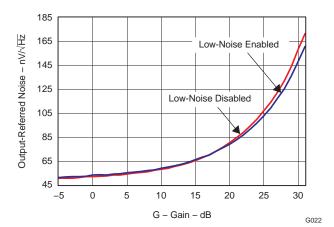

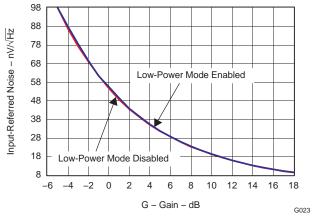

Figure 7. Output-Referred Noise vs Gain

11 10 9 8 Low-Power Mode Disabled 7 6 Low-Power Mode Enabled 5 Low-Power Mode Enabled 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 G - Gain - dB

Figure 8. Input-Referred Noise for Low Gains

Figure 9. Input-Referred Noise for High Gains

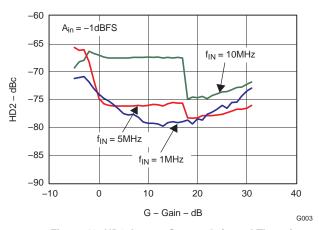

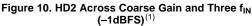

Figure 11. HD2 Across Coarse Gain and Three  $f_{IN}$  (-6dBFS)<sup>(2)</sup>

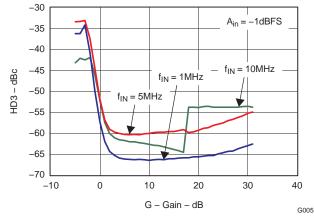

<sup>(1)</sup> For gains ≥5dB, the input amplitude is adjusted to give -1dBFS. At 5dB gain, input amplitude is 4dBm (corresponding to -1dBFS). For gains less than 5dB, the input is kept constant at 4dBm.

<sup>(2)</sup> For gains ≥0dB, the input amplitude is adjusted to give –6dBFS. At 0dB gain, input amplitude is 4dBm (corresponding to –6dBFS). For gains less than 0dB, the input is kept constant at 4dBm.

-40  $A_{in} = -6dBFS$  $f_{IN} = 5MHz$ -50  $f_{IN} = 10MHz$  $f_{IN} = 1MHz$ -60 HD3 - dBc -70 -80 -90 -10 10 40 G - Gain - dB G006

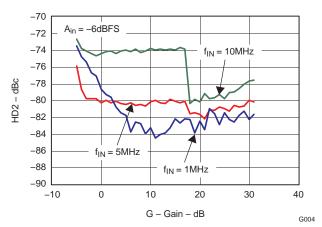

Figure 12. HD3 Across Coarse Gain and Three  $f_{IN}$  (-1dBFS)<sup>(1)</sup>

Figure 13. HD3 Across Coarse Gain and Three  $f_{IN}$   $(-6dBFS)^{(2)}$

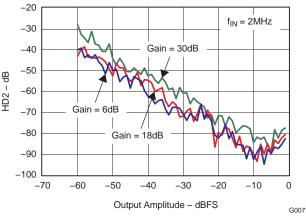

Figure 14. HD2 vs Output Amplitude

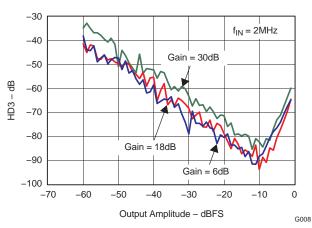

Figure 15. HD3 vs Output Amplitude

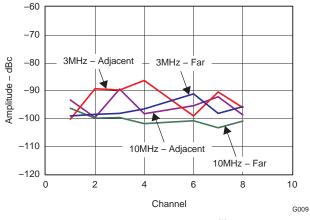

Figure 16. Crosstalk (3)

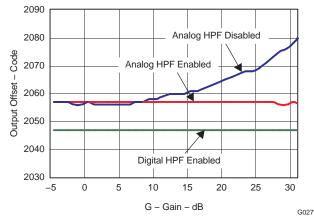

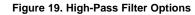

Figure 17. Output Offset vs Gain

- (3) -1dB signal applied on one channel at a time and output is observed on:

- 1. Adjacent channel channel next to the aggressor channel, but not a shared channel

- 2. Far channel all other channels (neither shared or adjacent)

All graphs are at 25°C, AVDD3 = 3.3V, AVDD18 = DVDD18 = 1.8V, -1dBFS analog input AC coupled with  $0.1\mu F$ , internal reference mode, maximum rated channel sampling frequency (65MSPS), LVCMOS (single-ended) clock, 50% duty cycle,  $f_{IN}$  = 2MHz, anti-aliasing filter set at 14MHz (3dB corner), output clamp disable and analog high-pass filter enabled.

20 K = 7dBAnalog Filter 10 -10K = 4dB-20 K = 2dBGain -30 K = 5dBK = 3dBပ္ပ -40 K = 6dB-50 K = 8dBK = 9dB-60K = 10dB0.0 2.0 1.5 2.5 3.0 f - Frequency - MHz G011

Figure 18. Antialiasing Filter Frequency Response

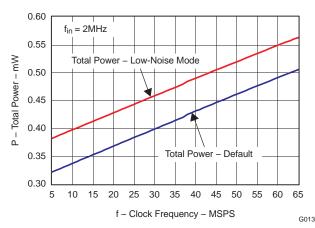

Figure 20. Analog Power vs Input-Clock Frequency

Figure 21. Total Power vs Input-Clock Frequency

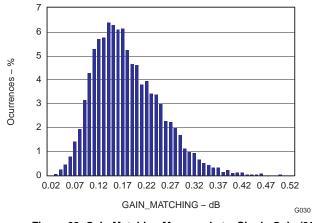

Figure 22. Gain Matching Measured at a Single Gain (30 dB) as Peak-to-Peak Variation of Gain Across Channels on Every Device and Measured at Three Temperatures. Every Device at Each Temperature Counted as One Event

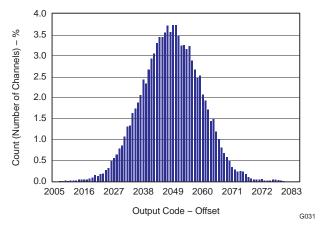

Figure 23. Offset (Average Code) With Signal. Every Channel Counted as One Event

Copyright © 2008–2010, Texas Instruments Incorporated

All graphs are at 25°C, AVDD3 = 3.3V, AVDD18 = DVDD18 = 1.8V, -1dBFS analog input AC coupled with  $0.1\mu F$ , internal reference mode, maximum rated channel sampling frequency (65MSPS), LVCMOS (single-ended) clock, 50% duty cycle,  $f_{IN}$  = 2MHz, anti-aliasing filter set at 14MHz (3dB corner), output clamp disable and analog high-pass filter enabled.

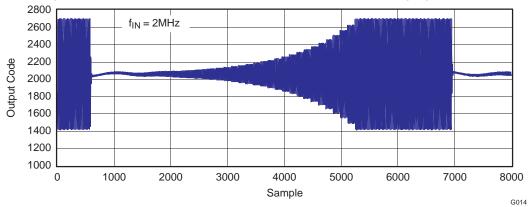

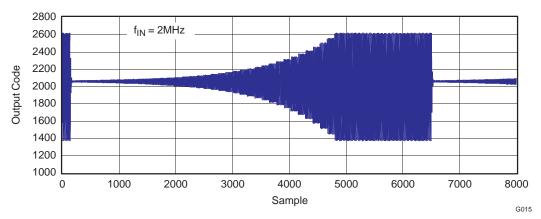

Figure 24. TGC Sweep With Interpolation Disabled and High-Pass Filter Enabled

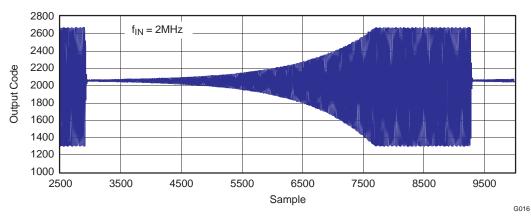

Figure 25. TGC Sweep With Interpolation Disabled and High-Pass Filter Disabled

Figure 26. TGC Sweep With Interpolation Enabled and High-Pass Filter Disabled

Figure 27. Intermodulation Distortion

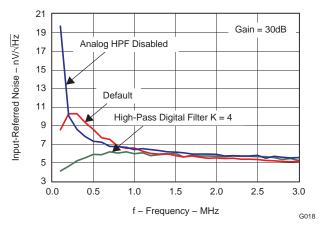

Figure 28. Input-Referred Noise vs Frequency

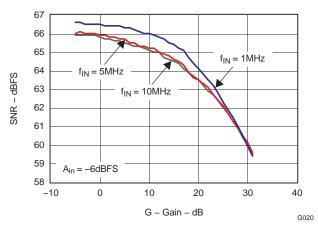

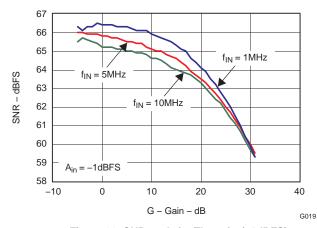

Figure 30. SNR vs Gain Three f<sub>IN</sub> (-6dBFS)

Figure 29. SNR vs Gain, Three f<sub>IN</sub> (-1dBFS)

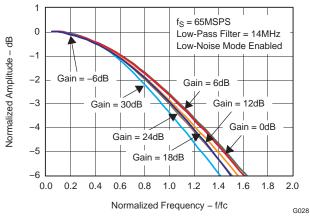

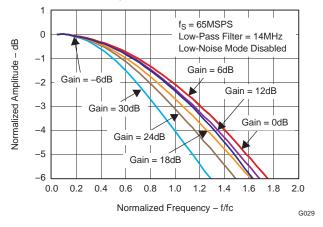

Figure 31. LPF Response Across Coarse Gain

File Edit Verbical Horiz/Acq Trig Display Cursors Measure Mads Math Utilities Help

Strong Sample

Curs 1 Pos

-90 (np

Curs 2 Pos

-92 (np

Curs 2 Pos

-92

Figure 32. LPF Response Across Coarse Gain

Figure 33. LVDS Eye Pattern

#### **APPLICATION INFORMATION**

#### THEORY OF OPERATION

The AFE5801 is a very low-power CMOS monolithic analog front end which includes an eight-channel variable-gain amplifier (VGA) followed by an eight-channel, 12bit, high-speed pipeline analog-to-digital convereter (ADC) based on switched-capacitor architecture.

Each of the eight VGA differential inputs is buffered and accepts a maximum swing of 2Vpp centered at a dc level (VCM) of about 1.6V.

Each VGA has a gain range from -5dB to 31dB, and the gain is digitally controlled, with a resolution of 0.125dB. Using the serial interface, the gain curves (common to all VGAs) versus time can be stored in the memory integrated within the device.

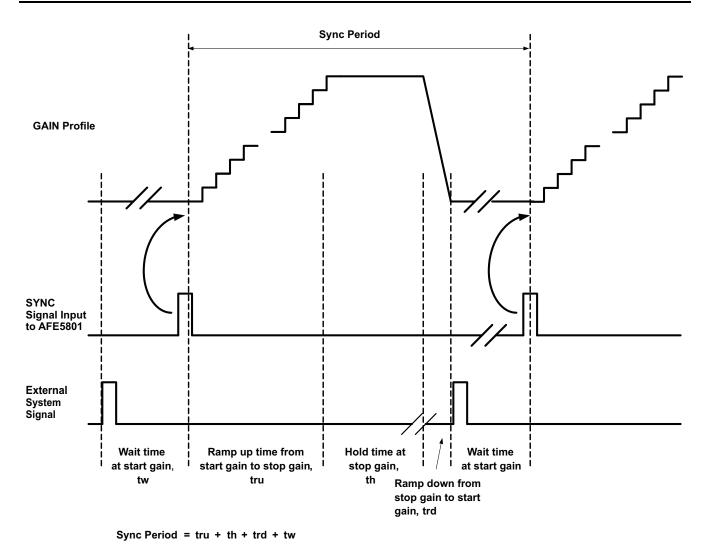

A hardware sync input pin is available (SYNC). When a pulse is applied to this pin, all the VGAs in the device start stepping through the selected time-gain curve at the same clock cycle. This sync can also be initiated by software using the serial interface.

A selectable anti-alias low-pass filter (AAF) with 3dB attenuation at 7.5MHz, 10MHz, or 14MHz is also integrated, together with clamping (which can be disabled).

The VGA/AAF can output 2Vpp differential swing without degradation in the specified linearity and can drive an onboard 12bit ADC. After the input signals are captured by the sample-and-hold circuit, at the rising edge of the clock, the samples are sequentially converted by a series of low-resolution stages. The outputs of the stages are combined in a digital correction logic block to form the final 12bit word with a latency of 11 clock cycles, without taking into account the delays introduced by the optional digital signal-processing functions. These functions are, in this order, offset correction, channel averaging, digital gain, and high-pass filtering (see *General-Purpose Register Map* for more details). The 12bit words of each channel are serialized and output as LVDS levels. For slower operation speeds, the AFE5801 offers the possibility of multiplexing up to two input channels into one LVDS output stream, reducing even further the power consumption and routing area. In addition to the data streams, a bit clock and frame clock are also output. The frame clock is aligned with the 12bit word boundary.

Notice that for the correct operation of the device (see the *Serial Interface* section), a positive pulse must be applied to the RESET pin. This sets the internal control registers to zero. There is, nevertheless, no need for any type of power-up sequencing.

### INPUT CONFIGURATION

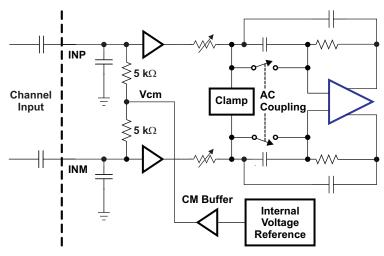

The analog input for the AFE5801, Figure 34, consists of a differential analog buffer which has inputs biased to 1.6V (usually refered as common-mode voltage,  $V_{CM}$ ). The biasing is done with two internal resistors of  $5k\Omega$ . For proper operation, the input signal should be either ac-coupled or have a commn-mode value equal to  $V_{CM}$ . In the case of ac coupling, the external input capacitors form a high-pass filter with the internal bias resistors  $(5k\Omega)$ , so, the value of the capacitors should allow the lowest frequency of interest to pass with minimum attenuation. For the typical frequencies used in ultrasound (>1MHz) a value of 10nF or bigger is recommended. If dc coupling is preferred, the user can tap the  $V_{CM}$  output pins to set the common-mode level of the input signal. The  $V_{CM}$  output should be connected to high-input-impedance circuits, as its driving capability is limited. Regardless of the choosen input configuration, a capacitor of 100nF should be connected on each  $V_{CM}$  input to AVSS.

For proper operation, the input signal should be in the recommended input range. The maximum input swing is limited to 2Vpp before saturation/distortion fo the input stage occurs. As the input common mode (VCM) is about 1.6V, each input of the buffer should stay between 1.1V and 2.1V.

NOTE: Dashed area denotes one of eight channels.

Figure 34. Common-Mode Biasing of Input Pins

The maximum input swing is limited to 2Vpp before distortion/saturation of the input stage occurs. As the input dc level (VCM) is about 1.6V, this means that each input of the VGA typically stays between 1.1V and 2.1V.

To drive the AFE5801 with a single-ended signal, the signal should be connected to one of the inputs ( $IN_iP$ , in principle, to keep the polarity) and the other connected to AVSS through a 100nF capacitor. In fact, all the AFE5801 inputs that must be connected to ground can be shorted together and connected to ground through a single 100nF capacitor. The input is limited to 1Vpp (from 1.1V to 2.1V) and the performance is similar to that of the AFE5851. Every channel on the AFE5851 is similar to a channel on the AFE5801 where the other input has been shorted internally to VCM. See the AFE5851 16 Channel Variable Gain Amplifier (VGA) With Octal High Speed ADC data sheet (SLOS574) for more information.

# **SERIAL INTERFACE**

#### **Register Initialization**

After power up, the internal registers must be initialized to the default value (zero). Initialization can be done in one of two ways:

- Through a hardware reset, by applying a positive pulse in the RESET pin

- Through a software reset, using the serial interface, by setting the SOFTWARE RESET bit to high. Setting

this bit initializes the internal registers to the respective default values (all zeros) and then self-resets the

SOFTWARE RESET bit to low. In this case, the RESET pin can stay low (inactive).

It is important to notice that after power up and before the device is reset to its default state, the power consumption could be up to 2x the specified maximum, due to the unknown setting of the internal registers. In order to prevent the initial increased power consumption, a potential solution is to connect the RESET pin to either 1.8V or 3.3V supply with a  $10k\Omega$  resistor, so that the device is reset while powering up. For the reset to take effect, the power must be up on DVDD18. Notice that there is no damage to the part by applying voltage to the RESET pin while the device power is off.

Notice also that the reset only affects the digital registers, putting the part in its default state. It does not act as a power down and as such, everything internal just keeps running. As the internal registers change their values, the effects on the data propagate through the pipe. At the same time, there may be some glitches on the output due to the transition of the registers values if any of the output controlling modes, for instance, change. As the reset is level-sensitive and asynchronous with the input clock, it should be inactive in order to write into the internal registers. Although it takes only 10ns after the reset rising edge to change the registers, the output data may take, in the worst case, up to 20 clock cycles to be considered stable. Notice that the output clocks (data and frame) are independent of the RESET and tight to the input clock, avoiding any loss of synchronization.

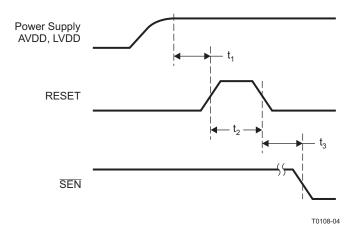

#### Reset Timing

Typical values at 25°C, min and max values across the full temperature range  $T_{MIN} = -40$ °C to  $T_{MAX} = 85$ °C, AVDD3 = 3.3V, AVDD18 = DVDD18 = 1.8V, unless otherwise noted.

|                | PARAMATER                 | CONDITIONS                                                 | MIN | TYP N | ΙΑΧ | UNIT |

|----------------|---------------------------|------------------------------------------------------------|-----|-------|-----|------|

| t <sub>1</sub> | Power-on delay time       | Delay from power-up of AVDD and LVDD to RESET pulse active | 5   |       |     | ms   |

| t <sub>2</sub> | Reset pulse width         | Pulse width of active RESET signal                         | 10  |       |     | ns   |

| t <sub>3</sub> | Register write delay time | Delay from RESET disable to SEN active                     | 25  |       |     | ns   |

| $t_{PO}$       | Power-up delay time       | Delay from power-up of AVDD and LVDD to output stable      |     | 6.5   |     | ms   |

Figure 35. Reset Timing

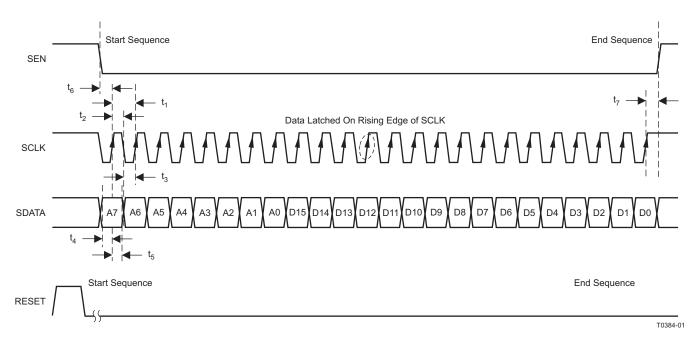

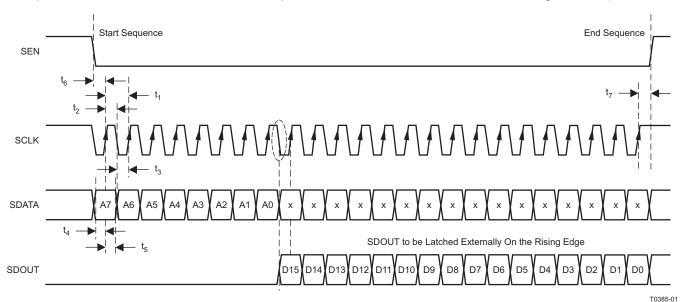

Programming of different modes can be done through the serial interface formed by pins  $\overline{\text{SEN}}$  (serial interface enable), SCLK (serial interface clock),  $\overline{\text{SDATA}}$  (serial interface data) and RESET. SCLK and SDATA have a 100k $\Omega$  pulldown resistor to ground, and  $\overline{\text{SEN}}$  has a 100k $\Omega$  pullup resistor to DVDD18. Serial shift of bits into the device is enabled when  $\overline{\text{SEN}}$  is low. Serial data SDATA is latched at every rising edge of  $\overline{\text{SEN}}$  is low. In case the word length exceeds a multiple of 24 bits, the excess bits are ignored. Data can be loaded in multiples of 24bit words within a single active  $\overline{\text{SEN}}$  pulse (there is an internal counter that counts groups of 24 clocks after the falling edge of  $\overline{\text{SEN}}$ ). The interface can work with SCLK frequency from 20MHz down to very low speeds (a few Hertz) and even with a non-50% duty-cycle SCLK.

The data is divided in two main portions: a register address (8 bits) and the data itself, to load on the addressed register (16 bits). When writing to a register with unused bits, these should be set to 0. Also, when writing, the SDOUT signal outputs zeros. The following timing diagram illustrates this process.

Figure 36. Serial Interface Register Write

Minimum values across full temperature range  $T_{MIN} = -40^{\circ}C$  to  $T_{MAX} = 85^{\circ}C$ , AVDD3 = 3.3V, AVDD18 = DVDD18 = 1.8V.

| PARAMETER      | DESCRIPTION                                           | MIN | TYP | MAX | UNIT |

|----------------|-------------------------------------------------------|-----|-----|-----|------|

| t <sub>1</sub> | SCLK period                                           | 50  |     |     | ns   |

| t <sub>2</sub> | SCLK high time                                        | 20  |     |     | ns   |

| t <sub>3</sub> | SCLK low time                                         | 20  |     |     | ns   |

| t <sub>4</sub> | Data setup time                                       | 5   |     |     | ns   |

| t <sub>5</sub> | Data hold time                                        | 5   |     |     | ns   |

| t <sub>6</sub> | SEN fall to SCLK rise                                 | 8   |     |     | ns   |

| t <sub>7</sub> | Time between last SCLK rising edge to SEN rising edge | 8   |     |     | ns   |

### **GENERAL-PURPOSE REGISTER MAP**

The internal registers can be divided in two groups, a group of registers to control all the general functions and settings of the device, and a bank of registers to control the TGC/gain curves operation. Those two sets of registers overlap in all the address space, except for the address 0, which holds the control of the register bank. One of the bits of this register, TGC\_REG\_WREN (see following table) is used to access one set of registers or the other. Its default value is zero and gives access to the general-purpose registers (which are also by default zero). The TGC control registers (described after the general-purpose registers) can be accessed by writing 1 to TGC REG WREN.

The following table describes the function of the registers when TGC\_REGISTER\_WREN = 0 (default). The address format is address[bit of the register].

| ADDRESS | FUNCTION                                  | DESCRIPTION                                                                               |

|---------|-------------------------------------------|-------------------------------------------------------------------------------------------|

| 0[2]    | TGC_REGISTER_WREN                         | 0: Access to general-purpose registers. 1: Access to TGC registers                        |

| 0[1]    | REGISTER_READOUT_ENABLE                   | 1: Enables readout of the registers                                                       |

| 0[0]    | SOFTWARE_RESET                            | 1: Resets the device and self-resets the bit to zero                                      |

| 1[14]   | OUTPUT_RATE_2X                            | 0: 1x rate (one ADC per LVDS stream). 1: 2x rate (2 ADCs per LVDS stream)                 |

| 1[13]   | EXTERNAL_REFERENCE                        | 0: Internal reference. 1: External reference                                              |

| 1[11]   | ${\tt LOW\_FREQUENCY\_NOISE\_SUPRESSION}$ | 0: No supression. 1: Supresses noise at low frequencies and pushes it to $f_{\text{S}}/2$ |

### www.ti.com

| ADDRESS   | FUNCTION                                                  | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

|-----------|-----------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1[10]     | STDBY                                                     | 0: Power up. 1: Standby (fast power-up mode)                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| 1[9:2]    | PDN CHANNEL<7:0>                                          | PDN for each individual channel (VCA+ADC). LVDS outputs logic 0.                                                                                                                                                                                                                                                                                                                                                                                             |  |

| 1[1]      | OUTPUT_DISABLE                                            | 0: Ouptut enabled. 1: Output disabled                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| 1[0]      | GLOBAL_PDN                                                | 0: Power up. 1: Global power down (slow power-up mode)                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| 2[15:13]  | PATTERN_MODES                                             | Pattern modes for serial LVDS. 000: No pattern. 001: Sync. 010: Deskew. 011: Custom reg. 100: All 1s. 101: toggle. 110: All 0s. 111: Ramp                                                                                                                                                                                                                                                                                                                    |  |

| 2[11]     | AVERAGING_ENABLE                                          | 0: Default (no averaging). 1: Average two channels to increase SNR.                                                                                                                                                                                                                                                                                                                                                                                          |  |

| 2[10:3]   | PDN_LVDS                                                  | Power down the eight data-output LVDS pairs.                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| 3[14:13]  | SERIALIZED_DATA_RATE                                      | Serialization factor. 00: 12x. 01: 10x. 10: 16x. 11: 14x                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| 3[12]     | DIGITAL_GAIN_ENABLE                                       | 0: Default (no gain). 1: Apply digital gain set by the following registers.                                                                                                                                                                                                                                                                                                                                                                                  |  |

| 3[8]      | REGISTER_OFFSET_SUBTRACTION_<br>ENABLE                    | 0: Default (no subtraction). 1: Subtract offset value set in the corresponding registers.                                                                                                                                                                                                                                                                                                                                                                    |  |

| 4[3]      | DFS                                                       | Data format select. 0: 2s complement. 1: Offset binary                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| 5[13:0]   | CUSTOM_PATTERN                                            | Custom pattern data for LVDS (PATTERN_MODES = 011)                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| 7[10]     | VCA_LOW_NOISE_MODE_(INCREASE_<br>POWER)                   | 0: Low power. 1: Low noise, at the expense of increased power (5mW/channel)                                                                                                                                                                                                                                                                                                                                                                                  |  |

| 7[8:7]    | SELF_TEST                                                 | 00 or 10: No self-test. 01: Self-test enabled. 100 mV dc applied to the input of the channels. 11: Self-test enabled. 150 mV dc applied to the input of the channels. NOTE: DC applied before the input buffer. Test does not work if input is dc-shorted to a different potential. Also notice that the INTERNAL_AC_COUPLING bit is automatically set to 1 when entering this mode, and reset back to whatever value it had before, when leaving this mode. |  |

| 7[3:2]    | FILTER_BW                                                 | 00: 14MHz. 01: 10MHz. 10: 7.5MHz. 11: Not used.                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| 7[1]      | INTERNAL_AC_COUPLING                                      | VGA coupling. 0: AC-coupled. 1: DC-coupled                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| 13[15:11] | DIG_GAIN1                                                 | 0dB to 6dB in steps of 0.2dB                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| 13[9:2]   | OFFSET_CH1                                                | Value to be subtracted from channel 1                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| 15[15:11] | DIG_GAIN2                                                 | 0dB to 6dB in steps of 0.2dB                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| 15[9:2]   | OFFSET_CH2                                                | Value to be subtracted from channel 2                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| 17[15:11] | DIG_GAIN3                                                 | 0dB to 6dB in steps of 0.2dB                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| 17[9:2]   | OFFSET_CH3                                                | Value to be subtracted from channel 3                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| 19[15:11] | DIG GAIN4                                                 | 0dB to 6dB in steps of 0.2dB                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| 19[9:2]   | OFFSET_CH4                                                | Value to be subtracted from channel 4                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| 21[4:1]   | DIGITAL_HIGH_PASS_FILTER_CORNER_<br>FREQ_FOR_CHANNELS-1-4 | Sets k for the high-pass filter as desribed in <i>General-Purpose Register Description</i> (k from 2 to 10).                                                                                                                                                                                                                                                                                                                                                 |  |

| 21[0]     | DIGITAL_HIGH_PASS_FILTER_ENABLE_<br>FOR_CHANNELS_1-4      | 0: No high-pass filter. 1: High-pass filter enabled                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| 25[15:11] | DIG_GAIN8                                                 | 0dB to 6dB in steps of 0.2dB                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| 25[9:2]   | OFFSET_CH8                                                | Value to be subtracted from channel 5                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| 27[15:11] | DIG_GAIN7                                                 | 0dB to 6dB in steps of 0.2dB                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| 27[9:2]   | OFFSET_CH7                                                | Value to be subtracted from channel 6                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| 29[15:11] | DIG_GAIN6                                                 | 0dB to 6dB in steps of 0.2dB                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| 29[9:2]   | OFFSET_CH6                                                | Value to be subtracted from channel 7                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| 31[15:11] | DIG_GAIN5                                                 | 0dB to 6dB in steps of 0.2dB                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| 31[9:2]   | OFFSET_CH5                                                | Value to be subtracted from channel 8                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| 33[4:1]   | DIGITAL_HIGH_PASS_FILTER_CORNER_<br>FREQ_FOR_CHANNELS_5-8 | Sets k for the high-pass filter as desribed in <i>General-Purpose Register Description</i> (k from 2 to 10).                                                                                                                                                                                                                                                                                                                                                 |  |

| 33[0]     | DIGITAL_HIGH_PASS_FILTER_ENABLE_<br>FOR_CHANNELS_5-8      | 0: No high-pass filter. 1: High-pass filter enabled                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| 70[14]    | CLAMP_DISABLE                                             | 0: Enabled. 1: Disabled                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

#### GENERAL-PURPOSE REGISTER DESCRIPTION

#### **AVERAGING\_ENABLE**

Address: 2[11]

When set to 1, two samples, corresponding to two consecutive channels, are averaged (channel 1 with 2, 3 with 4, 5 with 6, and 7 with 8). If both channels receive the same input, the net effect is an improvement in SNR. The averaging is performed as:

- Channel 1 + channel 2 comes out on channel 3.

- Channel 3 + channel 4 comes out on channel 4.

- Channel 5 + channel 6 comes out on channel 5.

- Channel 7 + channel 8 comes out on channel 6.

#### **DFS**

Address: 4[3]

DFS stands for data format select. The ADC output, by default, is in 2s-complement mode. Programming the DFS bit to 1 inverts the MSB, and the output becomes straight-offset binary mode.

#### **DIGITAL GAIN ENABLE**

Address: 3[12]

Setting this bit to 1 applies to each channel i the corresponding gain given by DIG\_GAIN<sub>i</sub><15:11>. The gain is given as 0dB + 0.2dB × DIG\_GAIN<sub>i</sub><15:11>. For instance, if DIG\_GAIN<sub>5</sub><15:11> = 3, channel 5 is increased by 0.6dB gain. DIG\_GAIN<sub>i</sub><15:11> = 31 produces the same effect as DIG\_GAIN<sub>i</sub><15:11> = 30, setting the gain of channel i to 6dB.

### DIGITAL\_HIGH\_PASS\_FILTER\_ENABLE and DIGITAL\_HIGH\_PASS\_FILTER\_CORNER\_FREQ

DIGITAL\_HIGH\_PASS\_FILTER\_ENABLE (channels 1-4): Address: 21[0]

DIGITAL HIGH PASS FILTER ENABLE (channels 5-8): Address: 33[0]

DIGITAL HIGH PASS FILTER CORNER FREQ (channels 1-4): Address: 21[4:1]

DIGITAL\_HIGH\_PASS\_FILTER\_CORNER\_FREQ (channels 5-8): Address: 33[4:1]

This group of four registers controls the characteristics of a digital high-pass transfer function applied to the output data, following the formula:  $y(n) = 2^k/(2^k + 1) [x(n) - x(n - 1) + y(n - 1)]$ . The DIGITAL\_HIGH\_PASS\_FILTER\_CORNER\_FREQ registers (one for the first four channels and one for the second group of four channels) describe the setting of k.

#### **EXTERNAL REFERENCE**

Address: 1[13]

The internal reference mode (default) uses approximately 3mW more power on AVDD (which is already included in all the specification tables). The AFE5801 can operate in external reference mode by programming EXTERNAL\_REFERENCE to 1. In this mode, the VREF\_IN pin should be driven with 1.4V. Due to the high input impedace of this pin, no special drive capabilities are required. For the same reason, no decoupling on VREF\_IN is needed, although depending on the noise on the 1.4V signal, some filtering may be required. Nevertheless, when using the internal reference, there is no need to decouple VREF\_IN. The advantage of using the external reference mode is that multiple AFE5801 units can be made to operate with the same external reference, thereby improving parameters such as gain matching across devices.

#### FILTER BW

Address: 7[3:2]

This bit sets the 3dB attenuation frequency for the antialiasing filter (AAF).

### **GLOBAL\_PDN**

Address: 1[0]

The global PDN bit is ORed with the signal in the external PDN pin (59). Therefore, a 1 on this bit shuts the device down completely.