SBAS180B - JUNE 2001 - REVISED SEPTEMBER 2003

# 12-Bit, Sampling A/D Converter with I<sup>2</sup>C<sup>™</sup> INTERFACE

#### **FEATURES**

- **9** 50kHz SAMPLING RATE

- NO MISSING CODES

- 2.7V TO 5V OPERATION

- FOUR-WORD FILO

- A0, A1 ADDRESS PINS

- I<sup>2</sup>C INTERFACE SUPPORTS: Standard, Fast, and High-Speed Modes

- **MSOP-8 PACKAGE**

## **APPLICATIONS**

- VOLTAGE SUPPLY MONITORING

- ISOLATED DATA ACQUISITION

- TRANSDUCER INTERFACE

- BATTERY-OPERATED SYSTEMS

- REMOTE DATA ACQUISITION

#### DESCRIPTION

The ADS7823 is a single-supply, low-power, 12-bit data acquisition device that features a serial I<sup>2</sup>C interface. The Analog-to-Digital (A/D) converter features a sample-and-hold amplifier and internal, asynchronous clock. The combination of an I<sup>2</sup>C serial two-wire interface and micropower consumption makes the ADS7823 ideal for applications requiring the A/D converter to be close to the input source in remote locations and for applications requiring isolation. The ADS7823 is available in an MSOP-8 package.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

All trademarks are the property of their respective owners.

#### ABSOLUTE MAXIMUM RATINGS(1)

| +V <sub>DD</sub> to GND0.3V to +6V<br>Digital Input Voltage to GND0.3V to +V <sub>DD</sub> + 0.3V |

|---------------------------------------------------------------------------------------------------|

| Analog Input Voltage to GND0.3V to +6.0V                                                          |

| Operating Temperature Range40°C to +85°C                                                          |

| Storage Temperature Range65°C to +150°C                                                           |

| Junction Temperature (T <sub>J</sub> max)+150°C                                                   |

| TSSOP Package                                                                                     |

| Power Dissipation $(T_J max - T_A)/\theta_{JA}$                                                   |

| $\theta_{ m JA}$ Thermal Impedance+240°C/W                                                        |

| Lead Temperature, Soldering                                                                       |

| Vapor Phase (60s)+215°C                                                                           |

| Infrared (15s)+220°C                                                                              |

NOTE: (1) Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. Exposure to absolute maximum conditions for extended periods may affect device reliability.

## ELECTROSTATIC DISCHARGE SENSITIVITY

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

#### PACKAGE/ORDERING INFORMATION

| aSheet4U.com | MAXIMUM<br>INTEGRAL<br>LINEARITY<br>ERROR (LSB) | SPECIFIED<br>TEMPERATURE<br>RANGE | PACKAGE-LEAD | PACKAGE<br>DESIGNATOR <sup>(1)</sup> | PACKAGE<br>MARKING | ORDERING<br>NUMBER             | TRANSPORT<br>MEDIA, QUANTITY           |

|--------------|-------------------------------------------------|-----------------------------------|--------------|--------------------------------------|--------------------|--------------------------------|----------------------------------------|

| ADS7823E     | <u>+2</u>                                       | -40°C to +85°C                    | MSOP-8       | DGK<br>"                             | B23                | ADS7823E/250<br>ADS7823E/2K5   | Tape and Reel, 250 Tape and Reel, 2500 |

| ADS7823EB    | ±1<br>"                                         | -40°C to +85°C                    | MSOP-8       | DGK<br>"                             | B23                | ADS7823EB/250<br>ADS7823EB/2K5 | Tape and Reel, 250 Tape and Reel, 2500 |

NOTE: (1) For the most current specifications and package information, refer to our web site at www.ti.com.

### **ELECTRICAL CHARACTERISTICS: +2.7V**

At  $T_A = -40^{\circ}\text{C}$  to  $+85^{\circ}\text{C}$ ,  $+V_{DD} = +2.7\text{V}$ ,  $V_{REF} = +2.5\text{V}$ , SCL Clock Frequency = 3.4MHz (High Speed Mode) unless otherwise noted.

|                                                                                                                                                |                                                                                                                                  | ADS7823E |                                                |                              | ,   | ADS7823EB                           | }                   |                                     |

|------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|----------|------------------------------------------------|------------------------------|-----|-------------------------------------|---------------------|-------------------------------------|

| PARAMETER                                                                                                                                      | CONDITIONS                                                                                                                       | MIN      | TYP                                            | MAX                          | MIN | TYP                                 | MAX                 | UNITS                               |

| RESOLUTION                                                                                                                                     |                                                                                                                                  |          |                                                | 12                           |     |                                     | *                   | Bits                                |

| ANALOG INPUT Full-Scale Input Range Input Capacitance Input Leakage Current                                                                    |                                                                                                                                  | 0        | 25<br>±1                                       | V <sub>REF</sub>             | *   | *                                   | *                   | V<br>pF<br>μA                       |

| SYSTEM PERFORMANCE No Missing Codes Integral Linearity Error Differential Linearity Error Offset Error Gain Error Noise Power Supply Rejection |                                                                                                                                  | 12       | ±1.0<br>-0.5, +1.0<br>±1.0<br>±1.0<br>33<br>82 | ±2<br>-1.0, +3.0<br>±4<br>±4 | *   | ±0.5<br>±0.5<br>±0.75<br>±0.75<br>* | ±1<br>*<br>±3<br>±3 | Bits LSB(1) LSB LSB LSB LSB dSB     |

| SAMPLING DYNAMICS Throughput Frequency Conversion Time                                                                                         | High Speed Mode: SCL = 3.4MHz<br>Fast Mode: SCL = 400kHz<br>Standard Mode, SCL = 100kHz                                          |          | 8                                              | 50<br>8<br>2                 |     | *                                   | *<br>*<br>*         | kHz<br>kHz<br>kHz<br>μs             |

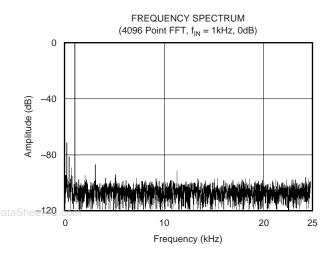

| AC ACCURACY Total Harmonic Distortion Signal-to-Ratio Signal-to-(Noise+Distortion) Ratio Spurious Free Dynamic Range                           | $V_{IN} = 2.5V_{PP}$ at 10kHz<br>$V_{IN} = 2.5V_{PP}$ at 10kHz<br>$V_{IN} = 2.5V_{PP}$ at 10kHz<br>$V_{IN} = 2.5V_{PP}$ at 10kHz |          | -82<br>72<br>71<br>86                          |                              |     | *<br>*<br>*<br>*                    |                     | dB <sup>(2)</sup><br>dB<br>dB<br>dB |

| VOLTAGE REFERENCE INPUT<br>Range<br>Resistance<br>Current Drain                                                                                | All Modes<br>At Code 800H, HS Mode: SCL = 3.4MHz                                                                                 | 0.05     | 1.0<br>9.0                                     | V <sub>DD</sub>              | *   | *                                   | *                   | V<br>GΩ<br>μΑ                       |

## **ELECTRICAL CHARACTERISTICS: +2.7V (Cont.)**

At  $T_A = -40^{\circ}\text{C}$  to  $+85^{\circ}\text{C}$ ,  $+V_{DD} = +2.7\text{V}$ ,  $V_{REF} = +2.5\text{V}$ , SCL Clock Frequency = 3.4MHz (High Speed Mode) unless otherwise noted.

|                                        |                                                                 |                        | ADS7823E  |                        |     | ADS7823EB |     |          |

|----------------------------------------|-----------------------------------------------------------------|------------------------|-----------|------------------------|-----|-----------|-----|----------|

| PARAMETER                              | CONDITIONS                                                      | MIN                    | TYP       | MAX                    | MIN | TYP       | MAX | UNITS    |

| DIGITAL INPUT/OUTPUT                   |                                                                 |                        |           |                        |     |           |     |          |

| Logic Family                           |                                                                 |                        | CMOS      |                        |     | *         |     |          |

| Logic Levels: V <sub>IH</sub>          |                                                                 | +V <sub>DD</sub> • 0.7 |           | +V <sub>DD</sub> + 0.5 | *   |           | *   | V        |

| $V_{IL}$                               |                                                                 | -0.3                   |           | +V <sub>DD</sub> • 0.3 | *   |           | *   | V        |

| $V_{OL}$                               | At min 3mA Sink Current                                         |                        |           | 0.4                    |     |           | *   | V        |

| Input Leakage: I <sub>IH</sub>         | $V_{IH} = +V_{DD} +0.5$                                         |                        |           | 10                     |     |           | *   | μA       |

| I <sub>IL</sub>                        | V <sub>IL</sub> = -0.3                                          | -10                    |           |                        | *   |           |     | μΑ       |

| Data Format                            |                                                                 |                        | Straight  |                        |     | *         |     |          |

|                                        |                                                                 |                        | Binary    |                        |     |           |     |          |

| ADS7823 HARDWARE ADDRESS               |                                                                 |                        | 10010     |                        |     | *         |     | Binary   |

| POWER SUPPLY REQUIREMENTS              |                                                                 |                        |           |                        |     |           |     |          |

| Power Supply Voltage, +V <sub>DD</sub> | Specified Performance                                           | 2.7                    |           | 3.6                    | *   |           | *   | V        |

| Quiescent Current                      | High Speed Mode: SCL = 3.4MHz                                   |                        | 250       | 370                    |     | *         | *   | μΑ       |

|                                        | Fast Mode: SCL = 400kHz                                         |                        | 137       |                        |     | *         |     | μΑ       |

| com                                    | Standard Mode, SCL = 100kHz                                     |                        | 109       |                        |     | *         |     | μΑ       |

| Power Dissipation                      | High Speed Mode: SCL = 3.4MHz                                   |                        | 680       | 1000                   |     | *         | *   | μW       |

|                                        | Fast Mode: SCL = 400kHz                                         |                        | 370       |                        |     | *         |     | μW       |

| <b>1 2 3 4 4 4</b>                     | Standard Mode, SCL = 100kHz                                     |                        | 290       |                        |     | *         |     | μW       |

| Powerdown Mode                         | High Speed Mode: SCL = 3.4MHz                                   |                        | 60        |                        |     | *         |     | μA       |

| w/Wrong Address Selected               | Fast Mode: SCL = 400kHz                                         |                        | 23<br>5.4 |                        |     | *         |     | μA<br>   |

| Full Powerdown                         | Standard Mode, SCL = 100kHz<br>SCL Pulled HIGH, SDA Pulled HIGH |                        | 5.4<br>2  | 3000                   |     | *         | *   | μA<br>nA |

|                                        | JOE T diled Filori, JDA Fulled Filori                           |                        |           | 3000                   |     | *         |     | IIA .    |

| TEMPERATURE RANGE                      |                                                                 |                        |           |                        |     |           |     |          |

| Specified Performance                  |                                                                 | -40                    |           | 85                     | *   |           | *   | °C       |

<sup>\*</sup> Specifications same as ADS7823E.

NOTES: (1) LSB means Least Significant Bit. With  $V_{REF}$  equal to 2.5V, 1LSB is 610 $\mu$ V. (2) THD measured out to the 9th-harmonic.

## **ELECTRICAL CHARACTERISTICS: +5V**

At  $T_A = -40^{\circ}\text{C}$  to +85°C, + $V_{DD} = +5.0\text{V}$ ,  $V_{REF} = +5.0\text{V}$ , SCL Clock Frequency = 3.4MHz (High Speed Mode) unless otherwise noted.

|                                                                                                                                                |                                                                                                                                  |      | ADS7823E                                       |                          | ADS7823EB |                                     |                     |                                             |

|------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|------|------------------------------------------------|--------------------------|-----------|-------------------------------------|---------------------|---------------------------------------------|

| PARAMETER                                                                                                                                      | CONDITIONS                                                                                                                       | MIN  | TYP                                            | MAX                      | MIN       | TYP                                 | MAX                 | UNITS                                       |

| RESOLUTION                                                                                                                                     |                                                                                                                                  |      |                                                | 12                       |           |                                     | *                   | Bits                                        |

| ANALOG INPUT Full-Scale Input Range Input Capacitance Input Leakage Current                                                                    |                                                                                                                                  | 0    | 25<br>±1                                       | V <sub>REF</sub>         | *         | *                                   | *                   | V<br>pF<br>μA                               |

| SYSTEM PERFORMANCE No Missing Codes Integral Linearity Error Differential Linearity Error Offset Error Gain Error Noise Power Supply Rejection |                                                                                                                                  | 12   | ±1.0<br>-0.5, +1.0<br>±1.0<br>±1.0<br>33<br>82 | ±2<br>-1, +3<br>±4<br>±4 | *         | ±0.5<br>±0.5<br>±0.75<br>±0.75<br>* | ±1<br>*<br>±3<br>±3 | Bits LSB <sup>(1)</sup> LSB LSB LSB LSB dSB |

| SAMPLING DYNAMICS Throughput Frequency Conversion Time                                                                                         | High Speed Mode: SCL = 3.4MHz<br>Fast Mode: SCL = 400kHz<br>Standard Mode, SCL = 100kHz                                          |      | 8                                              | 50<br>8<br>2             |           | *                                   | *<br>*<br>*         | kHz<br>kHz<br>kHz<br>μs                     |

| AC ACCURACY Total Harmonic Distortion Signal-to-Ratio Signal-to-(Noise+Distortion) Ratio Spurious Free Dynamic Range                           | $V_{IN} = 2.5V_{PP}$ at 10kHz<br>$V_{IN} = 2.5V_{PP}$ at 10kHz<br>$V_{IN} = 2.5V_{PP}$ at 10kHz<br>$V_{IN} = 2.5V_{PP}$ at 10kHz |      | -82<br>72<br>71<br>86                          |                          |           | *<br>*<br>*                         |                     | dB <sup>(2)</sup><br>dB<br>dB<br>dB         |

| VOLTAGE REFERENCE INPUT Range Resistance Current Drain                                                                                         | All Modes<br>At Code 800H, HS Mode: SCL = 3.4MHz                                                                                 | 0.05 | 1.0<br>20                                      | V <sub>DD</sub>          | *         | *                                   | *                   | V<br>GΩ<br>μA                               |

## **ELECTRICAL CHARACTERISTICS: +5V (Cont.)**

At  $T_A = -40^{\circ}\text{C}$  to  $+85^{\circ}\text{C}$ ,  $+V_{DD} = +5.0\text{V}$ ,  $V_{REF} = +5.0\text{V}$ , SCL Clock Frequency = 3.4MHz (High Speed Mode) unless otherwise noted.

|          |                                                    |                                                     |                                | ADS7823E           |                                                  |        | ADS7823EB |        |                 |

|----------|----------------------------------------------------|-----------------------------------------------------|--------------------------------|--------------------|--------------------------------------------------|--------|-----------|--------|-----------------|

|          | PARAMETER                                          | CONDITIONS                                          | MIN                            | TYP                | MAX                                              | MIN    | TYP       | MAX    | UNITS           |

|          | DIGITAL INPUT/OUTPUT<br>Logic Family               |                                                     | CMOS                           |                    |                                                  |        | *         |        |                 |

|          | Logic Levels: V <sub>IH</sub><br>V <sub>II</sub>   |                                                     | +V <sub>DD</sub> ● 0.7<br>-0.3 |                    | +V <sub>DD</sub> + 0.5<br>+V <sub>DD</sub> • 0.3 | *<br>* |           | *<br>* | V<br>V          |

|          | V <sub>OL</sub><br>Input Leakage: ا <sub>لبا</sub> | At min 3mA Sink Current $V_{IH} = +V_{DD} +0.5$     |                                |                    | 0.4<br>10                                        |        |           | *<br>* | V<br>μ <b>A</b> |

|          | ار<br>ار<br>Data Format                            | $V_{IL} = -0.3$                                     | -10                            | Ctroimht           |                                                  | *      | *         | ,      | μΑ              |

|          | Data Format                                        |                                                     |                                | Straight<br>Binary |                                                  |        | *         |        |                 |

|          | ADS7823 HARDWARE ADDRESS                           |                                                     |                                | 10010              |                                                  |        | *         |        | Binary          |

|          | POWER SUPPLY REQUIREMENTS                          |                                                     |                                |                    |                                                  |        |           |        |                 |

|          | Power Supply Voltage, +V <sub>DD</sub>             | Specified Performance                               | 4.75                           | 5                  | 5.25                                             | *      |           | *      | V               |

|          | Quiescent Current                                  | High Speed Mode: SCL= 3.4MHz                        |                                | 0.72               | 1.0                                              |        | *         | *      | mA              |

| www.Data | Sheet/III com                                      | Fast Mode: SCL= 400kHz<br>Standard Mode, SCL=100kHz |                                | 380<br>240         |                                                  |        | *         |        | μA<br>μA        |

| www.bata | Sheet4U.com Power Dissipation                      | High Speed Mode: SCL= 3.4MHz                        |                                | 3.6                | 5.0                                              |        | *         | *      | mW              |

|          |                                                    | Fast Mode: SCL= 400kHz                              |                                | 1.9                |                                                  |        | *         |        | mW              |

|          |                                                    | Standard Mode, SCL=100kHz                           |                                | 1.2                |                                                  |        | *         |        | mW              |

|          | Powerdown Mode                                     | High Speed Mode: SCL= 3.4MHz                        |                                | 346                |                                                  |        | *         |        | μΑ              |

|          | w/Wrong Address Selected                           | Fast Mode: SCL= 400kHz                              |                                | 136                |                                                  |        | *         |        | μΑ              |

|          | Š                                                  | Standard Mode, SCL=100kHz                           |                                | 34                 |                                                  |        | *         |        | μA              |

|          | Full Powerdown                                     | SCL Pulled HIGH, SDA Pulled HIGH                    |                                | 3                  | 3000                                             |        | *         | *      | nA              |

|          | TEMPERATURE RANGE Specified Performance            |                                                     | -40                            |                    | 85                                               | *      |           | *      | °C              |

<sup>\*</sup> Specifications same as ADS7823E.

NOTES: (1) LSB means Least Significant Bit. With  $V_{REF}$  equal to 2.5V, 1LSB is  $610\mu V$ . (2) THD measured out to the 9th-harmonic.

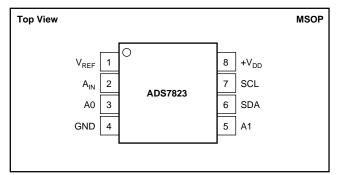

#### **PIN CONFIGURATION**

#### **PIN DESCRIPTIONS**

| PIN | NAME             | DESCRIPTION                   |  |  |  |  |

|-----|------------------|-------------------------------|--|--|--|--|

| 1   | $V_{REF}$        | Reference Input, 2.5V Nominal |  |  |  |  |

| 2   | A <sub>IN</sub>  | Analog Input.                 |  |  |  |  |

| 3   | A0               | Slave Address Bit 0           |  |  |  |  |

| 4   | GND              | Ground                        |  |  |  |  |

| 5   | A1               | Slave Address Bit 1           |  |  |  |  |

| 6   | SDA              | Serial Data                   |  |  |  |  |

| 7   | SCL              | Serial Clock                  |  |  |  |  |

| 8   | +V <sub>DD</sub> | Power Supply, 3.3V Nominal    |  |  |  |  |

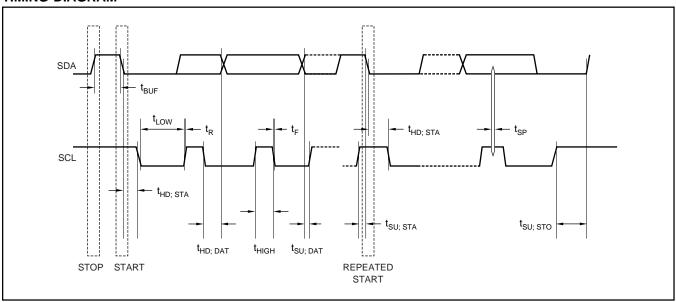

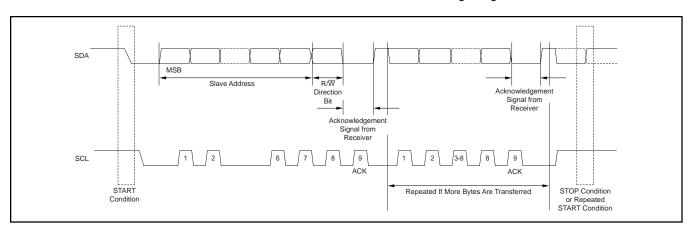

#### **TIMING DIAGRAM**

## TIMING CHARACTERISTICS(1)

At  $T_A = -40^{\circ}C$  to +85°C, +V<sub>DD</sub> = +2.7V, unless otherwise noted.

| PARAMETER                                                                                   | SYMBOL                           | CONDITIONS                                                                                                           | MIN                                           | MAX                      | UNITS                    |

|---------------------------------------------------------------------------------------------|----------------------------------|----------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|--------------------------|--------------------------|

| SCL Clock Frequency                                                                         | f <sub>SCL</sub>                 |                                                                                                                      |                                               | 100<br>400<br>3.4<br>1.7 | kHz<br>kHz<br>MHz<br>MHz |

| Bus Free Time Between a STOP and START Condition                                            | t <sub>BUF</sub>                 | Standard Mode<br>Fast Mode                                                                                           | 4.7<br>1.3                                    |                          | μs<br>μs                 |

| Hold Time (Repeated) START<br>Condition                                                     | t <sub>HD</sub> ;sta             | Standard Mode<br>Fast Mode<br>High-Speed Mode                                                                        | 4.0<br>600<br>160                             |                          | μs<br>ns<br>ns           |

| LOW Period of the SCL Clock                                                                 | t <sub>LOW</sub>                 | Standard Mode<br>Fast Mode<br>High-Speed Mode, $C_B = 100 pF max^{(2)}$<br>High-Speed Mode, $C_B = 400 pF max^{(2)}$ | 4.7<br>1.3<br>160<br>320                      |                          | μs<br>μs<br>ns<br>ns     |

| HIGH Period of the SCL Clock                                                                | t <sub>HIGH</sub>                |                                                                                                                      | 4.0<br>600<br>60<br>120                       |                          | μs<br>ns<br>ns<br>ns     |

| Setup Time for a Repeated START Condition                                                   | t <sub>SU</sub> ;sta             | Standard Mode<br>Fast Mode<br>High-Speed Mode                                                                        | 4.7<br>600<br>160                             |                          | μs<br>ns<br>ns           |

| Data Setup Time                                                                             | t <sub>SU</sub> ; <sub>DAT</sub> | Standard Mode<br>Fast Mode<br>High-Speed Mode                                                                        | 250<br>100<br>10                              |                          | ns<br>ns<br>ns           |

| Data Hold Time                                                                              | t <sub>HD</sub> ; <sub>DAT</sub> |                                                                                                                      | 0<br>0<br>0(3)<br>0(3)                        | 3.45<br>0.9<br>70<br>150 | μs<br>μs<br>ns<br>ns     |

| Rise Time of SCL Signal                                                                     | t <sub>RCL</sub>                 | Standard Mode<br>Fast Mode<br>High-Speed Mode, $C_B = 100 pF max^{(2)}$<br>High-Speed Mode, $C_B = 400 pF max^{(2)}$ | 20 + 0.1C <sub>B</sub><br>10<br>20            | 1000<br>300<br>40<br>80  | ns<br>ns<br>ns<br>ns     |

| Rise Time of SCL Signal After a<br>Repeated START Condition and<br>After an Acknowledge Bit | t <sub>RCL1</sub>                | Standard Mode<br>Fast Mode<br>High-Speed Mode, $C_B = 100 pF max^{(2)}$<br>High-Speed Mode, $C_B = 400 pF max^{(2)}$ | 20 + 0.1C <sub>B</sub><br>10<br>20            | 1000<br>300<br>80<br>160 | ns<br>ns<br>ns<br>ns     |

| Fall Time of SCL Signal                                                                     | t <sub>FCL</sub>                 |                                                                                                                      | 20 + 0.1C <sub>B</sub><br>10<br>20            | 300<br>300<br>40<br>80   | ns<br>ns<br>ns<br>ns     |

| Rise Time of SDA Signal                                                                     | t <sub>RDA</sub>                 | Standard Mode<br>Fast Mode<br>High-Speed Mode, $C_B = 100 pF max^{(2)}$<br>High-Speed Mode, $C_B = 400 pF max^{(2)}$ | 20 + 0.1C <sub>B</sub><br>10<br>20            | 1000<br>300<br>80<br>160 | ns<br>ns<br>ns<br>ns     |

| Fall Time of SDA Signal                                                                     | t <sub>FDA</sub>                 | Standard Mode<br>Fast Mode<br>High-Speed Mode, $C_B = 100 pF max^{(2)}$<br>High-Speed Mode, $C_B = 400 pF max^{(2)}$ | 20 + 0.1C <sub>B</sub><br>10<br>20            | 300<br>300<br>80<br>160  | ns<br>ns<br>ns<br>ns     |

| Setup Time for STOP Condition                                                               | t <sub>su</sub> ;sto             | Standard Mode<br>Fast Mode<br>High-Speed Mode                                                                        | 4.0<br>600<br>160                             |                          | μs<br>ns<br>ns           |

| Capacitive Load for SDA and SCL<br>Line                                                     | Св                               |                                                                                                                      |                                               | 400                      | pF                       |

| Pulse Width of Spike Suppressed                                                             | t <sub>SP</sub>                  | Fast Mode<br>High-Speed Mode                                                                                         |                                               | 50<br>10                 | ns<br>ns                 |

| Noise Margin at the HIGH Level for Each Connected Device (Including Hysteresis)             | $V_{NH}$                         | Standard Mode<br>Fast Mode<br>High-Speed Mode                                                                        | Standard Mode<br>Fast Mode 0.2V <sub>DD</sub> |                          | V                        |

| Noise Margin at the LOW Level for<br>Each Connected Device (Including<br>Hysteresis)        | $V_{NL}$                         | Standard Mode<br>Fast Mode<br>High-Speed Mode                                                                        | 0.1V <sub>DD</sub>                            |                          | V                        |

NOTES: (1) All values referred to  $V_{IHMIN}$  and  $V_{ILMAX}$  levels. (2) For bus line loads  $C_B$  between 100pF and 400pF the timing parameters must be linearly interpolated. (3) A device must internally provide a data hold time to bridge the undefined part between  $V_{IH}$  and  $V_{IL}$  of the falling edge of the SCLH signal. An input circuit with a threshold as low as possible for the falling edge of the SCLH signal minimizes this hold time.

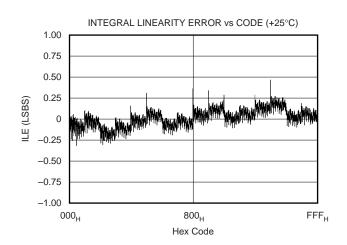

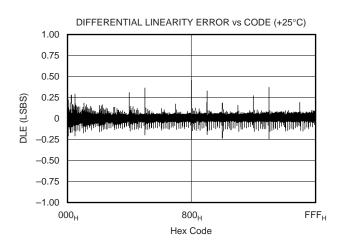

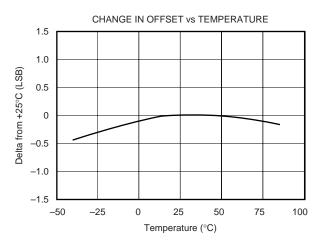

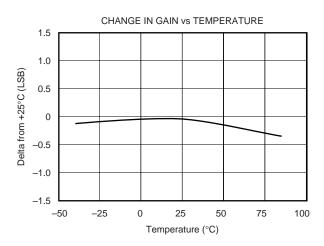

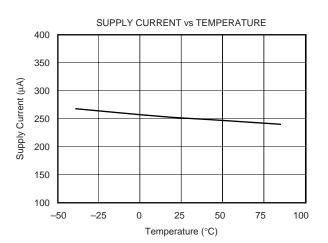

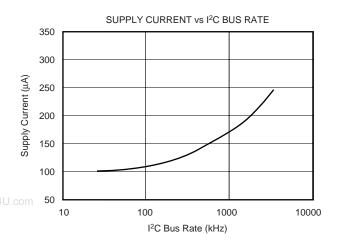

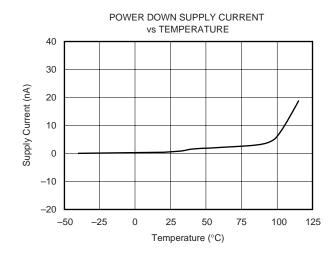

## TYPICAL CHARACTERISTICS

At  $T_A$  = +25°C, +V<sub>DD</sub> = +2.7V,  $V_{REF}$  = External +2.5V,  $f_{SAMPLE}$  = 50kHz, unless otherwise noted.

## **TYPICAL CHARACTERISTICS (Cont.)**

At  $T_A$  = +25°C, +V<sub>DD</sub> = +2.7V,  $V_{REF}$  = External +2.5V,  $f_{SAMPLE}$  = 50kHz, unless otherwise noted.

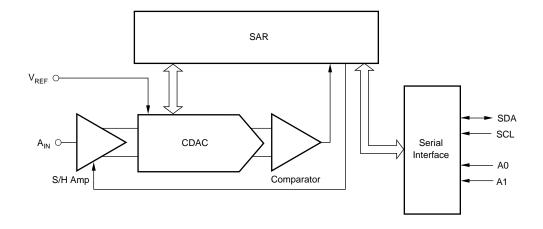

#### THEORY OF OPERATION

The ADS7823 is a classic Successive Approximation Register (SAR) A/D converter. The architecture is based on capacitive redistribution which inherently includes a sample-and-hold function. The converter is fabricated on a  $0.6\mu$  CMOS process.

The ADS7823 core is controlled by an internally-generated free-running clock. When the ADS7823 is not performing conversions or being addressed, it keeps the A/D converter core powered off, and the internal clock does not operate.

The ADS7823 has an internal 4-word first-in last-out buffer (FILO) that stores the results of up to four conversions while they are waiting to be read out over the I<sup>2</sup>C bus.

The simplified diagram of input and output for the ADS7823 is shown in Figure 1.

#### ww.DataANALOGINPUT

When the converter enters the hold mode, the voltage on the  $A_{\text{IN}}$  pin is captured on the internal capacitor array. The input current on the analog inputs depends on the conversion rate of the device. During the sample period, the source must charge the internal sampling capacitor (typically 25pF). After the capacitor has been fully charged, there is no further input current. The amount of charge transfer from the analog source to the converter is a function of conversion rate.

#### REFERENCE INPUT

The external reference sets the analog input range. The ADS7823 will operate with a reference in the range of 50mV to  $V_{DD}$ . There are several important implications of this.

As the reference voltage is reduced, the analog voltage weight of each digital output code is reduced. This is often referred to as the LSB (least significant bit) size and is equal to the reference voltage divided by 4096. This means that any offset or gain error inherent in the A/D converter will appear to increase, in terms of LSB size, as the reference voltage is reduced.

The noise inherent in the converter will also appear to increase with lower LSB size. With a 2.5V reference, the internal noise of the converter typically contributes only 0.32LSB peak-to-peak of potential error to the output code. When the external reference is 50mV, the potential error contribution from the internal noise will be 50 times larger—16LSBs. The errors due to the internal noise are Gaussian in nature and can be reduced by averaging consecutive conversion results.

#### **DIGITAL INTERFACE**

The ADS7823 supports the I<sup>2</sup>C serial bus and data transmission protocol, in all three defined modes: standard, fast, and high-speed. A device that sends data onto the bus is defined as a transmitter, and a device receiving data as a receiver.

FIGURE 1. Simplified I/O of the ADS7823.

The device that controls the message is called a "master." The devices that are controlled by the master are "slaves." The bus must be controlled by a master device that generates the serial clock (SCL), controls the bus access, and generates the START and STOP conditions. The ADS7823 operates as a slave on the I<sup>2</sup>C bus. Connections to the bus are made via the open-drain I/O lines SDA and SCL.

The following bus protocol has been defined (as shown in Figure 2):

- Data transfer may be initiated only when the bus is not busy.

- During data transfer, the data line must remain stable whenever the clock line is HIGH. Changes in the data line while the clock line is HIGH will be interpreted as control signals.

Accordingly, the following bus conditions have been defined:

Bus Not Busy: Both data and clock lines remain HIGH.

**Start Data Transfer:** A change in the state of the data line, from HIGH to LOW, while the clock is HIGH, defines a START condition.

**Stop Data Transfer:** A change in the state of the data line, from LOW to HIGH, while the clock line is HIGH, defines the STOP condition.

**Data Valid:** The state of the data line represents valid data, when, after a START condition, the data line is stable for the duration of the HIGH period of the clock signal. There is one clock pulse per bit of data.

Each data transfer is initiated with a START condition and terminated with a STOP condition. The number of data bytes transferred between START and STOP conditions is not limited and is determined by the master device. The information is transferred byte-wise and each receiver acknowledges with a ninth bit.

Within the  $I^2C$  bus specifications a standard mode (100kHz clock rate), a fast mode (400kHz clock rate), and a high-speed mode (3.4MHz clock rate) are defined. The ADS7823 works in all three modes.

**Acknowledge:** Each receiving device, when addressed, is obliged to generate an acknowledge after the reception of each byte. The master device must generate an extra clock pulse that is associated with this acknowledge bit.

A device that acknowledges must pull down the SDA line during the acknowledge clock pulse in such a way that the SDA line is stable LOW during the HIGH period of the acknowledge clock pulse. Of course, setup and hold times must be taken into account. A master must signal an end of data to the slave by not generating an acknowledge bit on the last byte that has been clocked out of the slave. In this case, the slave must leave the data line HIGH to enable the master to generate the STOP condition.

Figure 2 details how data transfer is accomplished on the  $I^2C$  bus. Depending upon the state of the  $R/\overline{W}$  bit, two types of data transfer are possible:

- Data transfer from a master transmitter to a slave receiver. The first byte transmitted by the master is the slave address. Next follows a number of data bytes. The slave returns an acknowledge bit after the slave address and each received byte.

- 2. Data transfer from a slave transmitter to a master receiver. The first byte, the slave address, is transmitted by the master. The slave then returns an acknowledge bit. Next, a number of data bytes are transmitted by the slave to the master. The master returns an acknowledge bit after all received bytes other than the last byte. At the end of the last received byte, a not-acknowledge is returned.

The master device generates all of the serial clock pulses and the START and STOP conditions. A transfer is ended with a STOP condition or a repeated START condition. Since a repeated START condition is also the beginning of the next serial transfer, the bus will not be released.

The ADS7823 may operate in the following two modes:

- Slave Receiver Mode: Serial data and clock are received through SDA and SCL. After each byte is received, an acknowledge bit is transmitted. START and STOP conditions are recognized as the beginning and end of a serial transfer. Address recognition is performed by hardware after reception of the slave address and direction bit.

- Slave Transmitter Mode: The first byte (the slave address) is received and handled as in the slave receiver mode. However, in this mode the direction bit will indicate that the transfer direction is reversed. Serial data is transmitted on SDA by the ADS7823 while the serial clock is input on SCL. START and STOP conditions are recognized as the beginning and end of a serial transfer.

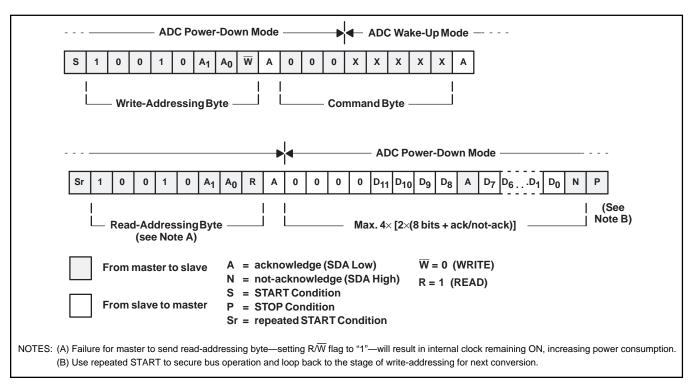

FIGURE 2. Basic Operation of the ADS7823.

#### **ADDRESS BYTE**

| MSB | 6 | 5 | 4 | 3 | 2  | 1  | LSB |

|-----|---|---|---|---|----|----|-----|

| 1   | 0 | 0 | 1 | 0 | A1 | A0 | R/W |

The address byte is the first byte received following the START condition from the master device. The first five bits (MSBs) of the slave address are factory pre-set to 10010. The next two bits of the address byte are the device select bits, A1 and A0. Input pins (A1-A0) on the ADS7823 determine these two bits of the device address for a particular ADS7823. A maximum of four devices with the same pre-set code can therefore be connected on the same bus at one time.

The A1-A0 Address Inputs can be connected to  $V_{DD}$  or digital ground. The device address is set by the state of these pins upon power-up of the ADS7823.

The last bit of the address byte  $(R/\overline{W})$  defines the operation to be performed. When set to a "1" a read operation is selected; when set to a "0" a write operation is selected. Following the START condition the ADS7823 monitors the SDA bus, checking the device type identifier being transmitted. Upon receiving the 10010 code, the appropriate device select bits, and the  $R/\overline{W}$  bit, the slave device outputs an acknowledge signal on the SDA line.

#### **COMMAND BYTE**

| MSB | 6 | 5 | 4 | 3 | 2 | 1 | LSB |

|-----|---|---|---|---|---|---|-----|

| 0   | 0 | 0 | Х | Х | Х | Х | Х   |

The ADS7823 operating mode is determined by a command byte.

The ADS7823 command byte simply consists of three zeros in the most significant bits, while the remaining 5 bits are don't cares.

#### **INITIATING CONVERSION**

Provided the master has write-addressed it, the ADS7823 turns on the A/D converter section and begins conversions when it receives bit 5 of the command byte shown in the Command Byte. If the command byte is correct, the ADS7823 will return an ACK condition.

The converter will ignore any wrong command byte (that is, setting any of the top three MSBs to 1), remain in the A/D converter power-down mode, and reset the internal 4-word stack.

The ADS7823 will ignore a second valid command byte if two valid commands are issued consecutively. The ADS7823 will respond with a not-acknowledge, and will go to the A/D converter power-down mode after the responded not-acknowledge.

FIGURE 3. Typical Read Sequence in F/S Mode.

#### **READING DATA**

Data can be read from the ADS7823 by read-addressing the part (LSB of address byte set to 1) and receiving the transmitted bytes. Converted data can only be read from the ADS7823 once a conversion has been initiated as described in the preceding section.

Each 12-bit data word is returned in two bytes, as shown below, where D11 is the MSB of the data word, and D0 is the LSB. Byte 0 is sent first, followed by Byte 1.

|       | MSB | 6  | 5  | 4  | 3   | 2   | 1  | LSB |

|-------|-----|----|----|----|-----|-----|----|-----|

| BYTE0 | 0   | 0  | 0  | 0  | D11 | D10 | D9 | D8  |

| BYTE1 | D7  | D6 | D5 | D4 | D3  | D2  | D1 | D0  |

#### **READING IN F/S MODE**

In Fast and Standard (F/S) modes, the A/D converter has time to make four complete conversions between the reception of bit 5 of the command byte and the complete reception of the read address, even when operating in Fast mode.

Because the ADS7823 can perform these conversions much faster than they can be transmitted in F/S mode, data is stored in a four-level FILO. During the read operation, the A/D converter is powered down and the contents of the stack are read out one by one in the correct order.

A typical transfer sequence for reading four words of data in F/S mode (see Figure 3). Note that the master sends a not-

acknowledge after the fourth data word has been read. This tells the ADS7823 that no further reads will be performed. No more than four data words should be read at a time; further reads will return undefined data.

Although a STOP condition is shown at the end of the figure, it is permissible to issue a repeated START; this will have the same effect.

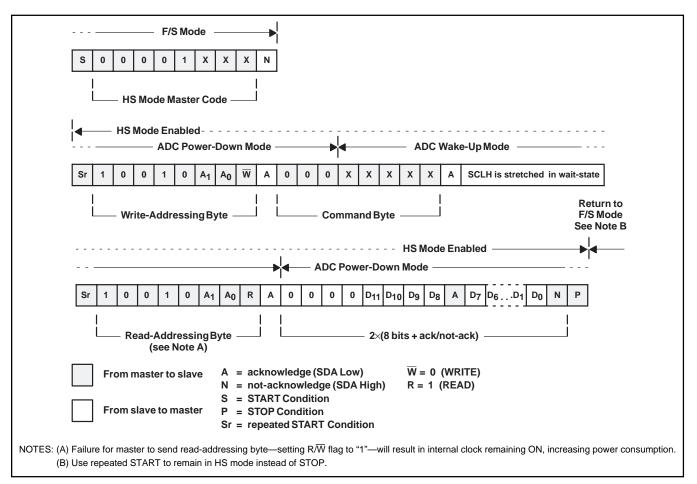

#### READING IN HS MODE

High Speed (HS) mode is fast enough that codes can be read out one at a time, without employing the FILO. In HS mode there is not enough time for a single conversion to complete between the reception of command bit 5 and the read address byte, so the ADS7823 stretches the clock after the command byte has been fully received, holding it LOW until the conversion is complete.

A typical read sequence for HS mode is shown in Figure 4. Included in the read sequence is the shift from F/S to HS modes. It may be desirable to remain in HS mode after reading a code; to do this, issue a repeated START instead of a STOP at the end of the read sequence, since a STOP causes the part to return to F/S mode.

It is very important not to read more than one code at a time from the ADS7823 during HS mode. If codes are read out more than one at a time, as in F/S mode, the results for all codes (except the first) are undefined, and the data stream will be corrupt.

FIGURE 4. Typical Read Sequence in HS Mode.

#### **TERMINATING A CONVERSION**

There are three methods to terminate the conversion of the A/D converter in the ADS7823 after the master initiates conversion:

- In normal operation sequence (see Figures 3 and 4). The conversion is terminated after the read-addressing has been received.

- A STOP condition will always terminate a conversion. It will also terminate the HS mode returning the ADS7823 to the F/S mode.

- 3) A not-acknowledge by the ADS7823 following a second command byte will end a conversion.

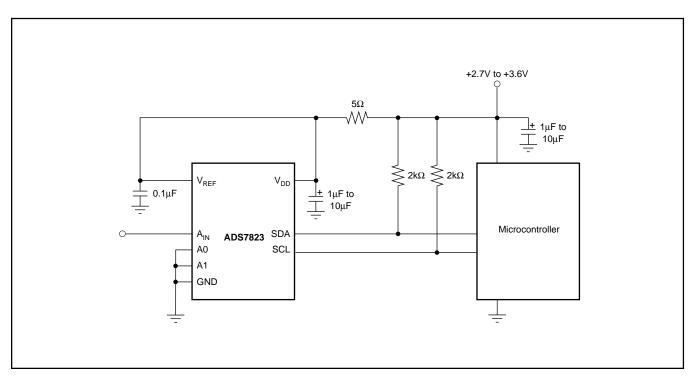

#### **LAYOUT**

For optimum performance, care should be taken with the physical dayout of the ADS7823 circuitry. The basic SAR architecture is sensitive to glitches or sudden changes on the power supply, reference, ground connections, and digital inputs that occur just prior to latching the output of the analog comparator. Therefore, during any single conversion for an "n-bit" SAR converter, there are n "windows" in which large

external transient voltages can easily affect the conversion result. Such glitches might originate from switching power supplies, nearby digital logic, and high-power devices.

With this in mind, power to the ADS7823 should be clean and well bypassed. A  $0.1\mu F$  ceramic bypass capacitor should be placed as close to the device as possible. A  $1\mu F$  to  $10\mu F$  capacitor may also be needed if the impedance of the connection between +V<sub>DD</sub> and the power supply is high.

The ADS7823 architecture offers no inherent rejection of noise or voltage variation in regards to using an external reference input. This is of particular concern when the reference input is tied to the power supply. Any noise and ripple from the supply will appear directly in the digital results. While high-frequency noise can be filtered out, voltage variation due to line frequency (50Hz or 60Hz) can be difficult to remove.

The GND pin should be connected to a clean ground point. In many cases, this will be the "analog" ground. Avoid connections that are too near the grounding point of a microcontroller or digital signal processor. The ideal layout will include an analog ground plane dedicated to the converter and associated analog circuitry.

#### PACKAGE OPTION ADDENDUM

30-Mar-2005

#### PACKAGING INFORMATION

| Orderable Device | Status <sup>(1)</sup> | Package<br>Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan <sup>(2)</sup> | Lead/Ball Finish | MSL Peak Temp <sup>(3)</sup> |

|------------------|-----------------------|-----------------|--------------------|------|----------------|-------------------------|------------------|------------------------------|

| ADS7823E/250     | ACTIVE                | MSOP            | DGK                | 8    | 250            | TBD                     | Call TI          | Level-3-260C-168 HR          |

| ADS7823E/2K5     | ACTIVE                | MSOP            | DGK                | 8    | 2500           | TBD                     | Call TI          | Level-3-260C-168 HR          |

| ADS7823EB/250    | ACTIVE                | MSOP            | DGK                | 8    | 250            | TBD                     | Call TI          | Level-3-260C-168 HR          |

| ADS7823EB/2K5    | ACTIVE                | MSOP            | DGK                | 8    | 2500           | TBD                     | Call TI          | Level-3-260C-168 HR          |

(1) The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS) or Green (RoHS & no Sb/Br) - please check http://www.ti.com/productcontent for the latest availability information and additional product content details.

TBD: The Pb-Free/Green conversion plan has not been defined.

Pb-Free (RoHS): TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes.

Green (RoHS & no Sb/Br): TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material)

(3) MSL, Peak Temp. -- The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

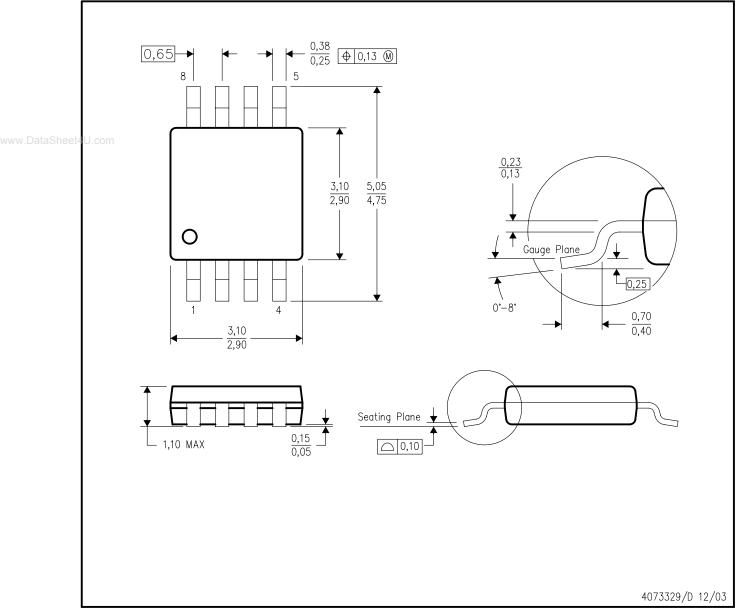

## DGK (S-PDSO-G8)

## PLASTIC SMALL-OUTLINE PACKAGE

NOTES:

- A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Body dimensions do not include mold flash or protrusion.

- D. Falls within JEDEC MO-187 variation AA.

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

| Products         |                        | Applications       |                           |

|------------------|------------------------|--------------------|---------------------------|

| Amplifiers       | amplifier.ti.com       | Audio              | www.ti.com/audio          |

| Data Converters  | dataconverter.ti.com   | Automotive         | www.ti.com/automotive     |

| DSP              | dsp.ti.com             | Broadband          | www.ti.com/broadband      |

| Interface        | interface.ti.com       | Digital Control    | www.ti.com/digitalcontrol |

| Logic            | logic.ti.com           | Military           | www.ti.com/military       |

| Power Mgmt       | power.ti.com           | Optical Networking | www.ti.com/opticalnetwork |

| Microcontrollers | microcontroller.ti.com | Security           | www.ti.com/security       |

|                  |                        | Telephony          | www.ti.com/telephony      |

|                  |                        | Video & Imaging    | www.ti.com/video          |

|                  |                        | Wireless           | www.ti.com/wireless       |

Mailing Address: Texas Instruments

Post Office Box 655303 Dallas, Texas 75265

Copyright © 2005, Texas Instruments Incorporated