## ADS7142-Q1

SBAS891A-NOVEMBER 2018-REVISED OCTOBER 2019

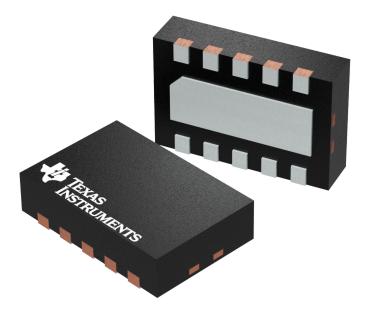

# ADS7142-Q1 Automotive, 2-Channel, 12-Bit, 140-kSPS, I<sup>2</sup>C-Compatible ADC With Programmable Threshold and Host Wake-Up Features

## 1 Features

- AEC-Q100 qualified for automotive applications:

- Device temperature grade 1: -40°C to 125°C, T<sub>A</sub>

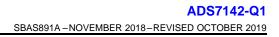

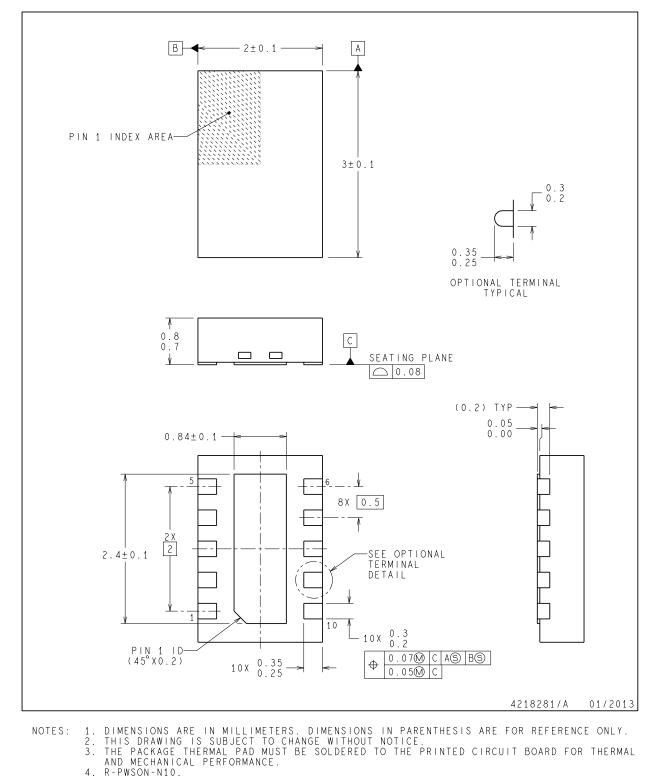

- Small package size: 3 mm × 2 mm

- 12-bit noise-free resolution

- Up to 140-kSPS sampling rate

- Efficient host sleep and wake-up:

- Autonomous monitoring at 900 nW

- Windowed comparator for event-triggered host wake-up

- Independent configuration and calibration:

- Dual-channel, pseudo-differential, or groundsense input configuration

- Programmable thresholds for calibration

- Internal calibration improves offset and drift

- False trigger prevention:

- Programmable thresholds per channel

- Programmable hysteresis for noise immunity

- Event counter for transient rejection

- I<sup>2</sup>C interface:

- Compatible from 1.65 V to 3.6 V

- 8 configurable addresses

- Up to 3.4 MHz (high speed)

- Analog supply: 1.65 V to 3.6 V

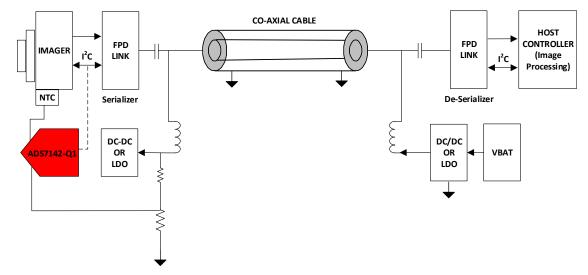

## 2 Applications

General-purpose voltage, current and temperature monitoring in:

- Automotive camera modules

- Driver monitoring and assistance systems

Support &

Community

20

- Infotainment systems and clusters

- Electric and ICE powertrain systems

## 3 Description

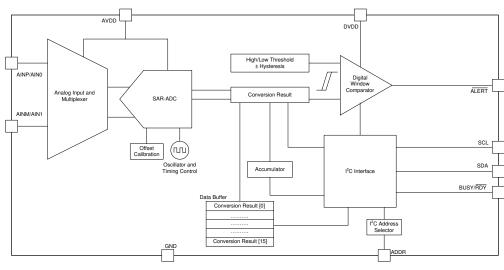

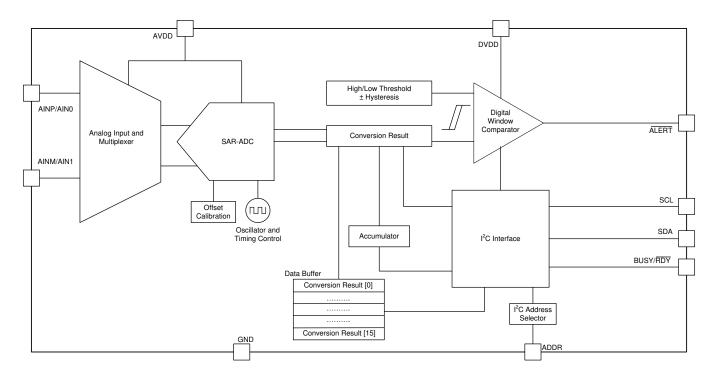

The ADS7142-Q1 is 12-bit, 140-kSPS successiveapproximation register (SAR) analog-to-digital converter (ADC) that can autonomously monitor signals while maximizing system power, reliability, and performance. The device implements eventtriggered interrupts per channel using a digital window comparator with programmable high and low thresholds, hysteresis, and event counter. The device includes a dual-channel analog multiplexer in front of a SAR ADC followed by an internal data buffer for converting and capturing data from sensors.

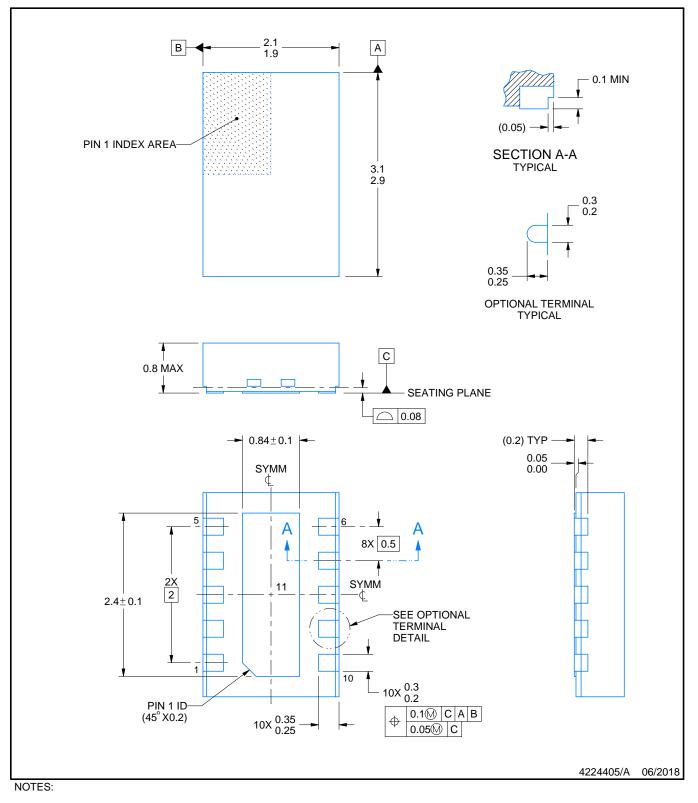

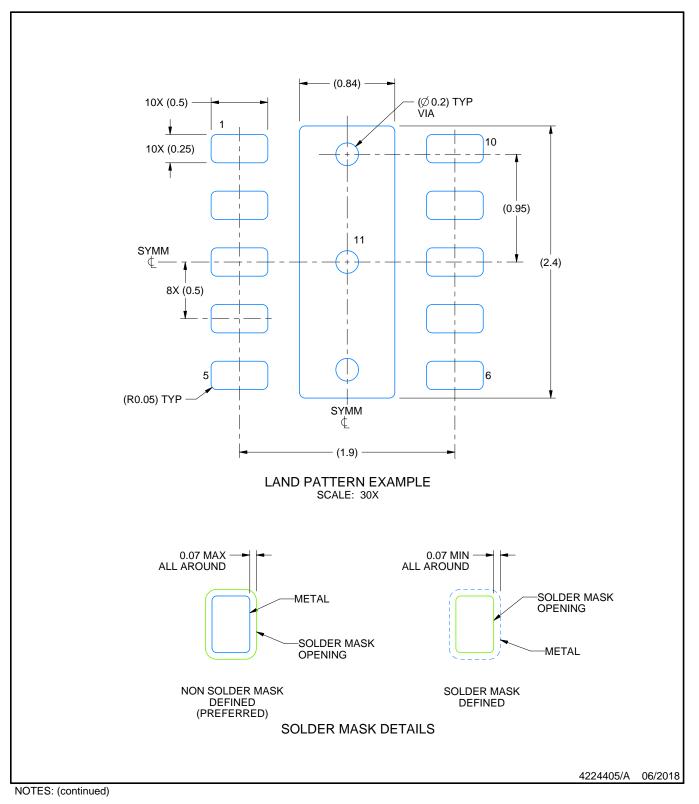

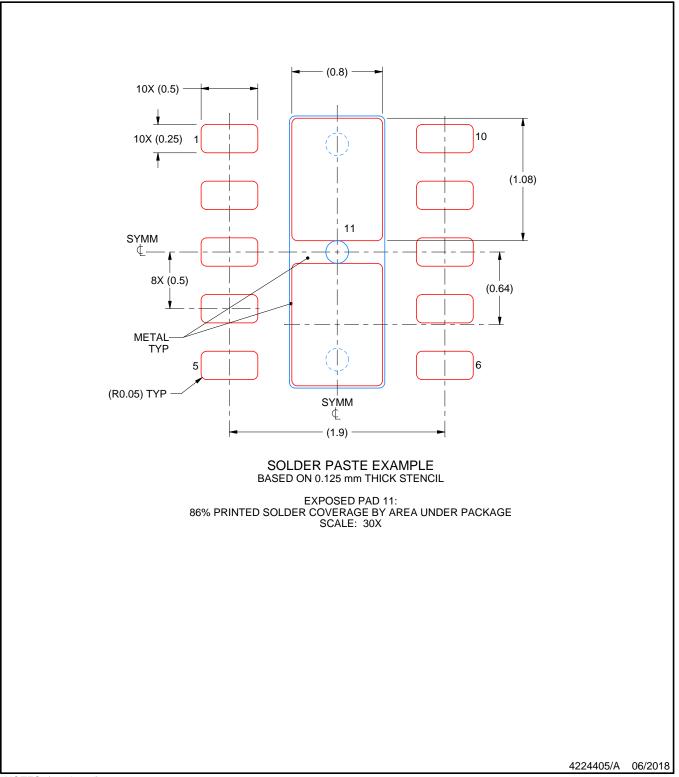

The ADS7142-Q1 is available in a 10-pin WSON package and can achieve low power consumption of only 900 nW. The small form-factor and low-power consumption make this device suitable for space-constrained applications.

## **Device Information**<sup>(1)</sup>

| PART NAME  | PACKAGE   | BODY SIZE (NOM)   |

|------------|-----------|-------------------|

| ADS7142-Q1 | WSON (10) | 3.00 mm × 2.00 mm |

(1) For all available packages, see the orderable addendum at the end of the datasheet.

## **Block Diagram**

An IMPORTANT NOTICE at the end of this data sheet addresses availability, warranty, changes, use in safety-critical applications, intellectual property matters and other important disclaimers. PRODUCTION DATA.

## **Table of Contents**

| 1 | Feat  | ures 1                                            |

|---|-------|---------------------------------------------------|

| 2 | App   | lications1                                        |

| 3 | Desc  | cription1                                         |

| 4 | Revi  | sion History 2                                    |

| 5 | Pin ( | Configuration and Functions 3                     |

| 6 | Spec  | cifications 4                                     |

|   | 6.1   | Absolute Maximum Ratings 4                        |

|   | 6.2   | ESD Ratings 4                                     |

|   | 6.3   | Recommended Operating Conditions 4                |

|   | 6.4   | Thermal Information 4                             |

|   | 6.5   | Electrical Characteristics: All Modes 5           |

|   | 6.6   | Electrical Characteristics: Manual Mode 6         |

|   | 6.7   | Electrical Characteristics: Autonomous Modes7     |

|   | 6.8   | Electrical Characteristics: High Precision Mode 8 |

|   | 6.9   | Timing Requirements 8                             |

|   | 6.10  | Switching Characteristics 10                      |

|   | 6.11  | Typical Characteristics: All Modes 12             |

|   | 6.12  | Typical Characteristics: Manual Mode 13           |

|   | 6.13  | Typical Characteristics: Autonomous Modes 17      |

|   | 6.14  | Typical Characteristics: High-Precision Mode 18   |

| 7 | Deta  | iled Description 19                               |

|   |       |                                                   |

|    | 7.1  | Overview                                        | 19        |

|----|------|-------------------------------------------------|-----------|

|    | 7.2  | Functional Block Diagram                        | 19        |

|    | 7.3  | Feature Description                             | 20        |

|    | 7.4  | Device Functional Modes                         | 28        |

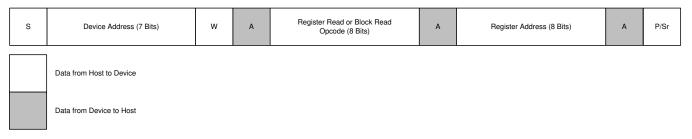

|    | 7.5  | Programming                                     |           |

|    | 7.6  | Register Map                                    | 42        |

| 8  | Арр  | lication and Implementation                     | 59        |

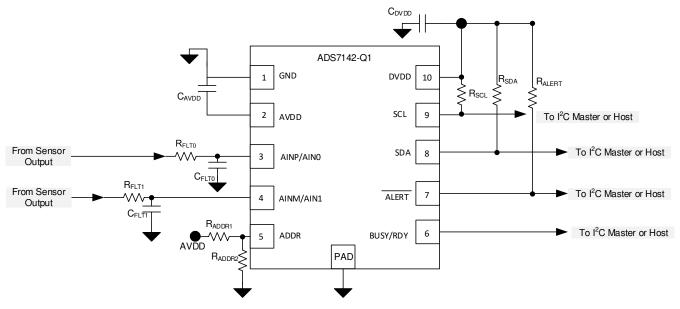

|    | 8.1  | Application Information                         | 59        |

|    | 8.2  | Typical Applications                            | 59        |

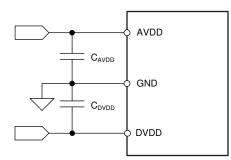

| 9  | Pow  | er Supply Recommendations                       | 65        |

|    | 9.1  | AVDD and DVDD Supply Recommendations            | 65        |

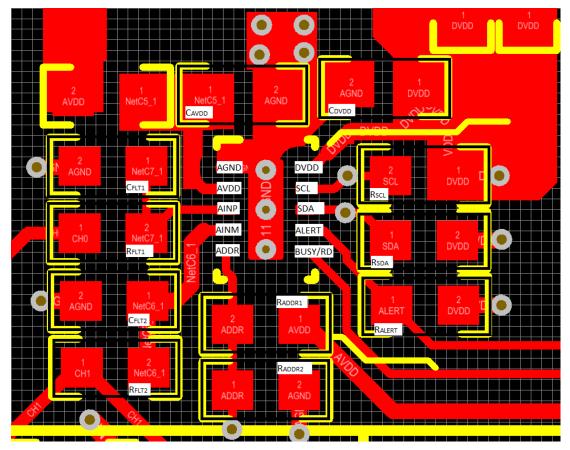

| 10 | Lay  | out                                             | 66        |

|    | 10.1 | Layout Guidelines                               |           |

|    | 10.2 | Layout Example                                  | 67        |

| 11 | Dev  | ice and Documentation Support                   | 68        |

|    | 11.1 | Receiving Notification of Documentation Updates | 68        |

|    | 11.2 | Community Resources                             | 68        |

|    | 11.3 | Trademarks                                      | <u>68</u> |

|    | 11.4 | Electrostatic Discharge Caution                 | 68        |

|    | 11.5 | Glossary                                        | 68        |

| 12 | Mec  | hanical, Packaging, and Orderable               |           |

|    |      | mation                                          | 68        |

|    |      |                                                 |           |

## 4 Revision History

| Changes from Original (November 2018) to Revision A |                                                                     |   | e |

|-----------------------------------------------------|---------------------------------------------------------------------|---|---|

| •                                                   | Changed document status from advance information to production data | 1 | 1 |

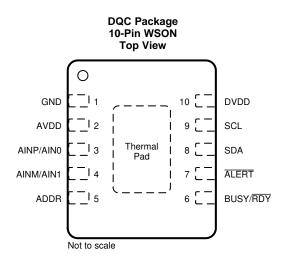

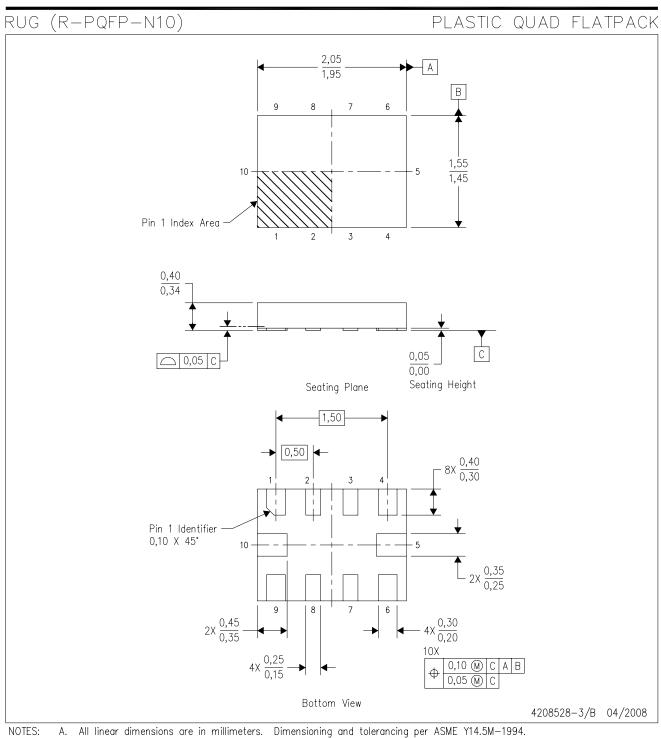

## 5 Pin Configuration and Functions

### Pin Functions

|     | PIN       | 1/0                  | DESCRIPTION                                                                                                                                                  |

|-----|-----------|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NO. | NO. NAME  |                      | DESCRIPTION                                                                                                                                                  |

| 1   | GND       | Supply               | Ground for power supply, all analog and digital signals are referred to this pin.                                                                            |

| 2   | AVDD      | Supply               | Analog supply input, also used as the reference voltage for analog-to-digital conversion.                                                                    |

| 3   | AINP/AIN0 | Analog input         | Single-channel operation: positive analog signal input.<br>Two-channel operation: analog signal input, channel 0.                                            |

| 4   | AINM/AIN1 | Analog input         | Single-channel operation: negative analog signal input.<br>Two-channel operation: analog signal input, channel 1.                                            |

| 5   | ADDR      | Analog Input         | Input for selecting the I <sup>2</sup> C address of the device.<br>See the <i>I2C Address Selection</i> section for details.                                 |

| 6   | BUSY/RDY  | Digital output       | The device pulls this pin high when scanning through channels in a sequence and brings this pin low when the sequence is completed or aborted.               |

| 7   | ALERT     | Digital output       | Active low, open-drain output. The status of this pin is controlled by the digital window comparator block. Connect a pullup resistor from DVDD to this pin. |

| 8   | SDA       | Digital input/output | Serial data input/output for the I <sup>2</sup> C interface. Connect a pullup resistor from DVDD to this pin.                                                |

| 9   | SCL       | Digital input        | Serial clock for the I <sup>2</sup> C interface. Connect a pullup resistor from DVDD to this pin.                                                            |

| 10  | DVDD      | Supply               | Digital I/O supply voltage.                                                                                                                                  |

## 6 Specifications

## 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                                             | MIN  | MAX        | UNIT |

|---------------------------------------------|------|------------|------|

| ADDR to GND                                 | -0.3 | AVDD + 0.3 | V    |

| AVDD to GND                                 | -0.3 | 3.9        | V    |

| DVDD to GND                                 | -0.3 | 3.9        | V    |

| AINP/AIN0 to GND                            | -0.3 | AVDD + 0.3 | V    |

| AINM/AIN1 to GND                            | -0.3 | AVDD + 0.3 | V    |

| Input current on any pin except supply pins | -10  | 10         | mA   |

| Digital input to GND                        | -0.3 | DVDD + 0.3 | V    |

| Junction temperature, T <sub>J</sub>        | -40  | 150        | °C   |

| Storage temperature, T <sub>stg</sub>       | -60  | 150        | °C   |

(1) Stresses beyond those listed under Absolute Maximum Rating may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Condition. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

## 6.2 ESD Ratings

|  |                                     |                                                         | VALUE          | UNIT  |  |

|--|-------------------------------------|---------------------------------------------------------|----------------|-------|--|

|  |                                     | Human-body model (HBM), per AEC Q100-002 <sup>(1)</sup> |                | ±2000 |  |

|  | Charged-device model (CDM), per AEC | Corner pins (1, 5, 6, and 10)                           | ±750           | V     |  |

|  |                                     | Q100-011                                                | All other pins | ±500  |  |

(1) AEC Q100-002 indicates that HBM stressing shall be in accordance with the ANSI/ESDA/JEDEC JS-001 specification.

## 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                |                              | MIN  | NOM MAX | UNIT |

|----------------|------------------------------|------|---------|------|

| AVDD           | Analog supply voltage range  | 1.65 | 3.6     | V    |

| DVDD           | Digital supply voltage range | 1.65 | 3.6     | V    |

| T <sub>A</sub> | Ambient temperature          | -40  | 125     | °C   |

## 6.4 Thermal Information

|                       |                                              | ADS7142-Q1 |      |

|-----------------------|----------------------------------------------|------------|------|

|                       | THERMAL METRIC <sup>(1)</sup>                | DQC (WSON) | UNIT |

|                       |                                              | 10 PINS    |      |

| $R_{	hetaJA}$         | Junction-to-ambient thermal resistance       | 61.8       | °C/W |

| $R_{\theta JC(top)}$  | Junction-to-case (top) thermal resistance    | 66.3       | °C/W |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 29.8       | °C/W |

| $\Psi_{JT}$           | Junction-to-top characterization parameter   | 2.1        | °C/W |

| $\Psi_{JB}$           | Junction-to-board characterization parameter | 29.7       | °C/W |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | 6.1        | °C/W |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

## 6.5 Electrical Characteristics: All Modes

| at T <sub>4</sub> = -40°C to 125°C | . AVDD = 3 V. DVDD = 1.6                | 5 V to 3.6 V. All Channel Configu | rations (unless otherwise noted) <sup>(1)</sup> |

|------------------------------------|-----------------------------------------|-----------------------------------|-------------------------------------------------|

| $a_A = 10001200$                   | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, |                                   |                                                 |

|                  | PARAMETER                                    | TEST CONDITIONS                                            | MIN             | TYP  | MAX       | UNIT |

|------------------|----------------------------------------------|------------------------------------------------------------|-----------------|------|-----------|------|

| ANALO            | G INPUT (Two-Channel Sin                     | gle-Ended Configuration)                                   |                 |      |           |      |

|                  | Full-scale input voltage span <sup>(1)</sup> | AINP/AIN0 to GND or AINM/AIN1 to GND                       | 0               |      | AVDD      | V    |

|                  | Absolute input voltage range                 | AINP/AIN0 to GND or AINM/AIN1 to GND                       | -0.1            | A۱   | /DD + 0.1 | V    |

| ANALO            | G INPUT (Single-Channel S                    | ingle-Ended Configuration with Remote Gro                  | und Sense)      |      |           |      |

|                  | Full-scale input voltage span <sup>(1)</sup> | AINP/AIN0 to AINM/AIN1                                     | 0               |      | AVDD      | V    |

|                  | Absolute input voltage                       | AINP/AIN0 to GND                                           | -0.1            | A۱   | /DD + 0.1 | V    |

|                  | range                                        | AINM/AIN1 to GND                                           | -0.1            |      | 0.1       | v    |

| ANALO            | G INPUT (Single-Channel F                    | seudo-Differential Configuration with Remot                | e Ground Sense) |      |           |      |

|                  | Full-scale input voltage span <sup>(1)</sup> | AINP/AIN0 to AINM/AIN1                                     | -AVDD/2         |      | AVDD/2    | V    |

|                  | Absolute input voltage                       | AINP/AIN0 to GND                                           | -0.1            | A۱   | /DD + 0.1 | V    |

|                  | range                                        | AINM/AIN1 to GND                                           | AVDD/2-0.1      | AV   | DD/2+0.1  | V    |

| INTERN           | IAL OSCILLATOR                               |                                                            |                 |      |           |      |

| t <sub>HSO</sub> | Time period for high-<br>speed oscillator    |                                                            |                 | 50   | 110       | ns   |

| t <sub>LPO</sub> | Time period for low-power oscillator         |                                                            |                 | 95.2 | 300       | μs   |

| DIGITAI          | L INPUT/OUTPUT (SCL, SD                      | A)                                                         |                 |      |           |      |

| V <sub>IH</sub>  | High-level input voltage                     |                                                            | 0.7 × DVDD      |      | DVDD      | V    |

| V <sub>IL</sub>  | Low-level input voltage                      |                                                            | 0               | 0.3  | 3 × DVDD  | V    |

|                  |                                              | With 3 mA sink current and DVDD > 2 V                      | 0               |      | 0.4       |      |

| V <sub>OL</sub>  | Low-level output voltage                     | With 3 mA sink current and 1.65 V < DVDD < 2 V             | 0               | 0.2  | 2 × DVDD  | V    |

|                  | Low-level output current                     | $V_{OL}$ = 0.4 V for standard and fast mode (100, 400 kHz) | 3               |      |           |      |

| I <sub>OL</sub>  | (sink)                                       | V <sub>OL</sub> = 0.6 V for fast mode (400 kHz)            | 6               |      |           | mA   |

|                  |                                              | $V_{OL} = 0.4$ V fast mode Plus (1 MHz)                    | 20              |      |           |      |

| I <sub>OL</sub>  | Low-level output current (sink)              | V <sub>OL</sub> = 0.4 V high speed (1.7 MHz, 3.4 MHz)      | 25              |      |           | mA   |

| l                | Input current on pin                         |                                                            |                 |      | 10        | μA   |

| CI               | Input capacitance on pin                     |                                                            |                 |      | 10        | pF   |

| DIGITA           | L OUTPUT (BUSY/RDY)                          |                                                            |                 |      |           |      |

| V <sub>ОН</sub>  | High-level output voltage                    | I <sub>source</sub> = 2 mA                                 | 0.7 × DVDD      |      | DVDD      | V    |

| V <sub>OL</sub>  | Low-level output voltage                     | I <sub>sink</sub> = 2 mA                                   | 0               | 0.3  | 3 × DVDD  | V    |

| DIGITA           | L OUTPUT (ALERT)                             |                                                            |                 |      |           |      |

| I <sub>OL</sub>  | Low-level output current                     | V <sub>OL</sub> < 0.25 V                                   |                 | 5    |           | mA   |

| V <sub>OL</sub>  | Low-level output voltage                     | I <sub>sink</sub> = 5 mA                                   | 0               |      | 0.25      | V    |

| POWER            | SUPPLY REQUIREMENTS                          |                                                            |                 |      |           |      |

| AVDD             | Analog supply voltage                        |                                                            | 1.65            |      | 3.6       | V    |

| DVDD             | Digital I/O supply voltage                   |                                                            | 1.65            |      | 3.6       | V    |

(1) Ideal Input span, does not include gain or offset error.

SBAS891A-NOVEMBER 2018-REVISED OCTOBER 2019

www.ti.com

STRUMENTS

EXAS

## 6.6 Electrical Characteristics: Manual Mode

at T<sub>A</sub> = -40°C to 125°C, AVDD = 3 V, DVDD = 1.65 V to 3.6 V, All Channel Configurations (unless otherwise noted)<sup>(1)</sup>

|                       | PARAMETER                         | TEST CONDITIONS                                                                            | MIN   | TYP   | MAX  | UNIT               |  |

|-----------------------|-----------------------------------|--------------------------------------------------------------------------------------------|-------|-------|------|--------------------|--|

| SAMPLING              | DYNAMICS                          |                                                                                            |       |       |      |                    |  |

| t <sub>conv</sub>     | Conversion time                   | AVDD = 1.65 V to 3.6 V                                                                     |       |       | 1.8  | μs                 |  |

| t <sub>acq</sub>      | Acquisition time                  | AVDD = 1.65 V to 3.6 V                                                                     |       | 18    |      | T <sub>SCL</sub>   |  |

| t <sub>cycle</sub>    | Cycle time                        | AVDD = 1.65 V to 3.6 V, SCL = 3.4 MHz                                                      |       |       | 7.1  | μs                 |  |

| DC SPECIF             | ICATIONS                          |                                                                                            |       |       |      | 1                  |  |

|                       | Resolution                        |                                                                                            |       | 12    |      | Bits               |  |

| NMC                   | No missing codes                  | AVDD = 1.65 V to 3.6 V                                                                     | 12    |       |      | Bits               |  |

| DNL                   | Differential nonlinearity         | AVDD = 1.65 V to 3.6 V                                                                     | -0.99 | ±0.3  | 1    | LSB <sup>(1)</sup> |  |

| INL                   | Integral nonlinearity             |                                                                                            | -2.75 | ±0.5  | 2.75 | LSB                |  |

| Eo                    | Offset error                      | Post offset calibration                                                                    | -4    | ±0.5  | 4    | LSB                |  |

| dV <sub>OS</sub> /dT  | Offset drift with temperature     | Post offset calibration                                                                    |       | 5     |      | ppm/°C             |  |

| E <sub>G</sub>        | Gain error                        |                                                                                            | -0.1  | ±0.03 | 0.1  | %FSR               |  |

| -                     | Gain error drift with temperature |                                                                                            |       | 5     |      | ppm/°C             |  |

| AC SPECIF             | FICATIONS                         | 1                                                                                          |       |       |      | I                  |  |

| (0)                   |                                   | f <sub>IN</sub> = 2 kHz, AVDD = 3 V,<br>f <sub>SAMPLE</sub> = 140 kSPS                     | 68.75 | 70    |      |                    |  |

| SNR <sup>(2)</sup>    | Signal-to-noise ratio             | $f_{IN} = 2 \text{ kHz}, \text{ AVDD} = 1.8 \text{ V},$<br>$f_{SAMPLE} = 140 \text{ kSPS}$ |       | 68    |      | dB                 |  |

|                       |                                   | $f_{IN} = 2 \text{ kHz}, \text{ AVDD} = 3 \text{ V},$<br>$f_{SAMPLE} = 140 \text{ kSPS}$   |       | -85   |      |                    |  |

| THD <sup>(2)(3)</sup> | Total harmonic distortion         | $f_{IN} = 2 \text{ kHz}, \text{ AVDD} = 1.8 \text{ V},$<br>$f_{SAMPLE} = 140 \text{ kSPS}$ |       | -80   |      | dB                 |  |

| SINAD <sup>(2)</sup>  |                                   | f <sub>IN</sub> = 2 kHz, AVDD = 3 V,<br>f <sub>SAMPLE</sub> = 140 kSPS                     | 68.5  | 69.5  |      |                    |  |

| SINAD -/              | Signal-to-noise and distortion    | f <sub>IN</sub> = 2 kHz, AVDD = 1.8 V,<br>f <sub>SAMPLE</sub> = 140 kSPS                   |       | 67.5  |      | dB                 |  |

| SFDR <sup>(2)</sup>   | Spurious-free dynamic range       | f <sub>IN</sub> = 2 kHz, AVDD = 3 V,<br>f <sub>SAMPLE</sub> = 140 kSPS                     |       | 90    |      | dB                 |  |

| BW                    | -3-dB small-signal bandwidth      |                                                                                            |       | 25    |      | MHz                |  |

| POWER CO              | DNSUMPTION                        |                                                                                            |       |       |      |                    |  |

|                       |                                   | f <sub>SAMPLE</sub> = 140 kSPS, SCL = 3.4 MHz                                              |       | 265   | 300  |                    |  |

|                       |                                   | f <sub>SAMPLE</sub> = 5.5 kSPS, SCL = 100 kHz                                              |       | 8     |      |                    |  |

| I <sub>AVDD</sub>     | Analog supply current             | $f_{SAMPLE}$ = 140 kSPS, SCL = 3.4 MHz, AVDD<br>= 1.8 V                                    |       | 160   |      | μA                 |  |

|                       |                                   | $f_{SAMPLE}$ = 5.5 kSPS, SCL = 100 kHz, AVDD<br>= 1.8 V                                    |       | 5     |      |                    |  |

|                       |                                   | $f_{SAMPLE}$ = 140 kSPS, SCL = 3.4 MHz, SDA = AAA0h                                        |       | 25    |      |                    |  |

| I <sub>DVDD</sub>     | Digital supply current            | $f_{SAMPLE} = 5.5 \text{ kSPS}, \text{ SCL} = 100 \text{ kHz}, \text{ SDA} = AAA0h$        |       | 2     |      | μA                 |  |

|                       |                                   | $f_{SAMPLE}$ = 140 kSPS, SCL = 3.4 MHz, AVDD<br>= 1.8 V, SDA = AAA0h                       |       | 15    |      |                    |  |

| I <sub>AVDD</sub>     | Static analog supply current      | No activity on SCL and SDA                                                                 |       | 6     |      | nA                 |  |

| I <sub>DVDD</sub>     | Static digital supply current     | No activity on SCL and SDA                                                                 |       | 2     |      | nA                 |  |

(1) LSB means least significant byte. See the ADC Transfer Function for details.

(2) All specifications expressed in decibels (dB) refer to the full-scale input (FSR) and are tested with an input signal 0.5 dB below full-scale, unless otherwise specified.

(3) Calculated on the first nine harmonics of the input frequency.

## 6.7 Electrical Characteristics: Autonomous Modes

at T<sub>A</sub> = -40°C to 125°C, AVDD = 3 V, DVDD = 1.65 V to 3.6 V, All Channel Configurations (unless otherwise noted)

|                    | PARAMETER                     | TEST CONDITIONS                                               | MIN | TYP   | MAX | UNIT             |

|--------------------|-------------------------------|---------------------------------------------------------------|-----|-------|-----|------------------|

| SAMPI              | ING DYNAMICS                  |                                                               |     |       |     | I                |

|                    | Conversion time               | High-speed oscillator                                         |     | 14    |     | t <sub>HSO</sub> |

| t <sub>conv</sub>  | Conversion time               | Low-power oscillator                                          |     | 14    |     | t <sub>LPO</sub> |

| t <sub>acq</sub>   |                               | High-speed oscillator                                         | 7   |       |     | t <sub>HSO</sub> |

|                    | Acquisition time              | Low-power oscillator                                          | 4   |       |     | t <sub>LPO</sub> |

| +                  | Cycle time                    | High-speed oscillator                                         |     | nCLK  |     | t <sub>HSO</sub> |

| t <sub>cycle</sub> | Cycle time                    | Low-power oscillator                                          |     | nCLK  |     | t <sub>LPO</sub> |

| DC SP              | ECIFICATIONS                  |                                                               |     |       |     |                  |

|                    | Resolution                    |                                                               |     | 12    |     | Bits             |

| Eo                 | Offset error                  | Post offset calibration                                       |     | ±0.5  |     | LSB              |

| E <sub>G</sub>     | Gain error                    |                                                               |     | ±0.03 |     | %FSR             |

| POWE               | R CONSUMPTION                 |                                                               |     |       |     |                  |

| IAVDD              |                               | With low-power oscillator, nCLK = 18                          |     | 0.75  |     |                  |

|                    | Analog supply current         | With low-power oscillator, AVDD = 1.8 V, nCLK = 18            |     | 0.45  |     | μΑ               |

|                    |                               | With low-power oscillator, nCLK = 250                         |     | 0.5   |     |                  |

|                    |                               | With low-power oscillator, nCLK = 21                          |     | 940   |     |                  |

| I <sub>DVDD</sub>  | Digital supply current        | With low-power oscillator, nCLK = 18, DVDD = $3.3 \text{ V}$  |     | 0.15  |     |                  |

|                    |                               | With low-power oscillator, DVDD = 1.8 V, nCLK = 18            |     | 0.25  |     |                  |

|                    |                               | With low-power oscillator, nCLK = 250, DVDD = $3.3 \text{ V}$ |     | 0.15  |     | μA               |

|                    |                               | With high-power oscillator, nCLK = 21, DVDD = $3.3 \text{ V}$ |     | 0.15  |     |                  |

| I <sub>AVDD</sub>  | Static analog supply current  | No activity on SCL and SDA                                    |     | 5     |     | nA               |

| I <sub>DVDD</sub>  | Static digital supply current | No activity on SCL and SDA                                    |     | 0.6   |     | nA               |

SBAS891A-NOVEMBER 2018-REVISED OCTOBER 2019

www.ti.com

RUMENTS

AS

## 6.8 Electrical Characteristics: High Precision Mode

at T<sub>A</sub> = -40°C to 125°C, AVDD = 3 V, DVDD = 1.65 V to 3.6 V, All Channel Configurations (unless otherwise noted)<sup>(1)</sup>

|                   | PARAMETER                    | TEST CONDITIONS                                        | MIN | TYP   | MAX | UNIT |

|-------------------|------------------------------|--------------------------------------------------------|-----|-------|-----|------|

| DC SPE            | ECIFICATIONS                 |                                                        |     |       | l   |      |

|                   | Resolution <sup>(2)</sup>    |                                                        |     | 16    |     | Dite |

| ENOB              | Effective number of bits     | With DC input of AVDD / 2 <sup>(3)</sup>               |     | 15.4  |     | Bits |

| Eo                | Offset error                 | Post offset calibration                                |     | ±10   |     | LSB  |

| E <sub>G</sub>    | Gain error                   |                                                        |     | ±0.03 |     | %FSR |

| POWER             | CONSUMPTION                  |                                                        |     |       |     |      |

|                   |                              | With low-power oscillator, nCLK = 18                   |     | 0.6   |     |      |

| I <sub>AVDD</sub> | Analog supply current        | With low-power oscillator, AVDD = 1.8 V, nCLK = 18     |     | 0.3   |     | μΑ   |

|                   |                              | With low-power oscillator, nCLK = 250                  |     | 0.5   |     |      |

|                   |                              | With high-speed oscillator, nCLK = 21                  |     | 980   |     |      |

| I <sub>DVDD</sub> | Digital supply current       | With low-power oscillator, nCLK = 21, DVDD<br>= 3.3 V  |     | 0.2   |     |      |

|                   |                              | With low-power oscillator, DVDD = 1.8 V, nCLK = 21     |     | 0.25  |     |      |

|                   |                              | With low-power oscillator, nCLK = 250,<br>DVDD = 3.3 V |     | 0.2   |     | μA   |

|                   |                              | With high-speed oscillator, nCLK = 21, DVDD = $3.3$ V  |     | 0.2   |     |      |

| I <sub>AVDD</sub> | Static analog supply current | No activity on SCL and SDA                             |     | 5     |     | nA   |

| I <sub>DVDD</sub> | Static analog supply current | No activity on SCL and SDA                             |     | 0.7   |     | nA   |

Sampling dynamics for high precision mode are same as for autonomous modes. (1)

(2) See Equation 5

(3) For DC input, ENOB = Ln[FSR/Standard deviation of Codes]/Ln[2]. See

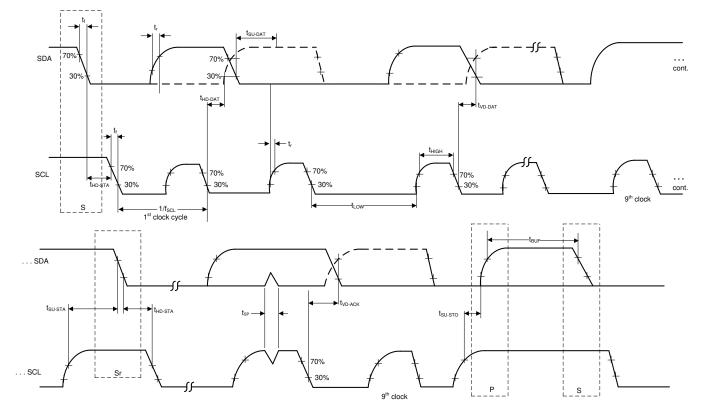

## 6.9 Timing Requirements

at  $T_A = -40^{\circ}$ C to 125°C, AVDD = 3 V, DVDD = 1.65 V to 3.6 V, All Channel Configurations (unless otherwise noted)<sup>(1)</sup>

|                                       | PARAMETER                                        | MIN | MAX | UNIT |  |  |  |

|---------------------------------------|--------------------------------------------------|-----|-----|------|--|--|--|

| STANDARD MC                           | STANDARD MODE (100 kHz)                          |     |     |      |  |  |  |

| f <sub>SCL</sub>                      | SCL clock frequency                              | 0   | 100 | kHz  |  |  |  |

| t <sub>HD-STA</sub>                   | Hold time (repeated) START condition             | 4   |     | μs   |  |  |  |

| t <sub>LOW</sub>                      | Low period of SCL                                | 4.7 |     | μs   |  |  |  |

| t <sub>HIGH</sub>                     | High period of SCL                               | 4   |     | μs   |  |  |  |

| t <sub>SU-STA</sub>                   | Setup time for a repeated start condition        | 4.7 |     | μs   |  |  |  |

| t <sub>HD-DAT</sub> <sup>(2)(3)</sup> | Data hold time                                   | 0   |     | μs   |  |  |  |

| t <sub>SU-DAT</sub>                   | Data setup time                                  | 250 |     | ns   |  |  |  |

| t <sub>SU-STO</sub>                   | Data setup time                                  | 4   |     | μs   |  |  |  |

| t <sub>BUF</sub>                      | Bus free time between a STOP and START condition | 4.7 |     | μs   |  |  |  |

| C <sub>b</sub>                        | Capacitive load on each line                     |     | 400 | pF   |  |  |  |

| FAST MODE (40                         | 00 kHz)                                          |     |     |      |  |  |  |

| f <sub>SCL</sub>                      | SCL clock frequency                              | 0   | 400 | kHz  |  |  |  |

| t <sub>HD-STA</sub>                   | Hold time (repeated) START condition             | 0.6 |     | μs   |  |  |  |

| t <sub>LOW</sub>                      | Low period of SCL                                | 1.3 |     | μs   |  |  |  |

| t <sub>HIGH</sub>                     | High period of SCL                               | 0.6 |     | μs   |  |  |  |

All values referred to V<sub>IH(min)</sub> (0.7 DVDD) and V<sub>IL(max)</sub> (0.3 DVDD).

t<sub>HD-DAT</sub> is the data hold time that is measured from the falling edge of SCL and applies to data in transmission and the acknowledge.

The maximum t<sub>HD-DAT</sub> can be 3.45 µs and 0.9 µs for standard-mode and fast-mode, but must be less than the maximum of t<sub>VD-DAT</sub> or t<sub>VD-ACK</sub> by a transition time. This maximum must only be met if the device does not stretch the LOW period (t<sub>LOW</sub>) of the SCL signal. If the clock is streched, the data must be valid by the setup time before being released.

## **Timing Requirements (continued)**

| at T <sub>≜</sub> = -40°C to 125°C. | AVDD = 3 V, DVDD = 1.65 V to 3.6 V | All Channel Configurations | (unless otherwise noted) <sup>(1)</sup> |

|-------------------------------------|------------------------------------|----------------------------|-----------------------------------------|

| a = 10001200                        | 1000 = 01, 0100 = 100100001        |                            |                                         |

|                     | PARAMETER                                        | MIN  | MAX  | UNIT |

|---------------------|--------------------------------------------------|------|------|------|

| t <sub>SU-STA</sub> | Setup time for a repeated start condition        | 0.6  |      | μs   |

| t <sub>HD-DAT</sub> | Data hold time                                   | 0    |      | μs   |

| t <sub>SU-DAT</sub> | Data setup time                                  | 100  |      | ns   |

| t <sub>SU-STO</sub> | Data setup time                                  | 0.6  |      | μs   |

| t <sub>BUF</sub>    | Bus free time between a STOP and START condition | 1.3  |      | μs   |

| C <sub>b</sub>      | Capacitive load on each line                     |      | 400  | pF   |

| FAST MODE I         | PLUS (1000 kHz)                                  |      |      |      |

| f <sub>SCL</sub>    | SCL clock frequency                              | 0    | 1000 | kHz  |

| t <sub>HD-STA</sub> | Hold time (repeated) START condition             | 0.26 |      | μs   |

| t <sub>LOW</sub>    | Low period of SCL                                | 0.5  |      | μs   |

| t <sub>HIGH</sub>   | High period of SCL                               | 0.26 |      | μs   |

| t <sub>SU-STA</sub> | Setup time for a repeated start condition        | 0.26 |      | μs   |

| t <sub>HD-DAT</sub> | Data hold time                                   | 0    |      | μs   |

| t <sub>SU-DAT</sub> | Data setup time                                  | 50   |      | ns   |

| t <sub>su-sто</sub> | Data setup time                                  | 0.26 |      | μs   |

| t <sub>BUF</sub>    | Bus free time between a STOP and START condition | 0.5  |      | μs   |

| C <sub>b</sub>      | Capacitive load on each line                     |      | 550  | pF   |

| HIGH SPEED          | MODE (1.7 MHz, C <sub>b</sub> = 400 pF max)      |      |      |      |

| f <sub>SCLH</sub>   | SCLH clock frequency                             | 0    | 1.7  | MHz  |

| t <sub>HD-STA</sub> | Hold time (repeated) START condition             | 160  |      | ns   |

| t <sub>LOW</sub>    | Low period of SCL                                | 320  |      | ns   |

| t <sub>ніGH</sub>   | High period of SCL                               | 120  |      | ns   |

| t <sub>SU-STA</sub> | Setup time for a repeated start condition        | 160  |      | ns   |

| t <sub>HD-DAT</sub> | Data hold time                                   | 0    | 150  | ns   |

| t <sub>SU-DAT</sub> | Data setup time                                  | 10   |      | ns   |

| t <sub>su-sто</sub> | Data setup time                                  | 160  |      | ns   |

| C <sub>b</sub>      | Capacitive load on each line                     |      | 100  | pF   |

| HIGH SPEED          | MODE (3.4 MHz, C <sub>b</sub> = 100 pF max)      |      |      |      |

| f <sub>SCLH</sub>   | SCLH clock frequency                             | 0    | 3.4  | MHz  |

| t <sub>HD-STA</sub> | Hold time (repeated) START condition             | 160  |      | ns   |

| t <sub>LOW</sub>    | Low period of SCL                                | 160  |      | ns   |

| t <sub>HIGH</sub>   | High period of SCL                               | 60   |      | ns   |

| t <sub>SU-STA</sub> | Setup time for a repeated start condition        | 160  |      | ns   |

| t <sub>HD-DAT</sub> | Data hold time                                   | 0    | 70   | ns   |

| t <sub>SU-DAT</sub> | Data setup time                                  | 10   |      | ns   |

| t <sub>SU-STO</sub> | Data setup time                                  | 160  |      | ns   |

| C <sub>b</sub>      | Capacitive load on each line                     |      | 100  | pF   |

SBAS891A-NOVEMBER 2018-REVISED OCTOBER 2019

ISTRUMENTS

**EXAS**

## 6.10 Switching Characteristics

at T<sub>A</sub> = -40°C to 125°C, AVDD = 3 V, DVDD = 1.65 V to 3.6 V, All Channel Configurations (unless otherwise noted)<sup>(1)</sup>

|                                    | PARAMETER                                                                       | TEST CONDITIONS                          | MIN           | MAX         | UNIT |

|------------------------------------|---------------------------------------------------------------------------------|------------------------------------------|---------------|-------------|------|

| STANDARD                           | ) MODE (100 kHz)                                                                |                                          |               |             |      |

| t <sub>rCL</sub>                   | Rise time of SCL                                                                |                                          |               | 1000        | ns   |

| t <sub>rDA</sub>                   | Rise time of SDA                                                                |                                          |               | 1000        | ns   |

| fCL                                | Fall time of SCL                                                                |                                          |               | 300         | ns   |

| t <sub>fDA</sub>                   | Fall time of SDA                                                                |                                          |               | 300         | ns   |

| t <sub>VD-DAT</sub> <sup>(2)</sup> | Data valid time                                                                 |                                          |               | 3.45        | μs   |

| t <sub>VD-ACK</sub> <sup>(2)</sup> | Data hold time                                                                  |                                          |               | 3.45        | μs   |

| FAST MOD                           | E (400 kHz)                                                                     |                                          |               |             |      |

| t <sub>rCL</sub>                   | Rise time of SCL                                                                |                                          | 20            | 300         | ns   |

| t <sub>rDA</sub>                   | Rise time of SDA                                                                |                                          | 20            | 300         | ns   |

| fCL                                | Fall time of SCL                                                                |                                          | 20 × DVDD/3.6 | 300         | ns   |

| t <sub>fDA</sub>                   | Fall time of SDA                                                                |                                          | 20 × DVDD/3.6 | 300         | ns   |

| t <sub>VD-DAT</sub>                | Data valid time                                                                 |                                          |               | 0.9         | μs   |

| t <sub>VD-ACK</sub>                | Data hold time                                                                  |                                          |               | 0.9         | μs   |

| t <sub>SP</sub> <sup>(3)</sup>     | Pulse duration of spikes suppressed by the input filter                         |                                          | 0             | 50          | ns   |

| FAST MOD                           | E PLUS (1000 kHz)                                                               |                                          |               | · · · · · · |      |

| t <sub>rCL</sub>                   | Rise time of SCL                                                                |                                          |               | 120         | ns   |

| t <sub>rDA</sub>                   | Rise time of SDA                                                                |                                          |               | 120         | ns   |

| t <sub>fCL</sub>                   | Fall time of SCL                                                                |                                          | 20 × DVDD/3.6 | 120         | ns   |

| t <sub>fDA</sub>                   | Fall time of SDA                                                                |                                          | 20 × DVDD/3.6 | 120         | ns   |

| t <sub>VD-DAT</sub>                | Data valid time                                                                 |                                          |               | 0.45        | μs   |

| t <sub>VD-ACK</sub>                | Data hold time                                                                  |                                          |               | 0.45        | μs   |

| t <sub>SP</sub>                    | Pulse duration of spikes suppressed by the input filter                         |                                          | 0             | 50          | ns   |

| HIGH SPEE                          | D MODE (1.7 MHz, C <sub>b</sub> = 400 pF max)                                   | I <u> </u>                               |               | I           |      |

| t <sub>rCL</sub>                   | Rise time of SCLH                                                               |                                          | 20            | 80          | ns   |

| t <sub>rCL1</sub>                  | Rise time of SCLH after a repeated start condition and after an acknowledge bit |                                          | 20            | 160         | ns   |

| t <sub>rDA</sub>                   | Rise time of SDAH                                                               |                                          | 20            | 160         | ns   |

| t <sub>fCL</sub>                   | Fall time of SCLH                                                               |                                          | 20            | 80          | ns   |

| t <sub>fDA</sub>                   | Fall time of SDAH                                                               |                                          | 20            | 160         | ns   |

| t <sub>SP</sub>                    | Pulse duration of spikes suppressed by the input filter                         |                                          | 0             | 10          | ns   |

| HIGH SPEE                          | D MODE (3.4 MHz, C <sub>b</sub> = 100 pF max)                                   | Ч. – – – – – – – – – – – – – – – – – – – |               |             |      |

| t <sub>rCL</sub>                   | Rise time of SCLH                                                               |                                          | 10            | 40          | ns   |

| t <sub>rCL1</sub>                  | Rise time of SCLH after a repeated start condition and after an acknowledge bit |                                          | 10            | 80          | ns   |

| t <sub>rDA</sub>                   | Rise time of SDAH                                                               |                                          | 10            | 80          | ns   |

| t <sub>fCL</sub>                   | Fall time of SCLH                                                               |                                          | 10            | 40          | ns   |

| t <sub>fDA</sub>                   | Fall time of SDAH                                                               |                                          | 10            | 80          | ns   |

| t <sub>SP</sub>                    | Pulse duration of spikes suppressed by the input filter                         |                                          | 0             | 10          | ns   |

|                                    | 1                                                                               |                                          |               |             |      |

Copyright © 2018–2019, Texas Instruments Incorporated

$\begin{array}{l} V_{IL}=0.3V_{DD}\\ V_{IH}=0.7V_{DD} \end{array}$

Figure 1. Timing Diagram for Standard Mode, Fast Mode, and Fast Mode Plus

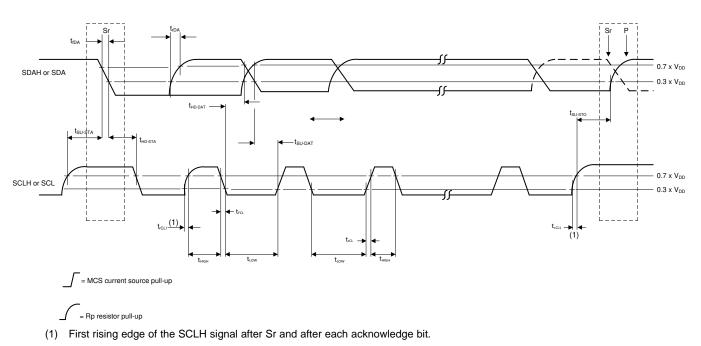

## Figure 2. Timing Diagram for High-Speed Mode

12 Submit Documentation Feedback

### ADS7142-Q1

SBAS891A-NOVEMBER 2018-REVISED OCTOBER 2019

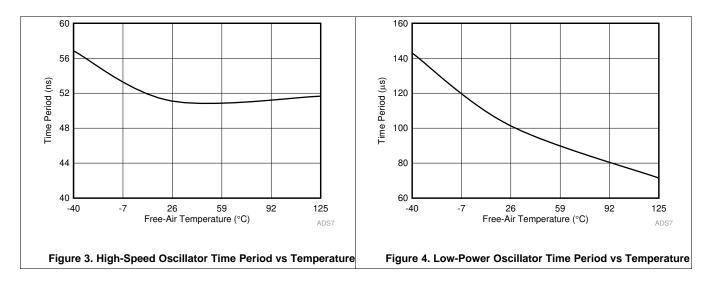

## 6.11 Typical Characteristics: All Modes

at  $T_A = 25^{\circ}C$ , AVDD = 3 V, DVDD = 3.3 V, and two-channel single-ended configuration (unless otherwise noted)

www.ti.com

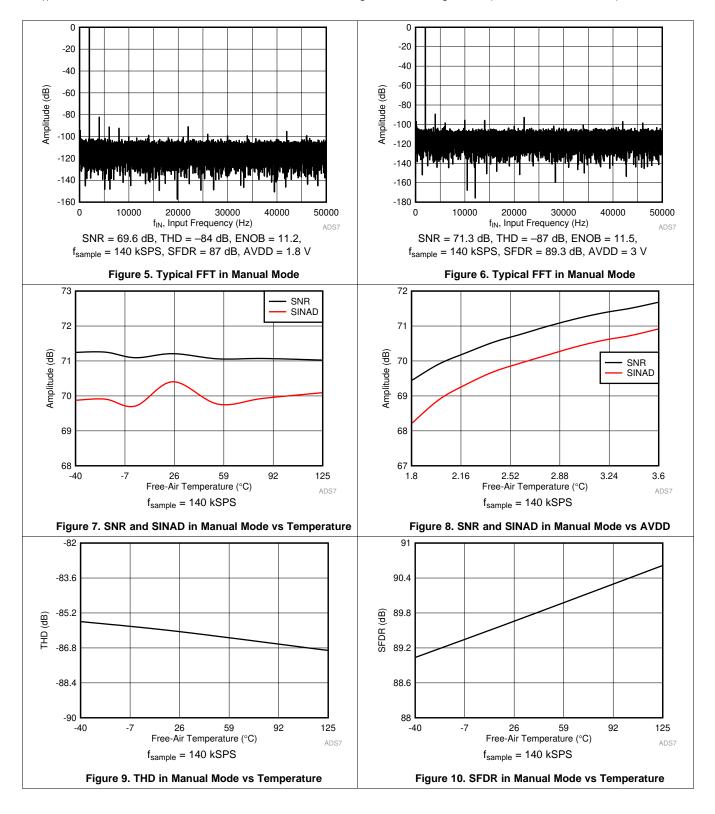

## 6.12 Typical Characteristics: Manual Mode

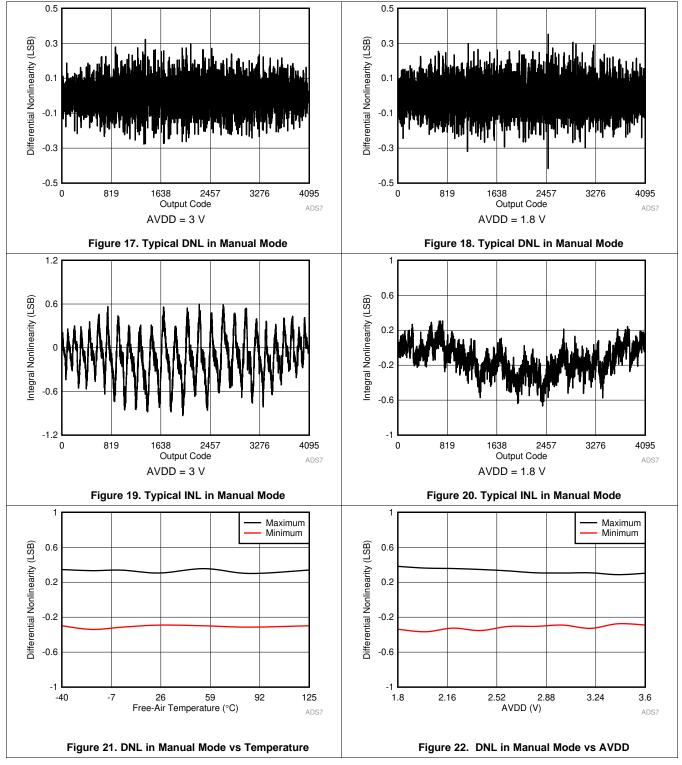

at T<sub>A</sub> = 25°C, AVDD = 3 V, DVDD = 3.3 V, and two-channel single-ended configuration (unless otherwise noted)

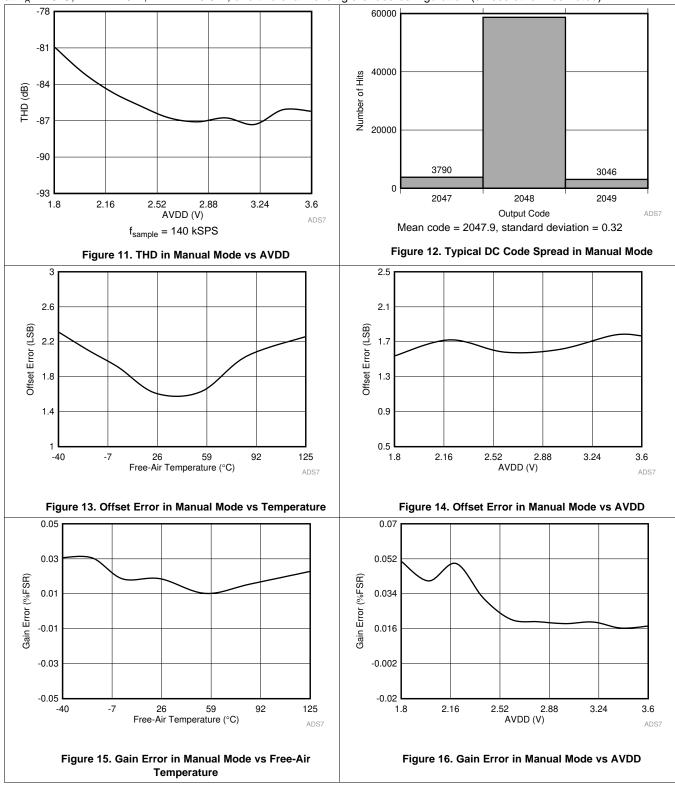

## Typical Characteristics: Manual Mode (continued)

at T<sub>A</sub> = 25°C, AVDD = 3 V, DVDD = 3.3 V, and two-channel single-ended configuration (unless otherwise noted)

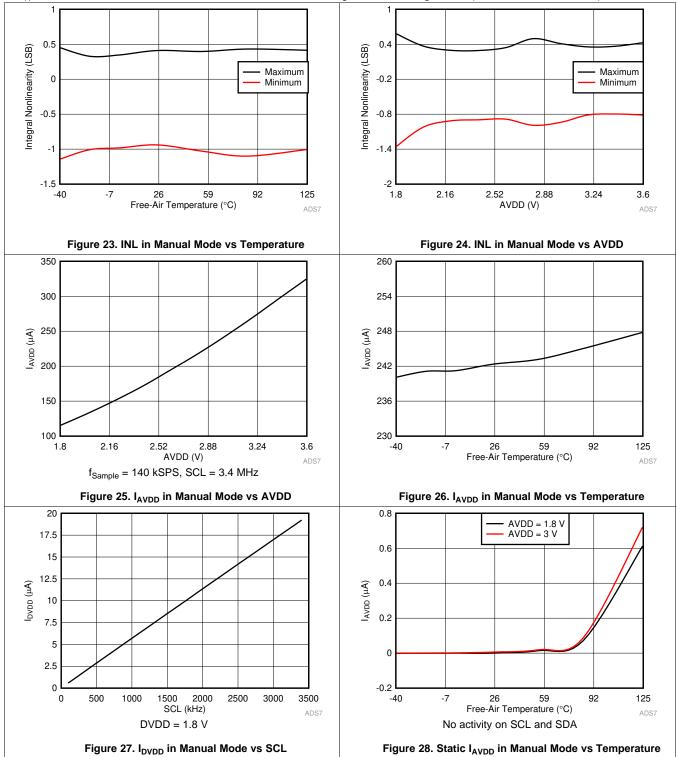

## Typical Characteristics: Manual Mode (continued)

## Typical Characteristics: Manual Mode (continued)

at T<sub>A</sub> = 25°C, AVDD = 3 V, DVDD = 3.3 V, and two-channel single-ended configuration (unless otherwise noted)

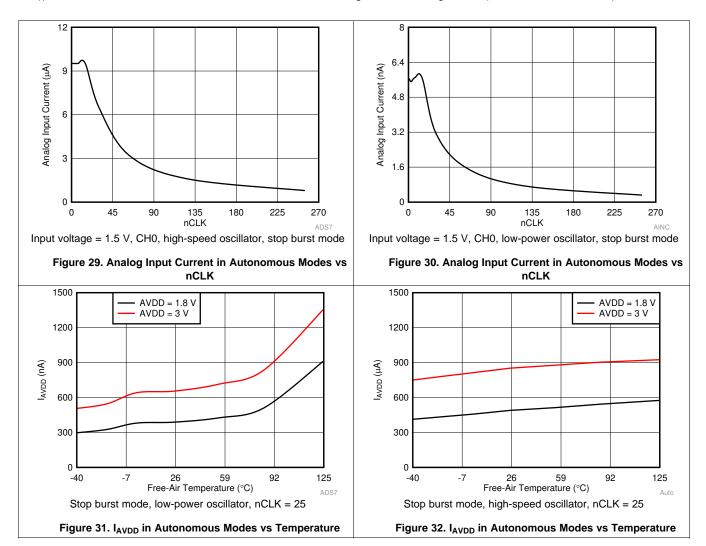

## 6.13 Typical Characteristics: Autonomous Modes

at T<sub>A</sub> = 25°C, AVDD = 3 V, DVDD = 3.3 V, and two-channel single-ended configuration (unless otherwise noted)

TEXAS INSTRUMENTS

www.ti.com

### ADS7142-Q1

SBAS891A-NOVEMBER 2018-REVISED OCTOBER 2019

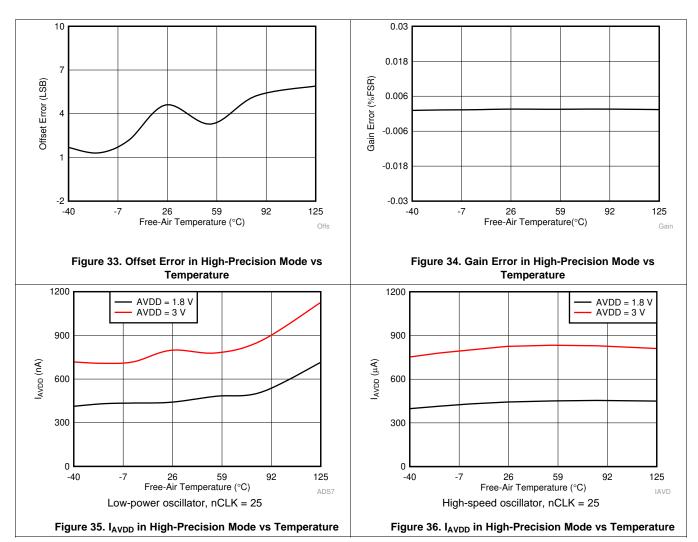

## 6.14 Typical Characteristics: High-Precision Mode

at  $T_A = 25^{\circ}$ C, AVDD = 3 V, DVDD = 3.3 V, and two-channel single-ended configuration (unless otherwise noted)

Copyright © 2018–2019, Texas Instruments Incorporated

## 7 Detailed Description

## 7.1 Overview

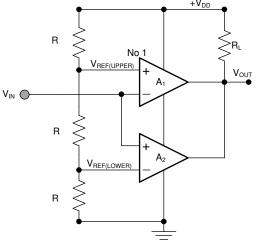

The ADS7142-Q1 is a small size, dual-channel, 12-bit programmable sensor monitor with an integrated analogto-digital converter (ADC), input multiplexer, digital comparator, data buffer, accumulator and internal oscillator. The *input multiplexer* can be either configured as two single-ended channels, one single-ended channel with remote ground sensing, or one pseudo-differential channel where the input can swing to approximately AVDD / 2. The device includes a *digital window comparator* with a dedicated output pin, which can be used to alert the host when a programmed high or low threshold is crossed. The device address is configured by the I2C address selector block. The device uses *internal oscillators* (high speed or low power) for conversion. The start of conversion is controlled by the host in *manual mode* and by the device in the *autonomous modes*.

The device also features a data buffer and an accumulator. The data buffer can store up to 16 conversion results of the ADC in the autonomous modes and the accumulator can accumulate up to 16 conversion results of the ADC in *high-precision mode*.

The device includes an offset calibration to calibration its own offset.

## 7.2 Functional Block Diagram

## 7.3 Feature Description

## 7.3.1 Analog Input and Multiplexer

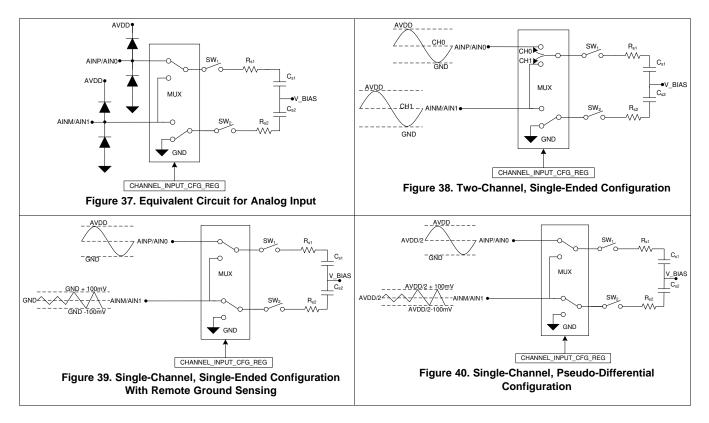

Figure 37 shows a small-signal equivalent circuit for the analog input pins. The device includes a two-channel analog multiplexer with each input pin having ESD protection diodes to AVDD and GND. The sampling switches are represented by ideal switches  $SW_1$  and  $SW_2$  in series with resistors  $R_{s1}$  and  $R_{s2}$  (typically 150  $\Omega$ ). The sampling capacitors,  $C_{s1}$  and  $C_{s2}$ , are typically 15 pF. The multiplexer configuration is set by the CH\_INPUT\_CFG register.

During acquisition, switches  $SW_1$  and  $SW_2$  are closed to allow the input signal to charge the internal sampling capacitors.

During conversion, switches  $SW_1$  and  $SW_2$  are opened to disconnect the input signal from the sampling capacitors.

The analog input of the device are optimized to be driven by high impedance source (up-to 100 k $\Omega$ ) in *Autonomous Modes* or in *High Precision Mode* mode with low power oscillator. It is recommended to drive the analog input of the device with an external amplifier when in *Autonomous Modes* or in *High Precision Mode* mode with a high-speed oscillator. Figure 29 and Figure 30 provide the analog input current for CH0 and CH1 of the device.

Figure 38, Figure 39 and Figure 40 provide a simplified circuit for analog input for input configurations described in *Two-Channel, Single-Ended Configuration, Single-Channel, Single-Ended Configuration* and *Single-Channel, Pseudo-Differential Configuration* respectively. The analog multiplexer supports following input configurations (set by writing into the CH\_INPUT\_CFG register).

## 7.3.1.1 Two-Channel, Single-Ended Configuration

Figure 38 shows a simplified block diagram showing a two-channel, single-ended configuration. Set the CH0\_CH1\_IP\_CFG bits = 00b or 11b to select this configuration. This configuration is also the default for the device after power up. In this configuration,  $C_{S2}$  always samples the GND pin and  $C_{S1}$  samples the input signal provided on channel 0 (AINP/AIN0) or channel 1 (AINM/AIN1) based on the channel selection. Each analog input channel can accept input signals in the range 0 V to AVDD V.

### Feature Description (continued)

On power-up, the device wakes up in manual mode with two-channel, single-ended configuration and samples CH0 only. This configuration can also be set by setting OPMODE\_SEL to 000b or 001b,

The device can be configured to sample either CH0 or CH1 or both channels by setting bits in the AUTO\_SEQ\_CHEN register to select the channels.

- To select a channel in AUTO sequence, set AUTO\_SEQ\_CHx bit in the AUTO\_SEQ\_CHEN register to 1.

- Set the bits in the OPMODE\_SEL register to 100b or 101b for manual mode with AUTO sequence.

- Set the bits in the OPMODE\_SEL register to 110b for Autonomous Modes with AUTO sequence.

- Set the bits in the OPMODE SEL register to 111b for High Precision Mode with AUTO sequence.

### 7.3.1.2 Single-Channel, Single-Ended Configuration

See Figure 39 for a simplified block diagram showing a single-channel, single ended configuration. Set  $CH0\_CH1\_IP\_CFG$  bits = 01b to select this configuration. In this configuration,  $C_{S1}$  samples the input signal provided on the AINP/AIN0 pin whereas  $C_{S2}$  samples input signal provided on the AINM/AIN1 pin. AINP/AIN0 pin can accept input signals in the range 0 V to AVDD V and AINM/AIN1 pin can accept input signals in the range 0 V to AVDD V and AINM/AIN1 pin can accept input signals in the range -100 mV to +100 mV. This input configuration is useful in systems where the sensor and/or the signal conditioning block is placed far from the device and there could be a small difference between the ground potentials. In this channel configuration, remove channel 1 from AUTO sequence by setting the AUTO\_SEQ\_CH1 bit to 0. Selecting channel 1 in AUTO sequence leads to an error condition and the device sets an error flag in the SEQUENCE\_STATUS register.

### 7.3.1.3 Single-Channel, Pseudo-Differential Configuration

See Figure 40 for a simplified block diagram showing a single-channel, pseudo-differential configuration. Set CH0\_CH1\_IP\_CFG bits = 10b to select this configuration. In this configuration,  $C_{S1}$  samples the input signal provided on the AINP/AIN0 pin whereas  $C_{S2}$  samples input signal provided on the AINM/AIN1 pin. AINP/AIN0 pin can accept input signals in the range 0 V to AVDD V and AINM/AIN1 pin can accept input signals in the range (AVDD/2) - 100 mV to (AVDD/2) + 100 mV. This input configuration is useful to interface with sensors that provide pseudo-differential signal with negative output as AVDD/2 like an electrochemical gas sensor. In this channel configuration, remove channel 1 from AUTO sequence by setting the AUTO\_SEQ\_CH1 bit to 0. Selecting channel 1 in AUTO sequence leads to an error condition and the device sets an error flag in SEQUENCE\_STATUS register.

## 7.3.2 OFFSET Calibration

The offset can be calibrated by setting the TRIG\_OFFCAL bit in the OFFSET\_CAL register. During offset calibration, the sampling switches are open (Figure 37) and the device keeps BUSY/RDY pin high. The device calculates its offset error and corrects for this error for subsequent conversions. The device calibrates the offset on power up. To nullify the change in offset due to change in temperature or in AVDD voltage, it is recommended to perform this calibration periodically.

## 7.3.3 Reference

The device uses the analog supply voltage (AVDD) as a reference for the analog-to-digital conversion process. It is recommended to place a 220-nF, low-ESR ceramic decoupling capacitor between the AVDD pin and the GND pin, close to the AVDD Pin. See *Power Supply Recommendations* section.

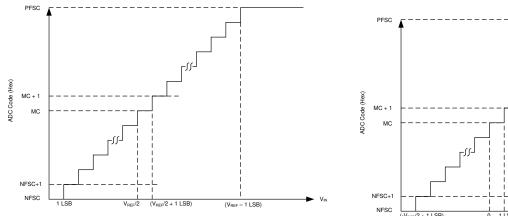

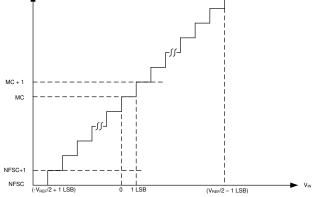

## 7.3.4 ADC Transfer Function

The ADC provides data in straight binary format. The ADC resolution can be computed by Equation 1:

$$1 \text{ LSB} = V_{\text{REF}} / 2^{\text{N}}$$

where:

- V<sub>REF</sub> = AVDD

- N = 12 for Autonomous Monitoring Modes and Manual Mode

ADS7142-Q1

SBAS891A-NOVEMBER 2018-REVISED OCTOBER 2019

## ADS7142-Q1

SBAS891A-NOVEMBER 2018-REVISED OCTOBER 2019

www.ti.com

## Feature Description (continued)

Figure 41 and Figure 42 show the ideal transfer characteristics for single-ended input and pseudo-differential input, respectively. Table 1 show the digital output codes for the transfer functions.

Figure 41. Ideal Transfer Characteristics for Single-Ended Configurations

Figure 42. Ideal Transfer Characteristics for Pseudo-Differential Configuration

## Table 1. Transfer Characteristics

| INPUT VOLTAGE FOR SINGLE-ENDED INPUT                              | INPUT VOLTAGE FOR PSEUDO<br>DIFFERENTIAL INPUT   | CODE     | DESCRIPTION                 | IDEAL<br>OUTPUT<br>CODE<br>(Autonomous<br>Monitoring<br>Mode or<br>Manual Mode) |

|-------------------------------------------------------------------|--------------------------------------------------|----------|-----------------------------|---------------------------------------------------------------------------------|

| ≤1 LSB                                                            | $\leq$ (-V <sub>REF</sub> / 2 + 1) LSB           | NFSC     | Negative full-scale<br>code | 000                                                                             |

| 1 LSB to 2 LSBs                                                   | $(-V_{REF} / 2 + 1)$ to $(-V_{REF} / 2 + 2)$ LSB | NFSC + 1 | —                           | 001                                                                             |

| (V <sub>REF</sub> / 2) to (V <sub>REF</sub> / 2) + 1 LSB          | 0 LSB to 1 LSB                                   | MC       | Mid code                    | 800                                                                             |

| (V <sub>REF</sub> / 2) + 1 LSB to (V <sub>REF</sub> / 2) + 2 LSBs | 1 LSB to 2 LSB                                   | MC + 1   | —                           | 801                                                                             |

| ≥ V <sub>REF</sub> – 1 LSB                                        | $\geq V_{REF} / 2 - 1 LSB$                       | PFSC     | Positive full-scale code    | FFF                                                                             |

## 7.3.5 Oscillator and Timing Control

The device uses one of the two internal oscillators (low power oscillator or high speed oscillator) for converting the analog input voltage into a digital output code.

The steps for selecting the oscillator and setting the sampling speed are listed below:

- Select the low power oscillator (OSC\_SEL = 1b) to monitor slow moving signals (< 300 Hz) at extremely low power consumption and sampling speeds (< 600 SPS). Select the high speed oscillator (OSC\_SEL = 0b) to scan the sensor signals with faster sampling speed (> 50 kHz).

- 2. Set sampling speed by programming the NCLK\_SEL register:

$$f_S = \frac{Oscillator frequency}{OLK}$$

nCLK

- f<sub>s</sub> = Sampling speed

- Oscillator frequency = 1 /  $t_{HSO}$  or 1 /  $t_{LPO}$  depending on the OSC\_SEL bit; see the *Specifications* section for 1 /  $t_{HSO}$  or 1 /  $t_{LPO}$

- nCLK is number of clocks in one conversion cycle (see the NCLK\_SEL register)

(2)

## 7.3.6 I<sup>2</sup>C Address Selector

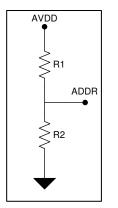

The I<sup>2</sup>C address for the device is determined by connecting external resistors on ADDR pin. The device address are selected on power-up based on the resistor values. The device retains this address until the next power up, or until next device reset, or until the device receives a command to program its own address (*General Call With Write Software Programmable Part of Slave Address*). Figure 43 provides the connection diagram for the ADDR pin and Table 2 provides the resistor values for selecting different addresses of the device.

Copyright © 2017, Texas Instruments Incorporated

## Figure 43. External Resistor Connection Diagram for ADDR Pin

## Table 2. I<sup>2</sup>C Address Selection

| RESISTORS          |                                 | 4000500        |

|--------------------|---------------------------------|----------------|

| R1 <sup>(1)</sup>  | R2 <sup>(1)</sup>               | ADDRESS        |

| 0 Ω                | DNP <sup>(2)</sup>              | 0011111b (1Fh) |

| 11 kΩ              | DNP <sup>(2)</sup>              | 0011110b (1Eh) |

| 33 kΩ              | DNP <sup>(2)</sup>              | 0011101b (1Dh) |

| 100 kΩ             | DNP <sup>(2)</sup>              | 0011100b (1Ch) |

| DNP <sup>(2)</sup> | $0\Omega$ or DNP <sup>(2)</sup> | 0011000b (18h) |

| DNP <sup>(2)</sup> | 11 kΩ                           | 0011001b (19h) |

| DNP <sup>(2)</sup> | 33 kΩ                           | 0011010b (1Ah) |

| DNP <sup>(2)</sup> | 100 kΩ                          | 0011011b (1Bh) |

(1) Tolerance for R1, R2 <  $\pm$ 5%.

(2) DNP = Do not populate.

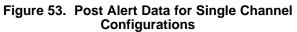

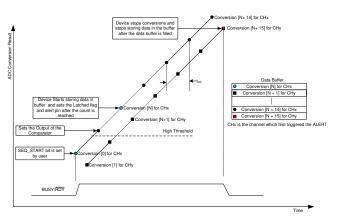

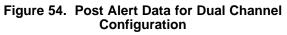

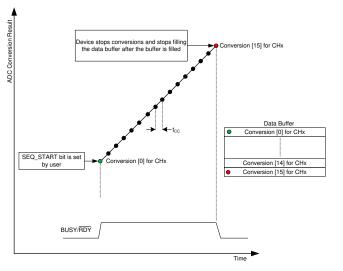

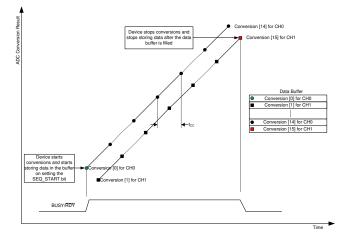

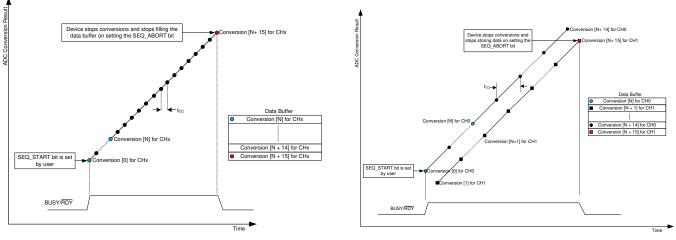

## 7.3.7 Data Buffer

When operating in autonomous monitoring mode, the device can use the internal data buffer for data storage. The internal data buffer is 16-bit wide and 16-word deep and follows the first-in, first-out (FIFO) approach.

ADS7142-Q1

SBAS891A-NOVEMBER 2018-REVISED OCTOBER 2019

### ADS7142-Q1

SBAS891A-NOVEMBER 2018-REVISED OCTOBER 2019

### 7.3.7.1 Filling of the Data Buffer

The write operation to the data buffer starts and stops as per the settings in the DATA\_BUFFER\_OPMODE register. The DATA\_BUFFER\_STATUS register provides the number of entries filled in the data buffer and this register can be read during an active sequence to get the current status of the data buffer. The time between two consecutive conversions is set by the NCLK\_SEL register and Equation 3 provides the relationship for time between two consecutive conversions of the same channel and nCLK parameter.

$t_{cc} = k \times nCLK \times OscillatorTimePeriod$

where

- $t_{cc}$  = Time between two consecutive conversions of same channel,  $t_{cc}$  = k ×  $t_{cycle}$

- k = Number of channels enabled in the device sequence

- nCLK = Number of clocks used by device for one conversion cycle

- Oscillator timer period = t<sub>LPO</sub> or t<sub>HSO</sub> depending on the OSC\_SEL value; see the Specifications section for t<sub>LPO</sub> or t<sub>HSO</sub>

(3)

The format of the 16-bit contents of each entry in the data buffer are set by programming the DOUT\_FORMAT\_CFG register. The DATA\_OUT\_CFG register enables the channel ID and DATA\_VALID flag in data buffer. Channel ID represents the channel number for the data entry in the data buffer. DATA\_VALID is set to zero in either of the following conditions:

- If the entry in the data buffer is not filled after the last start of sequence.

- If the I<sup>2</sup>C master tries to read more than 16 entries from the data buffer, the device provides zeros with DATA\_VALID set to zero

At the end of the write operation, the data buffer always has results of 16 (or lesser) consecutive conversions. The data buffer is filled in the order that the data is converted by the ADC. The channels converted by the ADC are controlled by the AUTO\_SEQ\_CHEN register. The entries that are not filled during an active sequence are filled with zeros.

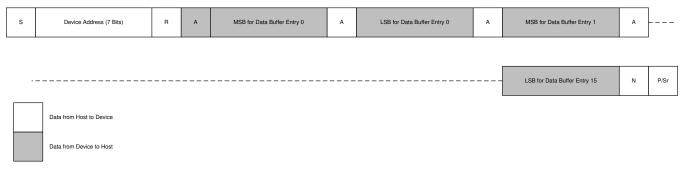

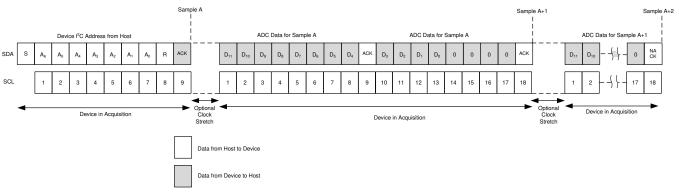

### 7.3.7.2 Reading Data From the Data Buffer

The device brings the BUSY/ $\overline{RDY}$  pin low after completion of the sequence or after the SEQ\_ABORT bit is set. As illustrated in Figure 44, the device provides the contents of the data buffer (in FIFO fashion) on receiving I<sup>2</sup>C read frame, which consists of the device address and the read bit set to 1.

## Figure 44. Reading Data Buffer (16 Bit Words × 16 Words)

The device returns zeroes with DATA VALID flag set to zero for all  $l^2C$  read frames received after all the valid data words from the data buffer are read or when a  $l^2C$  read frame is issued during an active sequence (indicated by high on the BUSY/RDY pin). The  $l^2C$  master needs to provide a NACK followed by a STOP or RESTART condition in an  $l^2C$  frame to finish the reading process. The data buffer is reset by setting the SEQ\_START bit or after resetting the device.

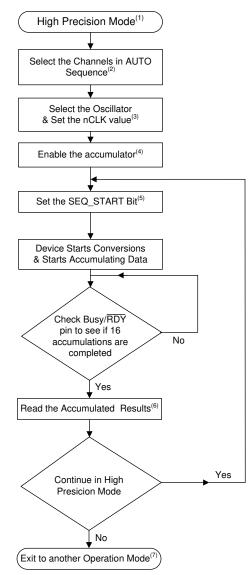

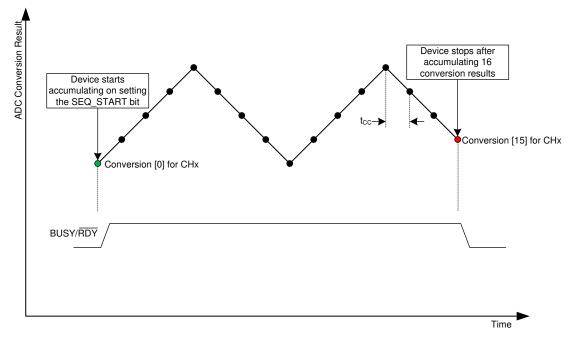

### 7.3.8 Accumulator

When operating in *High Precision Mode*, the device offers a 16-bit internal accumulator per channel. The Accumulator for a channel is enabled only if that channel is selected in the channel scanning sequence. The accumulator adds sixteen 12-bit conversion results. The result of adding 16 twelve bit words is one 16 bit word that has an effective resolution of an 16-bit ADC. The time between two consecutive conversions for accumulation is controlled by the NCLK\_SEL register and Equation 3 provides the relationship for time between two consecutive conversions of same channel and nCLK parameter.

The accumulated data can be read from the ACC\_CHx\_MSB and ACC\_CHx\_LSB registers in the device. The ACCUMULATOR\_STATUS register provides the number of accumulations done in the accumulator since last conversion. This register can be read during an active sequence to get the current status of the accumulator. The accumulator is reset on setting the SEQ\_START bit and on resetting the device. Equation 4 provides the relationship between high precision data and ADC conversion results.

High Precision Data for CHx =

$$\sum_{k=1}^{16}$$

Conversion Result[k] for CHx (4)

Equation 5 provides the value of LSB in high precision mode for the accumulated result.

$$1 LSB = \frac{AVDD}{2^{16}}$$

(5)

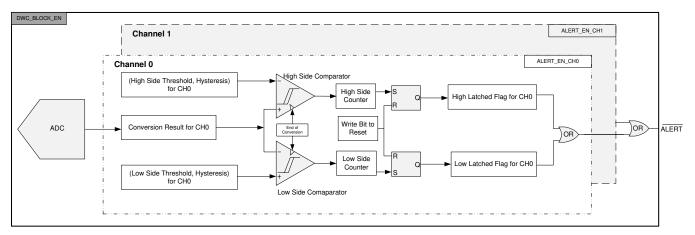

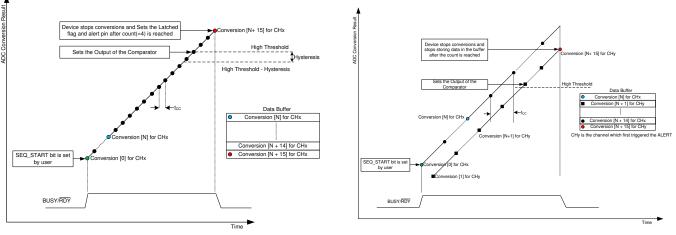

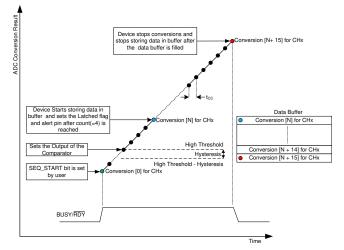

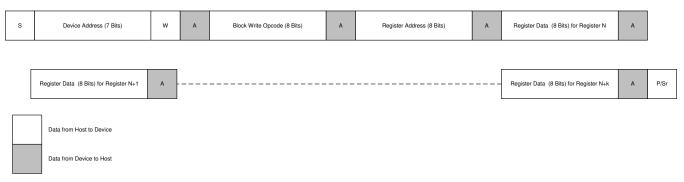

## 7.3.9 Digital Window Comparator

The internal digital window comparator is available in all modes. In *Autonomous Modes* with Thresholds monitoring and Diagnostics, the digital window comparator controls the filling of the data and the output of the alert pin and in other modes, it only controls the output of the ALERT pin. Figure 45 provides the block diagram for digital window comparator.

Figure 45. Digital Comparator Block Diagram

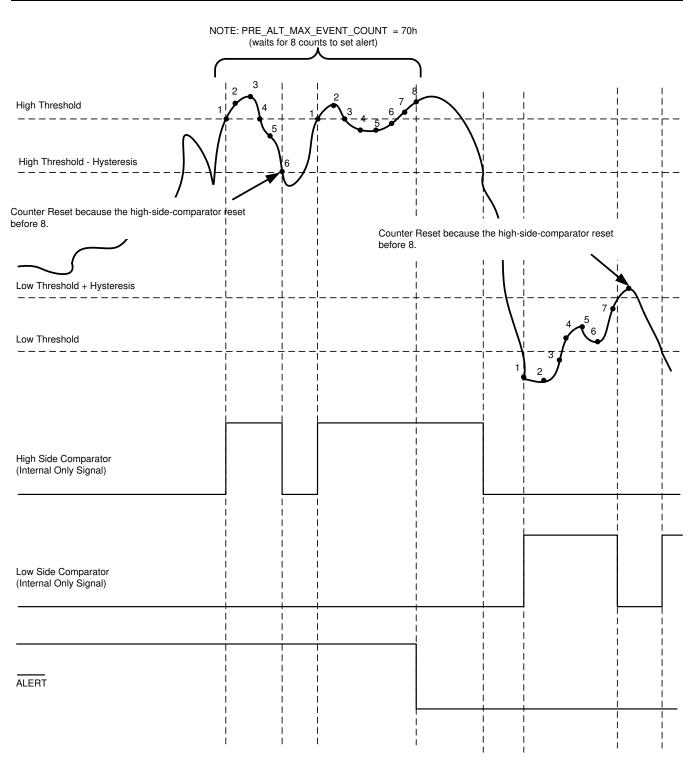

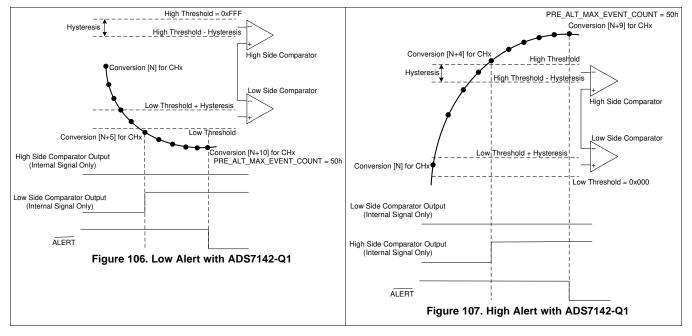

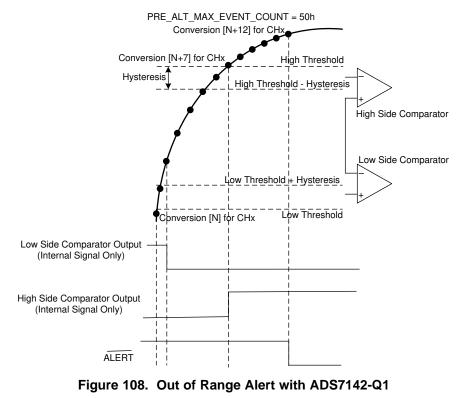

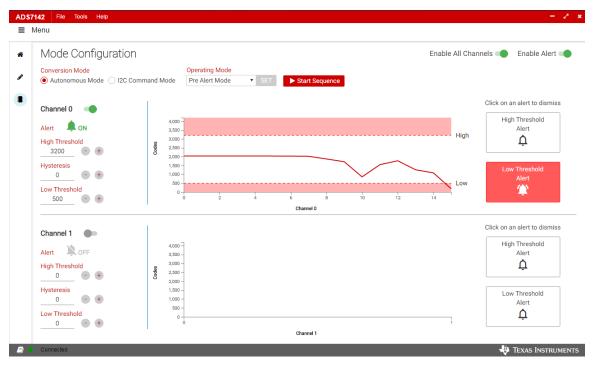

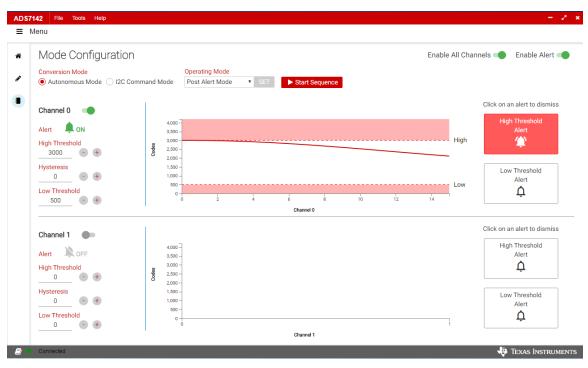

The low side threshold, high side threshold, and hysteresis parameters are independently programmable for each input channel. Figure 46 shows the comparison thresholds and hysteresis for the two comparators. A prealert event counter after each comparator counts the output of the comparator and sets the latched flags. The pre-alert event counter settings are common to the two channels. ADS7142-Q1 SBAS891A – NOVEMBER 2018 – REVISED OCTOBER 2019

www.ti.com

## Figure 46. Thresholds, Hysteresis and Event Counter for Digital Window Comparator

The DWC\_BLOCK\_EN bit in ALERT\_DWC\_EN register enables/disables the complete digital window comparator block (disabled at power-up) and ALERT\_EN\_CHx bits in the ALERT\_CHEN register enables digital window comparator for individual channels. When enabled, whenever a new conversion result is available:

1. The output of the high side comparator transitions to logic high when the conversion result is greater than the high threshold. This comparator resets when the conversion result is less than the high threshold – hysteresis.

- 2. The output of the low side comparator transitions to logic high when the conversion result is less than the low threshold. This comparator resets when the conversion result is greater than the low threshold + hysteresis.

- 3. A different threshold and hysteresis can be used for each channel.

- 4. When the output of either the high side or low side comparator transitions high the pre-alert event counter begins to increment for each subsequent conversion. This counter continues to increment until it reaches the value stored in the PRE\_ALT\_MAX\_EVENT\_COUNT register. When it reaches PRE\_ALT\_MAX\_EVENT\_COUNT, the alert becomes active and sets the latched flags. If the comparator output becomes zero before counter reaches PRE\_ALT\_MAX\_EVENT\_COUNT, then the event counter is reset to zero, Alert does not be set and latched flag is not set.

Therefore, the latched flags (high and low) for the channel are updated only if the respective comparator output remains 1 for the specified number of consecutive conversions (set by PRE\_ALT\_MAX\_EVENT\_COUNT).

The latched flags can be read from the ALERT\_LOW\_FLAGS and ALERT\_HIGH\_FLAGS registers. To clear a latched flag, write 1 to the applicable bit location. The ALERT pin status is re-evaluated whenever an applicable latched flag gets set or is cleared.

The response time for ALERT pin can be estimated by Equation 6

t<sub>response</sub> = [1 + k x (PRE\_ALT\_MAX\_EVENT\_COUNT + 1) ] x nCLK x Oscillator TimePeriod

where

- k = Number of channels enabled in device sequence

- nCLK = Number of clocks used by device for one conversion cycle

- Oscillator timer period = t<sub>LPO</sub> or t<sub>HSO</sub> depending on the OSC\_SEL value; see the Specifications section for t<sub>LPO</sub> or t<sub>HSO</sub>

(6)

## 7.3.10 I<sup>2</sup>C Protocol Features

## 7.3.10.1 General Call

On receiving a general call (00h), the device provides an ACK.

## 7.3.10.2 General Call With Software Reset

On receiving a general call (00h) followed with Software Reset (06h), the device resets itself.

## 7.3.10.3 General Call With Write Software Programmable Part of Slave Address

On receiving a general call (00h) followed by 04h, the device configures its own I<sup>2</sup>C address configured by the ADDR pin. During this operation, the device keeps BUSY/RDY Pin high and does not respond to other I<sup>2</sup>C commands except general call.

## 7.3.10.4 Configuring the Device Into High-Speed I<sup>2</sup>C Mode

The device can be configured in high-speed  $I^2C$  mode by providing an  $I^2C$  frame with one of the HS-mode master codes (08h to 0Fh).

After receiving one of the HS-mode master codes, the device sets the HS\_MODE bit in the OPMODE\_I2CMODE\_STATUS register and remains in high-speed I<sup>2</sup>C mode until a STOP condition is received in an I<sup>2</sup>C frame.

## 7.3.10.5 Bus Clear

If the SDA line is stuck low because of an incomplete I<sup>2</sup>C frame, providing nine clocks on SCL is recommended. The device releases the SDA line within these nine clocks, and then the next I<sup>2</sup>C frame can be started.

TEXAS INSTRUMENTS

www.ti.com

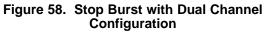

## 7.4 Device Functional Modes

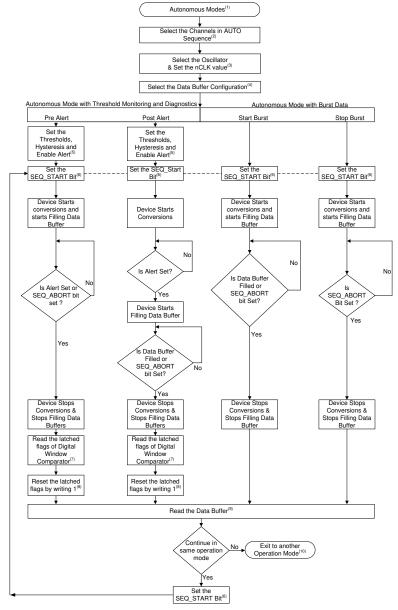

The device has below functional modes:

- Manual mode

- Autonomous modes:

- Autonomous mode with threshold monitoring and diagnostics

- Autonomous mode with burst data

- High-precision mode

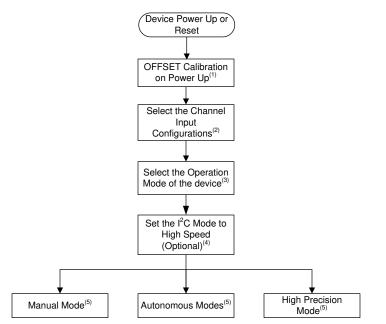

Device powers up in manual mode and can be configured into one of the other modes of these modes by writing the configuration registers for the desired mode. Steps for configuring device into different modes are illustrated in Figure 47

- (1) Offset can also be calibrated anytime during normal operation by setting the bit in the OFFSET\_CAL register.

- (2) Configure the CH\_INPUT\_CFG register.

- (3) Configure the OPMODE\_SEL register for the desired operation mode.

- (4) See the Configuring the Device Into High-Speed  $P^2C$  Mode section.

- (5) Operating mode is selected by configuring the OPMODE\_SEL register in step 3.

- (6) For reading and writing registers, see the *Programming* section.

## Figure 47. Configuring Device Into Different Modes

## 7.4.1 Device Power Up and Reset

On power up, the device calibrates its own offset and calculates the address from the resistors connected on ADDR pin. During this time, the device keeps BUSY/RDY high.

The device can be reset by recycling power on AVDD pin, by general call (00h) followed by software reset (06h), or by writing the WKEY register followed by setting the bit in the DEVICE\_RESET register.

Recycling power on the AVDD pin and on general call (00h) followed by software reset (06h), all the device configurations are reset, and the device initiates offset calibration and re-evaluates its I<sup>2</sup>C address.

When setting the bit in DEVICE\_RESET register, all the device configurations except latched flags for the digital window comparator and the WKEY register are reset. The device does not initiate offset calibration and does not re-evaluate its I<sup>2</sup>C address.

## **Device Functional Modes (continued)**

## 7.4.2 Manual Mode

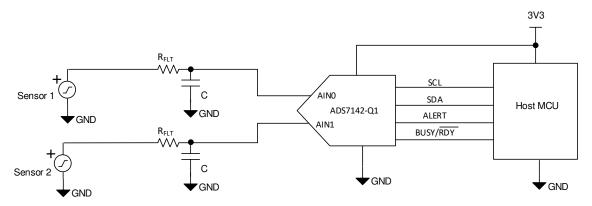

On power-up, the device is in Manual Mode using the single ended and dual channel configuration and starts by sampling the analog input applied on channel 0. In this mode, the device uses the high frequency oscillator for conversions. Manual mode allows the external host processor to directly request and control when the data is sampled. The data capture is initiated by an I<sup>2</sup>C command from the host processor and the data is then returned over the I<sup>2</sup>C bus at a throughput rate of up to 140-kSPS. Applications that can take advantage of this type of functionality include traditional ADC applications that require 1 or 2 channels of continuous data output.

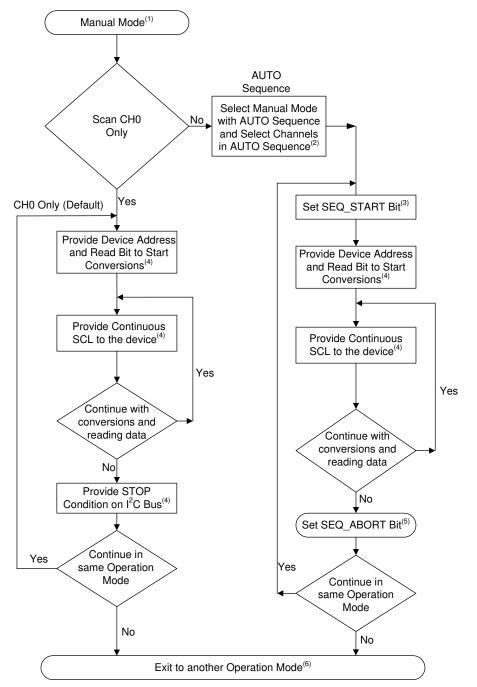

After setting the operation mode to manual mode as illustrated in Figure 47, steps for operating the device to be in manual mode and reading data are illustrated in Figure 48. The host can either configure the device to scan through one channel or both channels by configuring the CH\_INPUT\_CFG register and AUTO\_SEQ\_CHEN register.

## 7.4.2.1 Manual Mode With CH0 Only

Set the OPMODE\_SEL register to 000b or 001b for manual mode with channel 0 only. The host must provide the device address and read bit to start the conversions. To continue with conversions and reading data to the host must provide continuous SCL (Figure 49). In this mode, a NACK followed by a STOP condition in I<sup>2</sup>C frame is required to abort the operation. Then the device operation mode can be changed to another operation mode.

## 7.4.2.2 Manual Mode With AUTO Sequence

Set the OPMODE\_SEL register to 100b or 101b for manual mode with AUTO Sequence. The host must set the SEQ\_START bit in the START\_SEQUENCE register and provide the device address and read bit to start the conversions. To continue with conversions and reading data, the host must provide continuous SCL (Figure 49). In this mode, the SEQ\_ABORT bit in the ABORT\_SEQUENCE register must be set to abort the operation. Then the device operation mode can be changed to another operation mode. In this mode, a register read aborts the AUTO sequence.

In manual mode, the device always uses the high-speed oscillator and the nCLK parameter has no effect. The maximum scan rate is given by Equation 7:

$$f_s = \frac{1000}{\left[18 \times T_{SCL} + k\right]}$$