# High Performance ISM Band ASK/FSK/GFSK Transmitter IC

# ADF7011

#### **FEATURES**

Single Chip Low Power UHF Transmitter Frequency Band 433 MHz to 435 MHz 868 MHz to 870 MHz On-Chip VCO and Fractional-N PLL 2.3 V to 3.6 V Supply Voltage Programmable Output Power -16 dBm to +12 dBm, 0.3 dB Steps Data Rates up to 76.8 kbps Low Current Consumption 29 mA at +10 dBm at 433.92 MHz Power-Down Mode (<1 μA) 24-Lead TSSOP Package Hooks to External VCO for < 1.4 GHz Operation

APPLICATIONS Low Cost Wireless Data Transfer Wireless Metering Remote Control/Security Systems Keyless Entry

#### **GENERAL DESCRIPTION**

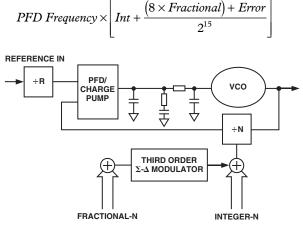

The ADF7011 is a low power OOK/ASK/FSK/GFSK UHF transmitter designed for use in ISM band systems. It contains and integrated VCO and  $\Sigma$ - $\Delta$  fractional-N PLL. The output power, channel spacing, and output frequency are programmable with four 24-bit registers. The fractional-N PLL enables the user to select any channel frequency within the European 433 MHz and 868 MHz bands, allowing the use of the ADF7011 in frequency hopping systems. The fractional-N also allows the transmitter to operate in the less congested sub-bands of the 868 MHz to 870 MHz SRD band.

It is possible to choose from the four different modulation schemes: Binary or Gaussian Frequency Shift Keying (FSK/ GFSK), Amplitude Shift Keying (ASK), or On/Off Keying (OOK). The device also features a crystal compensation register that can provide  $\pm 1$  ppm resolution in the output frequency. Indirect temperature compensation of the crystal can be accomplished inexpensively using this register.

Control of the four on-chip registers is via a simple 3-wire interface. The devices operate with a power supply ranging from 2.3 V to 3.6 V and can be powered down when not in use.

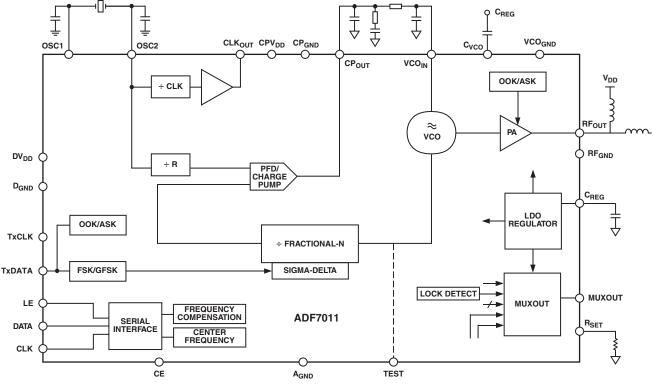

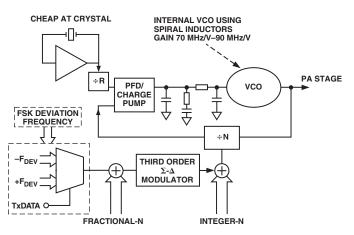

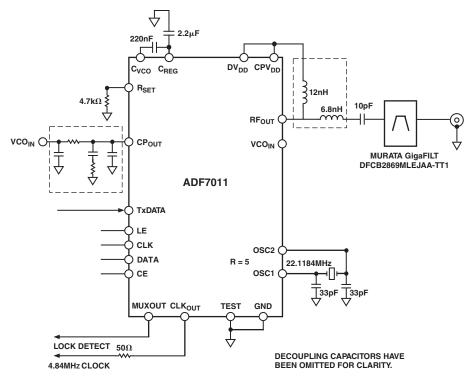

#### FUNCTIONAL BLOCK DIAGRAM

#### REV.0

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective companies.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781/329-4700 www.analog.com Fax: 781/326-8703 © 2003 Analog Devices, Inc. All rights reserved.

# ADF7011-SPECIFICATIONS<sup>1</sup>

| $(V_{DD} = 2.3 \text{ V to } 3.6 \text{ V}, \text{ GND} = 0 \text{ V}, T_A = T_{MIN} \text{ to } T_{MAX},$ | unless otherwise noted.   |

|------------------------------------------------------------------------------------------------------------|---------------------------|

| Typical specifications are at $V_{DD} = 3 \text{ V}, T_A = 25^{\circ}\text{C}$                             | , FPFD = 4 MHz @ 433 MHz, |

| FPFD = 22.1184/5.)                                                                                         | www.DataSheet4U.com       |

| Parameter                                                                                                                                                                                 | Min                     | Тур                           | Max                | Unit                              |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|-------------------------------|--------------------|-----------------------------------|

| RF CHARACTERISTICS                                                                                                                                                                        |                         |                               |                    |                                   |

| Output Frequency Ranges                                                                                                                                                                   |                         |                               |                    |                                   |

| Lower SRD Band                                                                                                                                                                            | 433                     |                               | 435                | MHz                               |

| Upper SRD Band                                                                                                                                                                            | 868                     |                               | 870                | MHz                               |

| Phase Frequency Detector Frequency                                                                                                                                                        | 3.4                     |                               | 20                 | MHz                               |

| TRANSMISSION PARAMETERS                                                                                                                                                                   |                         |                               |                    |                                   |

| Transmit Rate <sup>2</sup>                                                                                                                                                                |                         |                               |                    |                                   |

| FSK                                                                                                                                                                                       | 0.3                     |                               | 76.8               | kbits/s                           |

| ASK                                                                                                                                                                                       | 0.3                     |                               | 9.6                | kbits/s                           |

| GFSK                                                                                                                                                                                      | 0.3                     |                               | 76.8               | kbits/s                           |

| Frequency Shift Keying                                                                                                                                                                    | 0.5                     |                               | 10.0               | KUILS/S                           |

| FSK Separation <sup>3</sup>                                                                                                                                                               | 1                       |                               | 110                | kHz using 3.625 MHz PFD           |

| TSK Separation                                                                                                                                                                            | 4.88                    |                               | 620                | kHz using 20 MHz PFD              |

| Course Filter Ot                                                                                                                                                                          | 4.00                    | 0.5                           | 020                | KHZ USING 20 MHZ FFD              |

| Gaussian Filter $\beta$ t                                                                                                                                                                 |                         | 0.5                           | 20                 | 10                                |

| Amplitude Shift Keying Depth                                                                                                                                                              |                         |                               | 28                 | dB                                |

| On/Off Keying                                                                                                                                                                             |                         |                               | 40                 | dB                                |

| Output Power (No Filtering) <sup>4</sup>                                                                                                                                                  |                         |                               |                    |                                   |

| 868 MHz                                                                                                                                                                                   |                         |                               | 3                  | dBm                               |

| 433 MHz                                                                                                                                                                                   |                         |                               | 10                 | dBm                               |

| Output Power Variation                                                                                                                                                                    |                         |                               |                    |                                   |

| Max Power Setting                                                                                                                                                                         | 9                       | 12                            |                    | $dBm V_{DD} = 3.6 V$              |

| Max Power Setting                                                                                                                                                                         |                         | 11                            |                    | $dBm V_{DD} = 3.0 V$              |

| Max Power Setting                                                                                                                                                                         |                         | 9.5                           |                    | $dBm V_{DD} = 2.3 V$              |

| Programmable Step Size                                                                                                                                                                    |                         |                               |                    |                                   |

| -16 dBm to $+12$ dBm                                                                                                                                                                      |                         | 0.3125                        |                    | dB                                |

| LOGIC INPUTS                                                                                                                                                                              |                         |                               |                    |                                   |

|                                                                                                                                                                                           | $0.7 	imes V_{DD}$      |                               |                    | V                                 |

| V <sub>INH</sub> , Input High Voltage                                                                                                                                                     | $0.7 \wedge V_{\rm DD}$ |                               | $0.0 \times V$     |                                   |

| V <sub>INL</sub> , Input Low Voltage                                                                                                                                                      |                         |                               | $0.2 	imes V_{DD}$ | V                                 |

| I <sub>INH</sub> /I <sub>INL</sub> , Input Current                                                                                                                                        |                         |                               | ±1                 | μΑ                                |

| C <sub>IN</sub> , Input Capacitance                                                                                                                                                       |                         |                               | 10                 | pF                                |

| Control Clock Input                                                                                                                                                                       |                         |                               | 50                 | MHz                               |

| LOGIC OUTPUTS                                                                                                                                                                             |                         |                               |                    |                                   |

| V <sub>OH</sub> , Output High Voltage                                                                                                                                                     | $DV_{DD} - 0.4$         |                               |                    | V, I <sub>OH</sub> = 500 μA       |

| V <sub>OL</sub> , Output Low Voltage                                                                                                                                                      |                         |                               | 0.4                | $V, I_{OL} = 500 \mu A$           |

| CLK <sub>OUT</sub> Rise/Fall Time                                                                                                                                                         |                         | 16                            |                    | ns $F_{CLK}$ = 4.8 MHz into 10 pF |

| CLK <sub>OUT</sub> Mark: Space Ratio                                                                                                                                                      |                         | 50:50                         |                    |                                   |

|                                                                                                                                                                                           |                         |                               |                    |                                   |

| POWER SUPPLIES                                                                                                                                                                            |                         |                               |                    |                                   |

| Voltage Supply                                                                                                                                                                            |                         |                               | 2.6                | 37                                |

| $DV_{DD}$                                                                                                                                                                                 | 2.3                     |                               | 3.6                | V                                 |

|                                                                                                                                                                                           |                         |                               |                    |                                   |

| Transmit Current Consumption                                                                                                                                                              |                         |                               |                    |                                   |

| Transmit Current Consumption<br>433 MHz                                                                                                                                                   |                         |                               |                    |                                   |

| Transmit Current Consumption<br>433 MHz<br>0 dBm (1 mW)                                                                                                                                   |                         | 17                            |                    | mA                                |

| Transmit Current Consumption<br>433 MHz<br>0 dBm (1 mW)<br>10 dBm (10 mW)                                                                                                                 |                         | 17<br>29                      |                    | mA<br>mA                          |

| Transmit Current Consumption<br>433 MHz<br>0 dBm (1 mW)<br>10 dBm (10 mW)<br>868 MHz                                                                                                      |                         | 29                            |                    |                                   |

| Transmit Current Consumption<br>433 MHz<br>0 dBm (1 mW)<br>10 dBm (10 mW)<br>868 MHz<br>0 dBm (1 mW)                                                                                      |                         | 29<br>19                      |                    |                                   |

| Transmit Current Consumption<br>433 MHz<br>0 dBm (1 mW)<br>10 dBm (10 mW)<br>868 MHz                                                                                                      |                         | 29                            |                    | mA                                |

| Transmit Current Consumption<br>433 MHz<br>0 dBm (1 mW)<br>10 dBm (10 mW)<br>868 MHz<br>0 dBm (1 mW)                                                                                      |                         | 29<br>19                      |                    | mA<br>mA                          |

| Transmit Current Consumption<br>433 MHz<br>0 dBm (1 mW)<br>10 dBm (10 mW)<br>868 MHz<br>0 dBm (1 mW)<br>3 dBm (2 mW)<br>10 dBm (10 mW)                                                    |                         | 29<br>19<br>20.5              |                    | mA<br>mA<br>mA                    |

| Transmit Current Consumption<br>433 MHz<br>0 dBm (1 mW)<br>10 dBm (10 mW)<br>868 MHz<br>0 dBm (1 mW)<br>3 dBm (2 mW)<br>10 dBm (10 mW)<br>Crystal Oscillator Block Current                |                         | 29<br>19<br>20.5              |                    | mA<br>mA<br>mA<br>mA              |

| Transmit Current Consumption<br>433 MHz<br>0 dBm (1 mW)<br>10 dBm (10 mW)<br>868 MHz<br>0 dBm (1 mW)<br>3 dBm (2 mW)<br>10 dBm (10 mW)<br>Crystal Oscillator Block Current<br>Consumption |                         | 29<br>19<br>20.5<br>34<br>190 |                    | mA<br>mA<br>mA<br>μA              |

| Transmit Current Consumption<br>433 MHz<br>0 dBm (1 mW)<br>10 dBm (10 mW)<br>868 MHz<br>0 dBm (1 mW)<br>3 dBm (2 mW)<br>10 dBm (10 mW)<br>Crystal Oscillator Block Current                |                         | 29<br>19<br>20.5<br>34        |                    | mA<br>mA<br>mA<br>mA              |

#### ADF7011 www.DataSheet4U.com

| Parameter                                     | Min          | Тур       | Max            | Unit                                      |

|-----------------------------------------------|--------------|-----------|----------------|-------------------------------------------|

| PHASE-LOCKED LOOP                             |              |           |                |                                           |

| VCO Gain 433 MHz/868 MHz                      |              | 40/80     |                | MHz/V @ 868 MHz                           |

| Phase Noise (In-Band) <sup>5</sup> 433 MHz    |              | -81       |                | dBc/Hz @ 5 kHz offset                     |

| Phase Noise (Out-of-Band) <sup>6</sup>        |              | -90       |                | dBc/Hz @ 1 MHz offset                     |

| Phase Noise (In-Band) <sup>7</sup> 868 MHz    |              | -83       |                | dBc/Hz @ 5 kHz offset                     |

| Phase Noise (Out-of-Band) <sup>8</sup>        |              | -95       |                | dBc/Hz @ 1 MHz offset                     |

|                                               |              |           |                | 100 kHz loop BW                           |

| Spurious <sup>9, 10</sup>                     |              |           |                |                                           |

| 47-74, 87.5-118, 174-230, 470-862 MHz         |              |           | -54            | dBm                                       |

| 9 kHz – 1 GHz                                 |              |           | -36            | dBm                                       |

| Above 1 GHz                                   |              |           | -30            | dBm. Assumes external harmonic filter.    |

| Harmonics <sup>10</sup>                       |              |           |                |                                           |

| Second Harmonic, 433 MHz/868 MHz              |              | -23/-28   | -20/-23        | dBc                                       |

| Third Harmonic, 433 MHz/868 MHz               |              | -25/-29   | -22/-25        | dBc                                       |

| Other Harmonics, 433 MHz/868 MHz              |              | -26/-40   | -23/-35        | dBc                                       |

| REFERENCE INPUT                               |              |           |                |                                           |

| Crystal Reference                             |              |           |                |                                           |

| 433 MHz                                       | 1.7          |           | 22.1184        | MHz                                       |

| 868 MHz                                       | 3.4          |           | 22.1184        | MHz                                       |

| External Oscillator                           |              |           |                |                                           |

| Frequency                                     | 3.4          |           | 40             | MHz                                       |

| Input Level, High Voltage                     | $0.7 V_{DD}$ |           |                | V                                         |

| Input Level, Low Voltage                      |              |           | $0.2 \ V_{DD}$ | V                                         |

| FREQUENCY COMPENSATION                        |              |           |                |                                           |

| Pull In Range of Register                     | 1            |           | 100            | ppm                                       |

| PA CHARACTERISTICS                            |              |           |                |                                           |

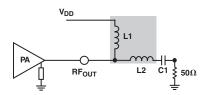

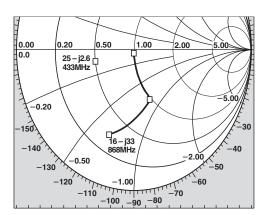

| RF Output Impedance                           |              |           |                |                                           |

| 868 MHz                                       |              | 16 – j33  |                | $\Omega$ , Z <sub>REF</sub> = 50 $\Omega$ |

| 433 MHz                                       |              | 25 – j2.6 |                | Ω, Z <sub>REF</sub> = 50 Ω                |

| TIMING INFORMATION                            |              |           |                |                                           |

| Chip Enabled to Regulator Ready <sup>10</sup> |              | 50        | 200            | μs                                        |

| Crystal Oscillator to CLK <sub>OUT</sub> OK   |              |           |                |                                           |

| 4 MHz Crystal                                 |              | 1.8       |                | ms                                        |

| 22.1184 MHz Crystal                           |              | 2.2       |                | ms                                        |

| TEMPERATURE RANGE – T <sub>A</sub>            | -40          |           | +85            | °C                                        |

NOTES

<sup>1</sup>Operating temperature range is as follows: -40°C to +85°C.

<sup>2</sup>Datarates should be limited to adhere to edge of band requirements in accordance with ETSI 300-220

<sup>3</sup>Frequency Deviation = (PFD Frequency × Mod Deviation )/ $2^{12}$ .

GFSK Frequency Deviation = (PFD Frequency  $\times 2^{m}/2^{12}$  where m = Mod Control.

<sup>4</sup> The output power is limited by the spurious requirements of ETSI at +55°C. The addition of an output filter (see Applications section) will allow increased output levels to >10 dBm at both 433 MHz and 868 MHz

${}^{5}V_{DD} = 3 \text{ V}, \text{ PFD} = 4 \text{ MHz}, \text{ PA} = 10 \text{ dBm}$

$^{6}$  V<sub>DD</sub> = 3 V, Loop Filter BW = 100 kHz

$^{7}$  V<sub>DD</sub> = 3 V, PFD = 4.42368 MHz, PA = 3 dBm

$^{8}V_{DD} = 3 \text{ V}$ , Loop Filter BW = 100 kHz

<sup>9</sup> These spurious levels are based on a maximum output power of +3 dBm for 868 MHz and +10 dBm for 433 MHz. It assumes a PFD frequency of <5 MHz. Recommended PFD frequencies are 4.42368 MHz (22.1184/5) for 868 MHz, and 4 MHz for 433 MHz operation. Compliance for higher output powers will require an external filter. See Applications section.

<sup>10</sup> Not production tested. Based on characterization.

Specifications subject to change without notice.

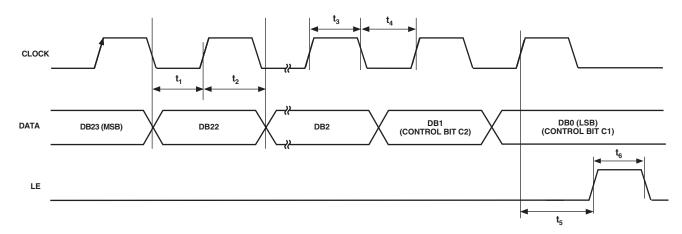

# TIMING CHARACTERISTICS ( $V_{DD} = 3 V \pm 10\%$ ; VGND = 0 V, $T_A = 25^{\circ}C$ , unless otherwise noted.)

| Parameter      | Limit at<br>T <sub>MIN</sub> to T <sub>MAX</sub><br>(B Version) | Unit   | Test Conditions/Comments |

|----------------|-----------------------------------------------------------------|--------|--------------------------|

| t <sub>1</sub> | 10                                                              | ns min | DATA to CLOCK Setup Time |

| t <sub>2</sub> | 10                                                              | ns min | DATA to CLOCK Hold Time  |

| t <sub>3</sub> | 25                                                              | ns min | CLOCK High Duration      |

| t <sub>4</sub> | 25                                                              | ns min | CLOCK Low Duration       |

| t <sub>5</sub> | 10                                                              | ns min | CLOCK to LE Setup Time   |

| t <sub>6</sub> | 20                                                              | ns min | LE Pulsewidth            |

Guaranteed by design but not production tested.

Specifications subject to change without notice.

Figure 1. Timing Diagram

#### **ABSOLUTE MAXIMUM RATINGS<sup>1, 2</sup>**

| $(T_A = 25^{\circ}C, \text{ unless otherwise noted.})$                            |

|-----------------------------------------------------------------------------------|

| $V_{DD}$ to $GND^3$                                                               |

| $CPV_{DD}$ to $GND$                                                               |

| Digital I/O Voltage to GND $\dots \dots \dots -0.3$ V to DV <sub>DD</sub> + 0.3 V |

| Operating Temperature Range                                                       |

| Industrial (B Version)                                                            |

| Storage Temperature Range $\dots -65^{\circ}C$ to $+125^{\circ}C$                 |

| Maximum Junction Temperature 125°C                                                |

| TSSOP $\theta_{JA}$ Thermal Impedance 150.4°C/W                                   |

| Lead Temperature, Soldering                                                       |

| Vapor Phase (60 sec) 235°C                                                        |

| Infrared (15 sec) 240°C                                                           |

|                                                                                   |

#### NOTES

<sup>1</sup> Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those listed in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

$^2$  This device is a high performance RF integrated circuit with an ESD rating of  $<\!1$  kV and is ESD sensitive. Proper precautions should be taken for handling and assembly.

${}^{3}$ GND = VCOGND = CPGND = RFGND = DGND = AGND = 0 V.

#### **ORDERING GUIDE**

| Model            | Temperature<br>Range               | Package Option |

|------------------|------------------------------------|----------------|

| ADF7011BRU       | -40°C to +85°C                     | RU-24 (TSSOP)  |

| ADF7011BRU-REEL  | -40°C to +85°C                     | RU-24 (TSSOP)  |

| ADF7011BRU-REEL7 | $-40^{\circ}$ C to $+85^{\circ}$ C | RU-24 (TSSOP)  |

#### CAUTION \_

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although the ADF7011 features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

### PIN CONFIGURATION

#### PIN FUNCTION DESCRIPTIONS

| Pin No. | Mnemonic           | Function                                                                                                                                                                                                                                                                                                                                                          |

|---------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | R <sub>SET</sub>   | External Resistor to Set Change Pump Current and Some Internal Bias Currents. Use 4.7 kΩ as default:                                                                                                                                                                                                                                                              |

|         |                    | $I_{CP MAX} = \frac{9.5}{R_{SET}}$                                                                                                                                                                                                                                                                                                                                |

|         |                    | So, with $R_{SET} = 4.7 \text{ k}\Omega$ , $I_{CP MAX} = 2.02 \text{ mA}$ .                                                                                                                                                                                                                                                                                       |

| 2       | CPV <sub>DD</sub>  | Charge Pump Supply. This should be biased at the same level as $RF_{OUT}$ and $DV_{DD}$ . The pin should be decoupled with a 0.1 $\mu$ F capacitor as close to the pin as possible.                                                                                                                                                                               |

| 3       | CP <sub>GND</sub>  | Charge Pump Ground.                                                                                                                                                                                                                                                                                                                                               |

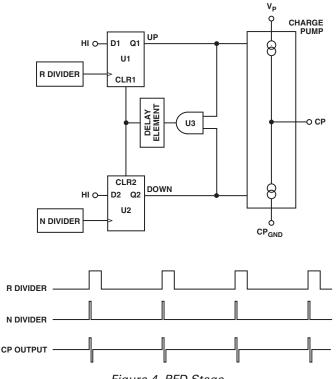

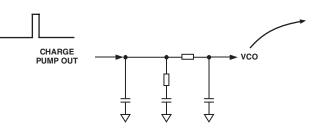

| 4       | CP <sub>OUT</sub>  | Charge Pump Output. This output generates current pulses that are integrated in the loop filter. The integrated current changes the control voltage on the input to the VCO.                                                                                                                                                                                      |

| 5       | CE                 | Chip Enable. A logic low applied to this pin powers down the part. This must be high for the part to function. This is the only way to power down the regulator circuit.                                                                                                                                                                                          |

| 6       | DATA               | Serial Data Input. The serial data is loaded MSB first with the two LSBs being the control bits. This is a high impedance CMOS input.                                                                                                                                                                                                                             |

| 7       | CLK                | Serial Clock Input. This serial clock is used to clock in the serial data to the registers. The data is latched into the 24-bit shift register on the CLK rising edge. This input is a high impedance CMOS input.                                                                                                                                                 |

| 8       | LE                 | Load Enable, CMOS Input. When LE goes high, the data stored in the shift registers is loaded into one of the four latches, the latch being selected using the control bits.                                                                                                                                                                                       |

| 9       | TxDATA             | Digital data to be transmitted is input on this pin.                                                                                                                                                                                                                                                                                                              |

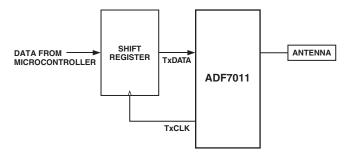

| 10      | TxCLK              | GFSK Only. This clock output is used to synchronize microcontroller data to the TxDATA pin of the ADF7011. The clock is provided at the same frequency as the data rate.                                                                                                                                                                                          |

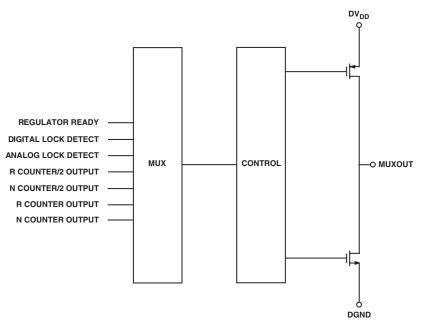

| 11      | MUXOUT             | This multiplexer output allows either the digital lock detect (most common), the scaled RF, or the scaled reference frequency to be accessed externally. Used commonly for system debug. See the Function Register Map.                                                                                                                                           |

| 12      | D <sub>GND</sub>   | Ground Pin for the RF Digital Circuitry.                                                                                                                                                                                                                                                                                                                          |

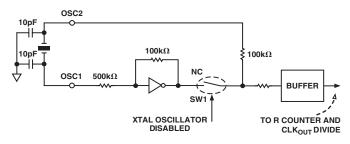

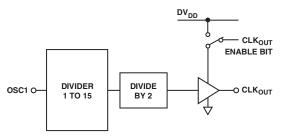

| 13      | CLK <sub>OUT</sub> | The Divided Down Crystal Reference with 50:50 Mark-Space Ratio. May be used to drive the clock input of a microcontroller. To reduce spurious components in the output spectrum, the sharp edges can be reduced with a series RC. For 4.8 MHz output clock, a series 50 $\Omega$ into 10 pF will reduce spurs to < -50 dBc. Defaults on power-up to divide by 16. |

| 14      | OSC2               | Oscillator Pin. If a single-ended reference (such as a TCXO) is used, it should be applied to this pin.<br>When using an external signal generator, a 51 $\Omega$ resistor should be tied from this pin to ground. The XOE bit in the R register should set high when using an external reference.                                                                |

| Pin No. | Mnemonic           | Function                                                                                                                                                                                                                       |

|---------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15      | OSC1               | Oscillator Pin. For use with crystal reference only. This is three-stated when an external reference oscilla-<br>tor is used.                                                                                                  |

| 16      | VCO <sub>GND</sub> | Voltage Controlled Oscillator Ground.                                                                                                                                                                                          |

| 17      | TEST               | Input to the RF Fractional-N Divider. This pin allows the user to connect an external VCO to the part. Disabling the internal VCO activates this pin. If the internal VCO is used, this pin should be grounded.                |

| 18      | $DV_{DD}$          | Positive Supply for the Digital Circuitry. This must be between 2.3 V and 3.6 V. Decoupling capacitors to the analog ground plane should be placed as close as possible to this pin.                                           |

| 19      | RF <sub>GND</sub>  | Ground for Output Stage of Transmitter.                                                                                                                                                                                        |

| 20      | RF <sub>OUT</sub>  | The modulated signal is available at this pin. Output power levels are from $-16$ dBm to $+12$ dBm. The output should be impedance matched to the desired load using suitable components. See the RF Output Stage section.     |

| 21      | A <sub>GND</sub>   | Ground Pin for the RF Analog Circuitry.                                                                                                                                                                                        |

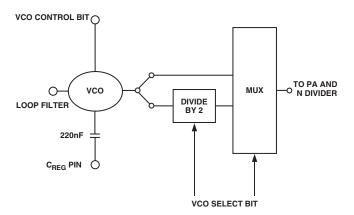

| 22      | VCO <sub>IN</sub>  | The tuning voltage on this pin determines the output frequency of the Voltage Controlled Oscillator (VCO). The higher the tuning voltage, the higher the output frequency.                                                     |

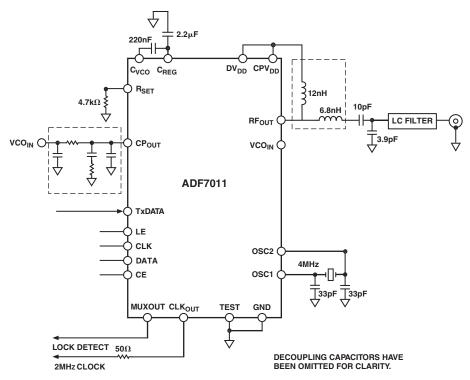

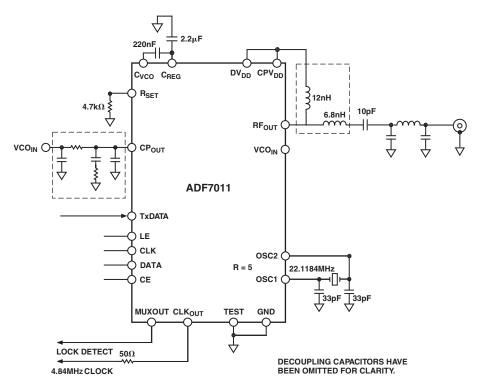

| 23      | C <sub>VCO</sub>   | A 0.22 $\mu$ F capacitor should be added to reduce noise on VCO bias lines. Tied to the C <sub>REG</sub> pin.                                                                                                                  |

| 24      | C <sub>REG</sub>   | A 2.2 $\mu$ F capacitor should be added at C <sub>REG</sub> , tied to GND, to reduce regulator noise and improve stability. A reduced capacitor will improve regulator power-on time but may cause higher spurious components. |

### PIN FUNCTION DESCRIPTIONS (continued)

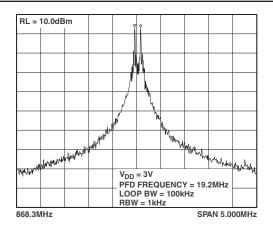

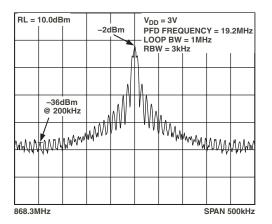

# Typical Performance Characteristics-ADF7011

TPC 1. FSK Modulated Signal,  $F_{DEVIATION} = 58$  kHz, Data Rate = 19.2 kbps, 10 dBm

TPC 2. OOK Modulated Signal, Data Rate = 4.8 kbps, 4 dBm

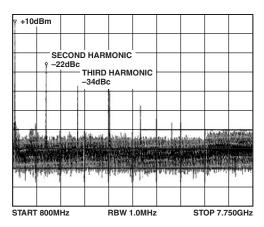

*TPC 3. Harmonic Levels at 10 dBm Output Power. See Figure 15.*

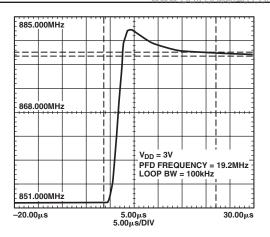

TPC 4. PLL Settling Time, 852 MHz to 878 MHz, 23  $\mu s$  (±400 kHz)

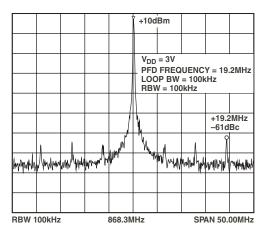

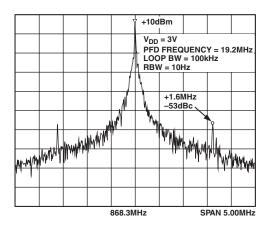

TPC 5. PFD Spurious/Fractional Spurious Components

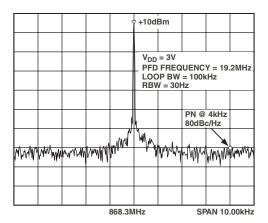

TPC 6. In-Band Phase Noise

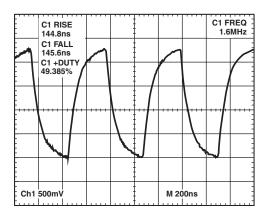

TPC 7. 1.6 MHz CLOCK<sub>OUT</sub> Waveform

TPC 8. Spurious Signal Generated by CLOCK<sub>OUT</sub>

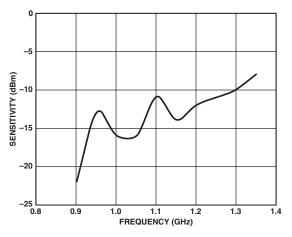

TPC 9. N-Divider Input Sensitivity

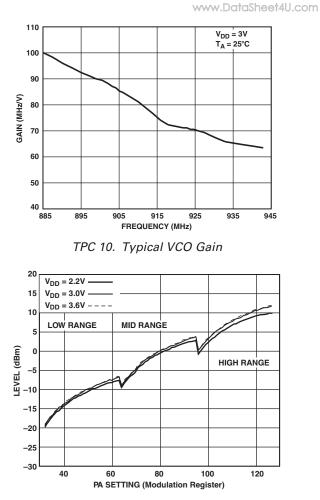

TPC 11. PA Output Programmability,  $T_A = 25^{\circ}C$

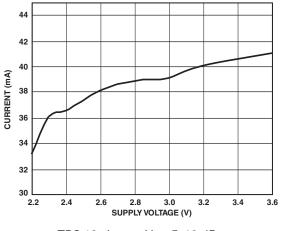

TPC 12. I<sub>DD</sub> vs. V<sub>DD</sub> @ 10 dBm

### **REGISTER MAPS**

#### **RF R REGISTER**

| RESE | ERVED | CLK <sub>OUT</sub> |      |      | XOE  |      |      | 11-BIT FREQUENCY ERROR CORRECTION |      |      |      |      |      |     |     |     |     |     | TROL<br>TS |     |     |        |        |

|------|-------|--------------------|------|------|------|------|------|-----------------------------------|------|------|------|------|------|-----|-----|-----|-----|-----|------------|-----|-----|--------|--------|

| DB23 | DB22  | DB21               | DB20 | DB19 | DB18 | DB17 | DB16 | DB15                              | DB14 | DB13 | DB12 | DB11 | DB10 | DB9 | DB8 | DB7 | DB6 | DB5 | DB4        | DB3 | DB2 | DB1    | DB0    |

| R2   | R1    | CL4                | CL3  | CL2  | CL1  | X1   | R4   | R3                                | R2   | R1   | F11  | F10  | F9   | F8  | F7  | F6  | F5  | F4  | F3         | F2  | F1  | C2 (0) | C1 (0) |

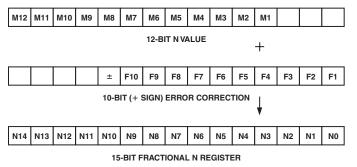

#### **RF N REGISTER**

| LD<br>PRECISION | VCO<br>BAND | 8-BIT INTEGER-N |                                       |  |  |  |  |  |  |  |      |      |      | 12-BI | IT FRA | CTION | AL-N |     |     |     |     |        | ITROL<br>ITS |

|-----------------|-------------|-----------------|---------------------------------------|--|--|--|--|--|--|--|------|------|------|-------|--------|-------|------|-----|-----|-----|-----|--------|--------------|

| DB23            | DB22        | DB21            | DB21 DB20 DB19 DB18 DB17 DB16 DB15 DB |  |  |  |  |  |  |  | DB12 | DB11 | DB10 | DB9   | DB8    | DB7   | DB6  | DB5 | DB4 | DB3 | DB2 | DB1    | DB0          |

| LDP             | V1          | N8              | N8 N7 N6 N5 N4 N3 N2                  |  |  |  |  |  |  |  | M11  | M10  | M9   | M8    | M7     | M6    | M5   | M4  | М3  | M2  | M1  | C2 (0) | C1 (1)       |

#### MODULATION REGISTER

| PRE-<br>SCALER | IND<br>COUN |      | GFSK MOD<br>CONTROL |      |      | MODULATION DEVIATION |      |      |      |      |      |      | POWER AMPLIFIER |     |     |     |     |     |     | MODULATION<br>SCHEME |     | CONTROL<br>BITS |        |

|----------------|-------------|------|---------------------|------|------|----------------------|------|------|------|------|------|------|-----------------|-----|-----|-----|-----|-----|-----|----------------------|-----|-----------------|--------|

| DB23           | DB22        | DB21 | DB20                | DB19 | DB18 | DB17                 | DB16 | DB15 | DB14 | DB13 | DB12 | DB11 | DB10            | DB9 | DB8 | DB7 | DB6 | DB5 | DB4 | DB3                  | DB2 | DB1             | DB0    |

| P1             | IC2         | IC1  | MC3                 | MC2  | MC1  | D7                   | D6   | D5   | D4   | D3   | D2   | D1   | P7              | P6  | P5  | P4  | P3  | P2  | P1  | S2                   | S1  | C2 (1)          | C1 (0) |

#### FUNCTION REGISTER

|      | TEST MODES |      |      |      |      |      |      |      |      | MUX  | оит  |      | VCO<br>DISABLE | 2   |     | CHARGE<br>PUMP |     | DATA<br>INVERT | CLK <sub>OUT</sub><br>ENABLE | ENABLE | PLL<br>ENABLE | CON<br>BI |        |

|------|------------|------|------|------|------|------|------|------|------|------|------|------|----------------|-----|-----|----------------|-----|----------------|------------------------------|--------|---------------|-----------|--------|

| DB23 | DB22       | DB21 | DB20 | DB19 | DB18 | DB17 | DB16 | DB15 | DB14 | DB13 | DB12 | DB11 | DB10           | DB9 | DB8 | DB7            | DB6 | DB5            | DB4                          | DB3    | DB2           | DB1       | DB0    |

| Т9   | Т8         | T7   | Т6   | T5   | T4   | Т3   | T2   | T1   | M4   | М3   | M2   | M1   | VP1            | CP4 | CP3 | CP2            | CP1 | 11             | PD3                          | PD2    | PD1           | C2 (1)    | C1 (1) |

#### www.DataSheet4U.com

# ADF7011

#### **RF R Register**

| RESE             | RVED |                  | CLKO             | UT    |              | XOE              |      | 4-BIT R          | -VALU | E    |                   |      | 11-E              | BIT FRI                   | EQUEN             | ICY ERI | ROR C             | ORREC                                                 | TION                             |                                                 |     |                                                               | TROL<br>TS                                                                         |

|------------------|------|------------------|------------------|-------|--------------|------------------|------|------------------|-------|------|-------------------|------|-------------------|---------------------------|-------------------|---------|-------------------|-------------------------------------------------------|----------------------------------|-------------------------------------------------|-----|---------------------------------------------------------------|------------------------------------------------------------------------------------|

| DB23             | DB22 | DB21             | DB20 D           | B19 I | DB18         | DB17             | DB16 | DB15             | DB14  | DB13 | DB12              | DB11 | DB10              | DB9                       | DB8               | DB7     | DB6               | DB5                                                   | DB4                              | DB3                                             | DB2 | DB1                                                           | DB0                                                                                |

| R2               | R1   | CL4              | CL3 C            | CL2   | CL1          | X1               | R4   | R3               | R2    | R1   | F11               | F10  | F9                | F8                        | F7                | F6      | F5                | F4                                                    | F3                               | F2                                              | F1  | C2 (0)                                                        | C1 (0)                                                                             |

|                  |      |                  |                  |       | X1<br>0<br>1 | x                |      |                  | TOR O |      |                   |      |                   | )<br>)<br>)<br> <br> <br> |                   |         |                   | F3<br>1<br>1<br>0<br>0<br>1<br>1<br>0<br>0<br>FRACTIO |                                  | F2<br>1<br>1<br>0<br>0<br>1<br>1<br>0<br>0<br>0 |     | F1<br>1<br>0<br>1<br>0<br>0<br>1<br>0<br>0<br>2 <sup>15</sup> | F-COUNTE<br>OFFSET<br>+1023<br>+1022<br>+1<br>+0<br>-1<br>-2<br>-<br>1023<br>-1024 |

|                  |      |                  | ,                |       |              |                  |      | CLKou            |       |      | R4<br>0<br>0<br>0 | 1    | R3<br>0<br>0<br>0 |                           | R2<br>0<br>1<br>1 |         | R1<br>1<br>0<br>1 |                                                       | RF R CC<br>DIVIDE<br>1<br>2<br>3 | DUNTE                                           | R   |                                                               |                                                                                    |

| CL4              | C    | CL3              | CL               | .2    |              | CL1              | DIV  | IDE R            |       |      | 0                 |      | 1                 |                           | 0                 |         | 0                 |                                                       | 4                                |                                                 |     |                                                               |                                                                                    |

| 0<br>0<br>0<br>0 |      | 0<br>0<br>0<br>1 | 0<br>1<br>1<br>0 |       |              | 1<br>0<br>1<br>0 |      | 2<br>4<br>6<br>8 |       |      | 1                 |      | 1                 |                           | 0                 |         | 0                 |                                                       | 12                               |                                                 |     |                                                               |                                                                                    |

|                  |      |                  |                  |       |              | :                |      | :                |       |      | 1                 |      | 1                 |                           | 0                 |         | 1                 |                                                       | 13                               | 3                                               |     |                                                               |                                                                                    |

| 1                |      | 1                |                  |       |              | 0                |      | 24               |       |      | 1                 |      | 1                 |                           | 1                 |         | 0                 |                                                       | 14                               | Ļ                                               |     |                                                               |                                                                                    |

| 1                |      | 1                | 0                |       |              | 1                |      | 26               |       |      | 1                 |      | 1                 |                           | 1                 |         | 1                 |                                                       | 15                               | 5                                               |     |                                                               |                                                                                    |

| 1                |      | 1                | 1                |       |              | 0                |      | 28               |       |      |                   |      |                   |                           |                   |         |                   |                                                       |                                  |                                                 |     |                                                               |                                                                                    |

| 1                |      | 1                | 1                |       |              | 1                |      | 30               |       |      |                   |      |                   |                           |                   |         |                   |                                                       |                                  |                                                 |     |                                                               |                                                                                    |

....

### **RF N Register**

| LD<br>PRECISION | V CO<br>BAND |       |                    | 8-1  | BIT IN   | TEGER- | N    |        |      |        |      |        |      | 12-8             | BIT FRA        | CTION              | AL-N                       |        |                 |          |     |        | TROL<br>TS |

|-----------------|--------------|-------|--------------------|------|----------|--------|------|--------|------|--------|------|--------|------|------------------|----------------|--------------------|----------------------------|--------|-----------------|----------|-----|--------|------------|

| DB23            | DB22         | DB21  | DB20               | DB19 | DB18     | DB17   | DB16 | DB15   | DB14 | DB13   | DB12 | DB11   | DB10 | DB9              | DB8            | DB7                | DB6                        | DB5    | DB4             | DB3      | DB2 | DB1    | DB0        |

| LDP             | V1           | N8    | N7                 | N6   | N5       | N4     | N3   | N2     | N1   | M12    | M11  | M10    | M9   | M8               | M7             | M6                 | M5                         | M4     | M3              | M2       | M1  | C2 (0) | C1 (1)     |

|                 |              |       |                    |      |          | M12    |      | M11    |      | M10    |      |        |      | e.g<br>∑-∆<br>M3 | ., SETT        | ING F =<br>E THE F | = 0 IN F<br>PLL IS /<br>M1 | AN INT | EGER \          | RNS OF   | ;   | ]      |            |

|                 |              |       |                    |      |          | 0      |      | 0      |      | 0      |      |        |      | 1                |                | 0                  | 0                          |        | 4               |          |     |        |            |

|                 |              |       |                    |      |          | 0      |      | 0      |      | 0      |      |        |      | 1                |                | 0                  | 1                          |        | 5               |          |     |        |            |

|                 |              |       |                    |      | 1        | 0      |      | 0      |      | 0      |      |        |      | 1                |                | 1                  | 0                          |        | 6               |          |     |        |            |

|                 |              |       |                    |      | 1        |        |      |        |      |        |      |        |      |                  |                |                    |                            |        |                 |          |     |        |            |

|                 |              |       |                    |      |          | 1      |      | 1      |      | 1      |      |        |      | 1                |                | 0                  | 0                          |        |                 | 1092     |     |        |            |

|                 |              |       |                    |      |          | 1      |      | 1      |      | 1      |      |        |      | 1                |                | 0                  | 1                          |        |                 | 1092     |     |        |            |

|                 |              |       |                    |      |          | 1      |      | 1      |      | 1      |      |        |      | 1                |                | 1                  | 0                          |        |                 | 1094     |     |        |            |

|                 |              |       |                    |      |          | 1      |      | 1      |      | 1      | .    |        |      | 1                |                | 1                  | 1                          |        | 4               | 1095     |     |        |            |

|                 |              |       |                    |      |          |        |      |        |      |        |      |        |      |                  |                |                    |                            |        |                 |          |     |        |            |

|                 |              |       |                    |      |          |        |      |        |      |        |      |        | e.g  | ., MODI          | JLUS D         | IVIDE              | RATIO                      | = 2048 | -> FRA          | CTION    | 1/2 |        |            |

|                 |              |       |                    |      | <b>*</b> |        | _    |        |      |        |      |        |      |                  |                |                    |                            |        | N 00            |          |     | 1      |            |

|                 |              |       |                    | N8   |          | N7     |      | N6     |      | N5     |      | N4     |      | <b>V</b> 3       | N2             | 2                  | N1                         |        | DIVID           | E RAT    |     |        |            |

|                 |              |       |                    | 0    |          | 0<br>0 |      | 0<br>1 |      | 1<br>0 |      | 1<br>0 |      | 1<br>0           | 1              |                    | 1<br>0                     |        |                 | 31<br>32 |     |        |            |

|                 |              |       |                    | 0    |          | Ő      |      | 1      |      | 0      |      | 0      |      | 0                | 0              |                    | 1                          |        |                 | 33       |     |        |            |

|                 |              |       |                    | 0    |          | 0      |      | 1      |      | 0      |      | 0      |      | 0                | 1              |                    | 0                          |        |                 | 34       |     |        |            |

|                 |              |       |                    | 1 :  |          |        |      | :      |      | :      |      | :      |      | :                | :              |                    |                            |        |                 |          |     |        |            |

|                 |              |       |                    |      |          |        |      |        |      |        |      |        |      |                  |                |                    |                            |        |                 |          |     |        |            |

|                 |              |       |                    | 1    |          | 1      |      | 1      |      | 1      |      | 1      |      | 1                | 0              |                    | 1                          |        |                 | 253      |     |        |            |

|                 |              |       |                    | 1    |          | 1      |      | 1      |      | 1      |      | 1      |      | 1                | 1              |                    | 0                          |        |                 | 254      |     |        |            |

|                 |              |       |                    | 1    |          | 1      |      | 1      |      | 1      |      | 1      |      | 1                | 1              |                    | 1                          |        |                 | 255      |     |        |            |

|                 |              |       |                    | L    |          |        |      |        |      |        | _    |        |      |                  |                |                    |                            |        |                 |          |     | 1      |            |

| -               | ¥.,          |       |                    | _    |          |        |      |        |      |        |      |        |      |                  |                |                    |                            |        |                 |          |     |        |            |

|                 | V1           |       | ) BAND<br>MHz)     | 2    |          |        |      |        |      |        |      |        |      |                  |                |                    |                            |        |                 |          |     |        |            |

|                 | 0            |       | -870               | 1    |          |        |      |        |      |        |      |        |      |                  |                |                    |                            |        |                 |          |     |        |            |

|                 | 1            | 433   | -435               |      |          |        |      |        |      |        |      |        |      |                  | P <sup>2</sup> | + 3P + 3           | 3. FOR                     | PRESC  | IS A M<br>CALER | = 8/9, 1 |     |        |            |

| ↓<br>LDP        |              |       | TECT               | ٦    |          |        |      |        |      |        |      |        |      |                  |                |                    |                            |        |                 |          |     |        |            |

| 0               |              | RECIS |                    |      |          |        |      |        |      |        |      |        |      |                  |                |                    |                            |        |                 |          |     |        |            |

| 1               |              |       | S < 15n<br>S < 15n |      |          |        |      |        |      |        |      |        |      |                  |                |                    |                            |        |                 |          |     |        |            |

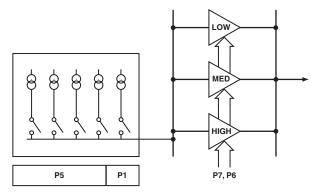

### Modulation Register

| [                       | PRE-<br>SCALER |          |      |             | FSK MOI     |                  |                     | мс               | DULA                                 |                                  | DEVIAT      | ION                                   |                                |                                                                     |             | POWE        | ER AMF      | LIFIEF      | 3      |                      |             | LATION                 |              | TROL<br>TS                                  |                             |

|-------------------------|----------------|----------|------|-------------|-------------|------------------|---------------------|------------------|--------------------------------------|----------------------------------|-------------|---------------------------------------|--------------------------------|---------------------------------------------------------------------|-------------|-------------|-------------|-------------|--------|----------------------|-------------|------------------------|--------------|---------------------------------------------|-----------------------------|

| F                       | DB23           |          | DB21 | DB20        | DB19        | DB18             | DB17                | DB16             | DB15                                 | DB14                             | DB13        | DB12                                  | DB11                           | DB10                                                                | DB9         | DB8         | DB7         | DB6         | DB5    | DB4                  | DB3         | DB2                    | DB1          | DB0                                         |                             |

| [                       | P1             | IC2      | IC1  | МСЗ         | MC2         | MC1              | D7                  | D6               | D5                                   | D4                               | D3          | D2                                    | D1                             | P7                                                                  | P6          | P5          | P4          | P3          | P2     | P1                   | S2          | S1                     | C2 (1)       | C1 (0)                                      |                             |

|                         |                | ŀ        |      |             |             |                  | I                   |                  |                                      |                                  |             |                                       |                                |                                                                     |             |             |             |             |        | S2<br>0<br>1<br>1    |             | S1<br>0<br>1<br>0<br>1 | F:<br>G<br>A | ODULATIC<br>SCHEME<br>SK<br>FSK<br>SK<br>OK |                             |

|                         |                |          | Г    |             | IF AM       |                  | IDE SH              |                  | VING                                 | SELEC                            |             | YDAT                                  | 4 - 0                          |                                                                     | ٦Г          |             | /           | P           | OWFR   |                      | IFIFR ()    |                        | T LEVE       | 1                                           |                             |

|                         | /              |          |      | D7          |             |                  |                     |                  | D2                                   |                                  | D1          |                                       |                                |                                                                     | 16          | P7          |             | P6          |        |                      | P2          |                        | P1           | -                                           |                             |

|                         | <b>,</b>       |          |      | 0<br>0<br>0 | 0<br>1<br>1 |                  |                     |                  | X<br>0<br>0                          |                                  | X<br>0<br>1 | -1                                    | OFF<br>6.0dBr<br>6+1×(         |                                                                     |             | 0<br>0<br>0 |             | 0<br>1<br>1 | ·<br>· |                      | X<br>0<br>0 |                        | X<br>0<br>1  | PA OF<br>-16.00<br>-16+1                    |                             |

|                         |                |          |      | 0<br>1<br>1 | 1<br>0<br>0 |                  | :                   |                  | 1<br>0<br>0                          |                                  | 1<br>0<br>1 | -6                                    | dBm                            | (10/32)                                                             |             | 0<br>1<br>1 |             | 1<br>0<br>0 | :      |                      | 1<br>0<br>0 |                        | 1<br>0       | -6dBr                                       | 81×(10/32)<br>n<br>×(10/32) |

|                         |                |          |      | י<br>1      |             |                  |                     |                  | 1                                    |                                  | י<br>1      | · .                                   | 5+1×(1<br>5+1×(1               |                                                                     |             | י<br>1      |             | 0           |        |                      | 1           |                        | 1<br>1       |                                             | ×(10/32)<br>×(10/32)        |

| ¥                       |                |          |      | 1           | 1           |                  | •                   |                  | 0                                    |                                  | 0           | 2d                                    | Bm<br>1×(10/                   |                                                                     |             | 1<br>1      |             | 1<br>1      |        |                      | 0           |                        | 0<br>1       | 2dBm<br>2+1×(                               |                             |

| P1 RF<br>0 4/5<br>1 8/9 | ;              | SCALER   | 416  | 1<br>1      | 1           |                  | :                   |                  | 1                                    |                                  | 1           | 12                                    | dBm                            |                                                                     |             | 1<br>1      |             | 1<br>1      | :      |                      | 1           |                        | 1            | 12dBm                                       | ı                           |

|                         |                |          |      |             |             | 0<br>0<br>0<br>0 | IF<br>7<br><br><br> | -<br>-<br>-<br>- | DUENC<br>D3<br>0<br>0<br>0<br>0<br>1 | CY SHII<br>0<br>0<br>1<br>1<br>1 |             | ING SE<br>D1<br>0<br>1<br>0<br>1<br>1 | F D<br>PL<br>1 ><br>2 ><br>3 > | ED<br>EVIATI<br>L MOD<br>< FSTEP<br>< FSTEP<br>7 × FSTEP<br>7 × FST | E<br>,<br>, |             |             | – – –       | <br>   | /2 <sup>12</sup><br> | - 1         |                        |              |                                             |                             |

|                         | Г              |          | •    |             |             | 1                | F GAU:              | SSIAN            | FREQ                                 | UENC                             | Y SHIFT     | r KEYI                                | NG SEI                         | LECTEI                                                              | D           |             |             |             |        |                      |             |                        |              |                                             |                             |

|                         |                | ІС       | 2    |             | IC1         | T .              | INDE                | x                | 7                                    |                                  | D7          | D3                                    |                                | D2                                                                  |             | D1          |             | DER F       | ACTOR  |                      |             |                        |              |                                             |                             |

|                         |                |          | )    |             | 0           |                  | COUI<br>16          | NTER             | _                                    |                                  | 0<br>0<br>0 | 0<br>0<br>0                           |                                | 0<br>0<br>1                                                         |             | 0<br>1<br>0 | 0<br>1<br>2 |             |        |                      |             |                        |              |                                             |                             |

|                         |                |          |      |             | 1<br>0      |                  | 32<br>64            |                  |                                      |                                  | 0           | 0                                     |                                | 1                                                                   |             | 1           | 3           |             |        |                      |             |                        |              |                                             |                             |

|                         |                |          |      |             | 1           |                  | 128                 |                  | GFS                                  |                                  | 1           | 1                                     |                                | 1                                                                   |             | 1           | 127         |             |        |                      |             |                        |              |                                             |                             |

|                         |                | 0        | C3   | 0           |             |                  | MC1                 |                  | 0                                    | TROL                             | -           |                                       |                                |                                                                     |             |             |             |             |        |                      |             |                        |              |                                             |                             |

|                         |                | 0        |      | 0           |             |                  | 1                   |                  | 1                                    |                                  |             |                                       |                                |                                                                     |             |             |             |             |        |                      |             |                        |              |                                             |                             |

|                         |                | <u> </u> |      | 1           |             |                  | 1                   |                  | 7                                    |                                  |             |                                       |                                |                                                                     |             |             |             |             |        |                      |             |                        |              |                                             |                             |

....

### **Function Register**

|      |                                                          |      | TES                                                                | ST MOD | ES                                                                      |                                                                              |          |                                                                                                            |                                                                                   | MUX                                                                      | оит                                    |                                 | VCO<br>DISABLE                               | FAST                          | LOCK | CH/<br>PL | ARGE<br>JMP                    | DATA<br>INVERT   | CLK <sub>OUT</sub><br>ENABLE | PA<br>ENABLE | PLL<br>ENABLE                       |                              | TROL<br>TS |

|------|----------------------------------------------------------|------|--------------------------------------------------------------------|--------|-------------------------------------------------------------------------|------------------------------------------------------------------------------|----------|------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|--------------------------------------------------------------------------|----------------------------------------|---------------------------------|----------------------------------------------|-------------------------------|------|-----------|--------------------------------|------------------|------------------------------|--------------|-------------------------------------|------------------------------|------------|

| DB23 | DB22                                                     | DB21 | DB20                                                               | DB19   | DB18                                                                    | DB17                                                                         | DB16     | DB15                                                                                                       | DB14                                                                              | DB13                                                                     | DB12                                   | DB11                            | DB10                                         | DB9                           | DB8  | DB7       | DB6                            | DB5              | DB4                          | DB3          | DB2                                 | DB1                          | DB0        |