# **ADC78H89**

# 7 チャネル、500kSPS、12 ビット A/D コンバータ

### 概要

ADC78H89 は入力 7 チャネルの 12 ビット CMOS A/D コンバータで、低消費電力で動作し変換スループットは 500kSPS です。 ADC78H89 はトラック / ホールド回路を内蔵した逐次比較レジスタ・アーキテクチャを採用しています。 AIN1 から AIN7 まで 7 チャネルの入力を備えています。

シリアル・データ出力はストレート・バイナリ形式で、SPI™、QSPI™、MICROWIRE™ など、広く使われている標準的な DSP シリアル・インタフェースと互換性があります。

ADC78H89 は、アナログ系とデジタル系に個別の電源電圧を与えて動作できます。アナログ電源  $(AV_{DD})$  の電圧範囲は+ 2.7V から+ 5.25V まで、デジタル電源  $(DV_{DD})$  の電圧範囲は+ 2.7V から  $AV_{DD}$  までです。 標準的な消費電力は、+ 3V 動作時で 1.5 mW、+ 5V 動作時で 8.3 mW です。 消費電力を低減できるパワーダウン機能を備えており、+ 3V 動作時で  $0.3 \, \mu \text{W}$ 、+ 5V 動作時で  $0.5 \, \mu \text{W}$  となります。 ADC78H89 は  $16 \, \mu \text{W}$  TSSOP パッケージで提供されます。 産業用温度範囲である-  $40 \, \mu \text{W}$  の動作が保証されています。

# 特長

入力 7 チャネル

可変パワー・マネージメント

独立したアナログ電源とデジタル電源

SPITM/QSPITM/MICROWIRETM/DSP 互換シリアル・インタ

フェース

16ピン TSSOP パッケージ

### 主な仕様

変換レート 500 kSPS DNL ± 1 LSB (max) INL ± 1 LSB (max)

消費電力

3V 電源

1.5 mW ( 代表値 )

5V 電源

8.3 mW ( 代表値 )

### アプリケーション

自動車のナビゲーション・システム ポータブル・システム 医療機器 移動通信

計測器や制御システム

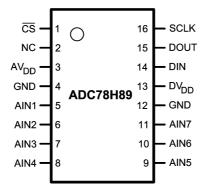

### ピン配置図

### 製品情報

| Order Code    | Temperature Range | Description                        |

|---------------|-------------------|------------------------------------|

| ADC78H89CIMT  | - 40 to + 85      | 16-Lead TSSOP Package              |

| ADC78H89CIMTX | - 40 to + 85      | 16-Lead TSSOP Package, Tape & Reel |

TRI-STATE<sup>®</sup> はナショナル セミコンダクター社の登録商標です。 MICROWIRE™ はナショナル セミコンダクター社の商標です。

QSPI™ および SPI™ はモトローラ(株)の商標です。

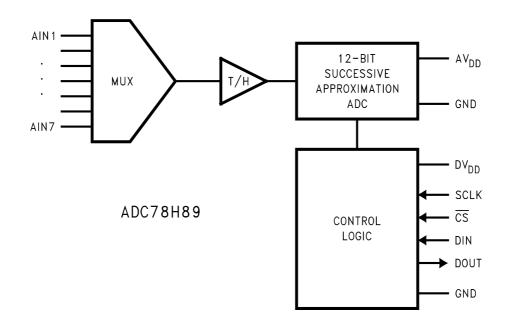

# ブロック図

# 端子説明および等価回路

| 端子番号     | シンボル                        | 等価回路 | 説明                                                                                                                             |

|----------|-----------------------------|------|--------------------------------------------------------------------------------------------------------------------------------|

| アナログ I/O |                             |      | •                                                                                                                              |

| 5 - 11   | AIN1 to AIN7                |      | アナログ入力です。 信号の電圧範囲は 0V から AV <sub>DD</sub> です。                                                                                  |

| 2        | NC                          |      | 内部には接続されていないので、開放のまま使用するかグラウンド<br>に接続してください。                                                                                   |

| デジタル I/O |                             |      | ·                                                                                                                              |

| 16       | SCLK                        |      | デジタル・クロック入力です。 クロック周波数範囲は 10kHz から<br>8MHz で、記載の性能は 8MHz で保証されています。 このクロッ<br>は変換処理と読み出し処理を直接制御します。                             |

| 15       | DOUT                        |      | デジタル・データ出力です。出力サンプルは、SCLK の立ち下がしているに同期して出力されます。                                                                                |

| 14       | DIN                         |      | デジタル・データ入力です。 SCLK の立ち上がりエッジで本ピンからデータが取り込まれ ADC78H89 内部の制御レジスタへ与えられます。                                                         |

| 1        | CS                          |      | チップ・セレクトです。 CS ピンの立ち下がりエッジで変換処理が開始されます。 CS が LOW の間は連続して変換が行われます。                                                              |

| 電源       |                             |      |                                                                                                                                |

| 3        | $\mathrm{AV}_{\mathrm{DD}}$ |      | 正電圧のアナログ電源ピンです。 + 2.7V ~ + 5.25V の安定した電源に接続し、ピンから 1cm 以内に 0.1µF のセラミック・モノリシック・コンデンサと 1µF のタンタル・コンデンサを設けグラウンドに対してバイパスを行なってください。 |

| 13       | DV <sub>DD</sub>            |      | 正電圧のデジタル電源ピンです。 + 2.7V から AV <sub>DD</sub> までの電源を接続し、ピンから 1cm 以内に 0.1 µF のセラミック・モノリシック・コンデンサを設けグラウンドに対してバイパスを行なってください。         |

| 4, 12    | GND                         |      | アナログ電源とデジタル電源のグラウンド・リターンです。 両ピンは 内部的には同一のため、必ず等しい電位となるように接続してください。 万が一、ピン間に電位差が存在すると、デバイスを通してi 大な電流が流れます。                      |

www.national.com/JPN/

### 絶対最大定格 (Note 1)

本データシートには軍用・航空宇宙用の規格は記載されていません。 関連する電気的信頼性試験方法の規格を参照ください。

アナログ電源電圧 AV<sub>DD</sub>  $-0.3V \sim 6.5V$ デジタル電源電圧 AV<sub>DD</sub>  $-0.3V \sim AV_{DD} + 0.3V$ 6.5V(最大値)

任意のピンの対 GND 電圧  $- 0.3V \sim AV_{DD} + 0.3V$ 入力電流 (Note 3) ± 10 mA

ESD 耐性 人体モデル 2500V マシン・モデル 250V

ハンダ付け温度(赤外線)

10 秒 260

+ 150 接合部温度 保存温度範囲 - 65 ~ + 150

# 動作定格

動作温度範囲 -40  $T_A$  +85AV<sub>DD</sub> 電源電圧 + 2.7V ~ + 5.25V +  $2.7V \sim AV_{DD}$ DV<sub>DD</sub> 電源電圧 デジタル入力ピン電圧範囲 -  $0.3V \sim AV_{DD}$

## パッケージ熱抵抗

| パッケージ                               | JA     |  |  |

|-------------------------------------|--------|--|--|

| 16-lead TSSOP on 4-layer, 2 oz. PCB | 96 / W |  |  |

### **ADC78H89** コンバータの電気的特性 (Note 2)

特記のない限り、以下の仕様は  $AV_{DD}$  =  $DV_{DD}$  = + 2.7V ~ + 5.25V、 $f_{SCLK}$  = 8MHz、 $f_{SAMPLE}$  = 500kSPS に適用されます。 太字のリミット値は  $T_A$  =  $T_{MIN}$  ~  $T_{MAX}$  に、それ以外のリミット値は  $T_A$  = 25 に適用されます。

| Symbol                      | Parameter                                                            | Conditions                                                                            | Typical       | Limits   | Units    |

|-----------------------------|----------------------------------------------------------------------|---------------------------------------------------------------------------------------|---------------|----------|----------|

| STATIC C                    | ONVERTER CHARACTERISTICS                                             |                                                                                       |               |          | •        |

|                             | Resolution with No Missing Codes                                     | $AV_{DD} = + 5.0V, DV_{DD} = + 3.3V$                                                  |               | 12       | Bits     |

| INL                         | Integral Non-Linearity                                               | $AV_{DD} = + 5.0V, DV_{DD} = + 3.3V$                                                  |               | ± 1      | LSB(max) |

| DNL                         | Differential Non-Linearity                                           | $AV_{DD}$ = + 5.0V, $DV_{DD}$ = + 3.3V                                                |               | ± 1      | LSB(max) |

| OE                          | Offset Error                                                         | $AV_{DD} = + 5.0V, DV_{DD} = + 3.3V$                                                  |               | ± 2      | LSB(max) |

| OEM                         | Offset Error Match                                                   | $AV_{DD} = + 5.0V, DV_{DD} = + 3.3V$                                                  |               | ± 2      | LSB(max) |

| GE                          | Gain Error                                                           | $AV_{DD} = + 5.0V, DV_{DD} = + 3.3V$                                                  |               | ± 3      | LSB(max) |

| GEM                         | Gain Error Match                                                     | $AV_{DD} = + 5.0V, DV_{DD} = + 3.3V$                                                  |               | ± 3      | LSB(max) |

| DYNAMIC                     | CONVERTER CHARACTERISTICS                                            | $(f_{IN} = 40 \text{ kHz}, -0.02 \text{ dBFS sine wave, unl})$                        | ess otherwise | e noted) |          |

| SINAD                       | Signal-to-Noise Plus Distortion Ratio                                |                                                                                       | 72.6          |          | dB       |

| SNR                         | Signal-to-Noise Ratio                                                |                                                                                       | 72.8          |          | dB       |

| THD                         | Total Harmonic Distortion                                            |                                                                                       | - 86          |          | dB       |

| SFDR                        | Spurious-Free Dynamic Range                                          |                                                                                       | 88            |          | dB       |

| ENOB                        | Effective Number of Bits                                             |                                                                                       | 11.8          |          | bits     |

|                             | Channel-to-Channel Crosstalk                                         |                                                                                       | - 82          |          | dB       |

|                             | Intermodulation Distortion, Second<br>Order Terms                    | $f_a = 40.161 \text{ kHz}, f_b = 41.015 \text{ kHz}$                                  | - 93          |          | JD       |

| IMD                         | Intermodulation Distortion, Third Order Terms                        | $f_a = 40.161 \text{ kHz}, f_b = 41.015 \text{ kHz}$                                  | - 90          |          | dB       |

|                             |                                                                      | $AV_{DD} = + 5V$                                                                      | 11            | MIL      |          |

| FPBW                        | - 3 dB Full Power Bandwidth                                          | $AV_{DD} = + 3V$                                                                      | 8             |          | MHz      |

| POWER S                     | SUPPLY CHARACTERISTICS ( $C_L = 10$                                  | 0 pF)                                                                                 |               |          |          |

| AV <sub>DD</sub> ,          | Analog and Digital Supply Voltages                                   | AV DV                                                                                 |               | 2.7      | V(min)   |

| $\mathrm{DV}_{\mathrm{DD}}$ | Alialog and Digital Supply Voltages                                  | AV <sub>DD</sub> DV <sub>DD</sub>                                                     |               | 5.25     | V(max)   |

|                             | Total Supply Current, Normal Mode (Operational, $\overline{CS}$ low) | $AV_{DD} = DV_{DD} = + 4.75V \text{ to } + 5.25V,$<br>$f_{SAMPLE} = 500 \text{ kSPS}$ | 1.65          | 2.3      | mA(max)  |

|                             |                                                                      | $AV_{DD} = DV_{DD} = + 2.7V \text{ to } + 3.6V,$<br>$f_{SAMPLE} = 500 \text{ kSPS}$   | 0.5           | 2.3      | mA(max)  |

| I <sub>DD</sub>             | Total Supply Current, Shutdown (CS                                   | $AV_{DD} = DV_{DD} = + 4.75V \text{ to } + 5.25V,$<br>$f_{SAMPLE} = 0 \text{ kSPS}$   | 0.1           |          | μA       |

|                             | high)                                                                | $AV_{DD} = DV_{DD} = + 2.7V \text{ to } + 3.6V,$<br>$f_{SAMPLE} = 0 \text{ kSPS}$     | 0.1           |          | μA       |

# **ADC78H89** コンバータの電気的特性 (Note 2)( つづき)

特記のない限り、以下の仕様は  $AV_{DD}$  =  $DV_{DD}$  = + 2.7V ~ + 5.25V、 $f_{SCLK}$  = 8MHz、 $f_{SAMPLE}$  = 500kSPS に適用されます。 太字のリミット値は  $T_A$  =  $T_{MIN}$  ~  $T_{MAX}$  に、それ以外のリミット値は  $T_A$  = 25 に適用されます。

| Symbol            | Parameter                                 | Conditions                                                                     | Typical               | Limits                 | Units       |

|-------------------|-------------------------------------------|--------------------------------------------------------------------------------|-----------------------|------------------------|-------------|

| POWER S           | SUPPLY CHARACTERISTICS $(C_L$             | = 10 pF)                                                                       |                       |                        |             |

|                   | Power Dissipation, Normal Mode            | $AV_{DD} = DV_{DD} = + 4.75V \text{ to } + 5.25V$                              | 8.3                   | 12                     | mW(max)     |

| D                 | (Operational, $\overline{\text{CS}}$ low) | $AV_{DD} = DV_{DD} = + 2.7V \text{ to } + 3.6V$                                | 1.5                   | 8.3                    | mW(max)     |

| $P_{D}$           | Power Dissipation, Shutdown (CS           | $AV_{DD} = DV_{DD} = + 4.75V \text{ to } + 5.25V$                              | 0.5                   |                        | μW          |

|                   | high)                                     | $AV_{DD} = DV_{DD} = + 2.7V \text{ to } + 3.6V$                                | 0.3                   |                        | μW          |

| ANALOG            | INPUT CHARACTERISTICS                     |                                                                                |                       |                        |             |

| V <sub>IN</sub>   | Input Range                               |                                                                                | 0 to AV <sub>DD</sub> |                        | V           |

| $I_{DCL}$         | DC Leakage Current                        |                                                                                |                       | 1                      | µA(max)     |

| C                 | Input Conscitones                         | In Track Mode                                                                  | 33                    |                        | pF          |

| C <sub>INA</sub>  | Input Capacitance                         | In Hold Mode                                                                   | 3                     |                        | pF          |

| DIGITAL I         | NPUT CHARACTERISTICS                      |                                                                                |                       |                        |             |

| V                 | Input High Voltage                        | $DV_{DD} = + 4.75Vto + 5.25V$                                                  |                       | 2.4                    | V(min)      |

| V <sub>IH</sub>   | input High voltage                        | $DV_{DD} = + 2.7V \text{ to } + 3.6V$                                          |                       | 2.1                    | V(min)      |

| $V_{IL}$          | Input Low Voltage                         | $DV_{DD} = + 2.7V \text{ to } + 5.25V$                                         |                       | 0.8                    | V(max)      |

| I <sub>IN</sub>   | Input Current                             | $V_{IN} = 0V \text{ or } DV_{DD}$                                              | 10 nA                 | 1                      | µA(max)     |

| C <sub>IND</sub>  | Input Capacitance                         |                                                                                | 2                     | 4                      | pF(max)     |

| DIGITAL (         | OUTPUT CHARACTERISTICS                    |                                                                                |                       |                        |             |

| $V_{OH}$          | Output High Voltage                       | $I_{\text{SOURCE}}$ = 200 $\mu$ A, DV <sub>DD</sub> = + 2.7V to + 5.25V        |                       | DV <sub>DD</sub> - 0.5 | V(min)      |

| V <sub>OL</sub>   | Output Low Voltage                        | $I_{SINK}$ = 200 $\mu A$                                                       |                       | 0.4                    | V(max)      |

| I <sub>OZL</sub>  | TRI-STATE Leakage Current                 |                                                                                |                       | 1                      | µA(max)     |

| C <sub>OUT</sub>  | TRI-STATE Output Capacitance              |                                                                                | 2                     | 4                      | pF(max)     |

|                   | Output Coding                             |                                                                                | Stra                  | ight (Natural) E       | Binary      |

| AC ELEC           | TRICAL CHARACTERISTICS                    |                                                                                |                       |                        |             |

| $f_{SCLK}$        | Clock Frequency                           |                                                                                |                       | 8                      | MHz(max)    |

| $t_{CON}$         | Conversion Time                           | 1.625 $\mu$ s with $f_{SCLK} = 8 \text{ MHz}$                                  |                       | 13                     | SCLK cycles |

| DC                | Duty Cycle                                |                                                                                | 40-60                 |                        | %           |

| t <sub>TH</sub>   | Track/Hold Acquisition Time               | Full-Scale Step Input                                                          |                       | 3                      | SCLK cycles |

|                   | Throughput Time                           | Conversion Time + Acquisition Time,<br>500 kSPS with f <sub>SCLK</sub> = 8 MHz |                       | 16                     | SCLK cycles |

| f <sub>RATE</sub> | Throughput Rate                           |                                                                                |                       | 500                    | kSPS(min)   |

| t <sub>AD</sub>   | Aperture Delay                            |                                                                                | 4                     |                        | ns          |

Note 1: 「絶対最大定格」とは、個々に適用されるリミット値で、これを超えるとデバイスの有効性が損なわれるおそれがあります。 絶対最大定格条件下では機能的な動作は想定されていません。 最大定格でデバイスを長時間にわたって動作させると信頼性に影響を及ぼすおそれがあります。

Note 2: データシートの min/max リミット値は、設計、テスト、統計解析によって保証されています。

Note 3: 電源ピンを除きます。

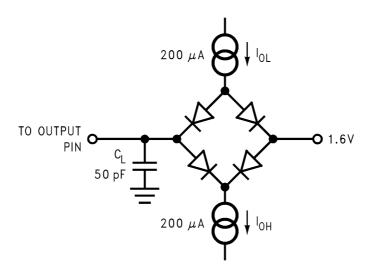

# タイミング・テスト回路

# ADC78H89 タイミング仕様

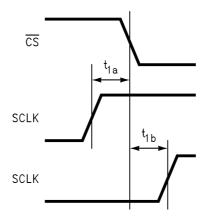

以下の仕様は  $AV_{DD}$  =  $DV_{DD}$  = + 2.7V ~ + 5.25V、 $f_{SCLK}$  = 8MHz、 $C_L$  = 50pF に適用されます。 太字体のリミット値は  $T_A$  =  $T_{MIN}$  ~  $T_{MAX}$  に、それ以外のリミット値は  $T_A$  = 25 に適用されます。

| Symbol               | Parameter                                                                                            | Conditions | Typical | Limits                  | Units       |

|----------------------|------------------------------------------------------------------------------------------------------|------------|---------|-------------------------|-------------|

| t <sub>CONVERT</sub> |                                                                                                      |            |         | 13                      | SCLK Cycles |

| t <sub>ACQ</sub>     | Acquisition Time; Throughput Time = t <sub>CONVERT</sub> + t <sub>ACQ</sub> = 16 x t <sub>SCLK</sub> |            |         | 3                       | SCLK Cycles |

| t <sub>1a</sub>      | High SCLK Setup to Falling CS                                                                        | (Note 4)   |         | 10                      | ns(min)     |

| t <sub>1b</sub>      | Low SCLK Hold to Falling $\overline{\text{CS}}$                                                      | (Note 4)   |         | 10                      | ns(min)     |

| $t_2$                | Delay from CS Until DOUT TRI-STATE® Disabled                                                         |            |         | 30                      | ns(max)     |

| t <sub>3</sub>       | Data Access Time after SCLK<br>Falling Edge                                                          |            |         | 30                      | ns(max)     |

| $t_4$                | Data Setup Time Prior to SCLK<br>Rising Edge                                                         |            |         | 10                      | ns(max)     |

| t <sub>5</sub>       | Data Valid SCLK Hold Time                                                                            |            |         | 10                      | ns(max)     |

| t <sub>6</sub>       | SCLK High Pulse Width                                                                                |            |         | 0.4 x t <sub>SCLK</sub> | ns(min)     |

| t <sub>7</sub>       | SCLK Low Pulse Width                                                                                 |            |         | 0.4 x t <sub>SCLK</sub> | ns(min)     |

| t <sub>8</sub>       | CS Rising Edge to DOUT High-Impedance                                                                |            |         | 20                      | ns(max)     |

Note 4: セットアップ時間  $t_{1a}$ とホールド時間  $t_{1b}$  の規定はありますが、 $\overline{CS}$  を有効な状態にするときのクロック・レベルは任意 (HIGH または LOW) です。

DONT

ADD2

ADD1

# タイミング図 CS t<sub>ACQ</sub> t<sub>CONVERT</sub> CONVERT DOUT Z3 Z2 Z1 Z0 DB11 DB10 DB9 DB8 DB1 DB0

ADC78H89 Serial Timing Diagram

ADDO DONTO DONTO

SCLK and  $\overline{\text{CS}}$  Timing Parameters

### 用語の定義

アパーチャ・ディレイ (APERTURE DELAY) は、変換処理開始後4番目の SCLK 立ち下がりエッジから、変換を行なうために入力信号がホールドされるまでの時間です。

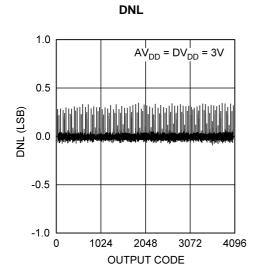

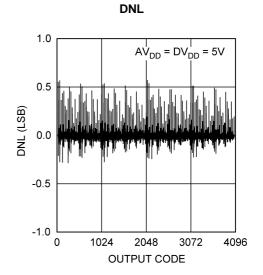

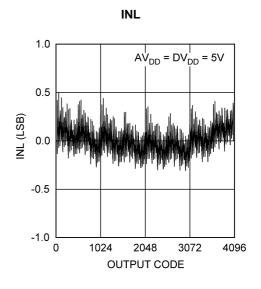

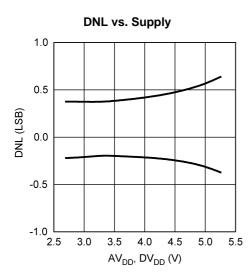

微分非直線性(DIFFERENTIAL NON-LINEARITY: DNL)は、 理想的なステップである ILSB からの最大偏差として表されます。

デューティ・サイクル (DUTY CYCLE) は、繰り返しデジタル波形での、周期に対する HIGH の時間の比です。このデータシートでは SCLK に適用されます。

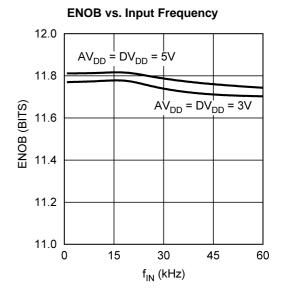

有効ビット (EFFECTIVE NUMBER OF BITS: ENOB) は、信号 /( ノイズ+歪み ) または SINAD の別の規定方法です。 ENOB は (SINAD - 1.76)/6.02 として定義され、この値のビット数をもつ理想的な A/D コンバータに等しいコンバータであることを意味します。

フル・パワー入力帯域 (FULL POWER BANDWIDTH) は、フル・スケール入力に対して再現される出力基本周波数特性で低周波数帯域に対して 3dB 落ちる周波数として測定されます。

ゲイン・エラー**(GAIN ERROR)** は、理想的な値 (V<sub>REF</sub> - 1.5LSB) に対する、オフセット・エラー調整後の、(111...110) から (111...111) に移る最終コード遷移の偏差です。

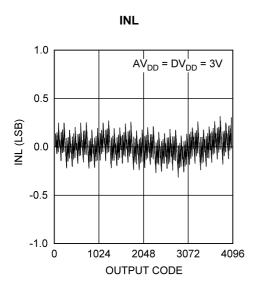

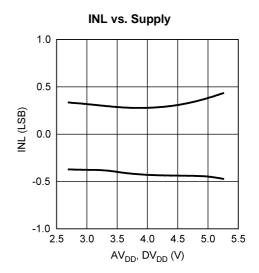

積分非直線性 (INTEGRAL NON-LINEARITY: INL) は、負のフルスケール(最初のコード遷移の1/2LSB下)から正のフルスケール(最後のコード遷移の1/2LSB上)まで引いた直線からそれぞれ個々のコードとの偏差として表されます。この直線から任意のコードとの偏差は、各コード値の中央から測定します。

混変調歪み (INTERMODULATION DISTORTION: IMD) は、A/Dコンバータの入力に2つの近接した周波数を同時に入力し、結果として作り出される追加のスペクトラル成分です。 元の周波数のパワーの合計に対する、両者の2次高調波のパワー(または両者の2次高調波と3次高調波すべてのパワー)の比として定義されています。 IMD は通常 dBFS で表されます。

ミッシング・コード (MISSING CODES) は ADC 出力に現れることのないコードです。 ADC78H89 は、ミッシング・コードが生じないことが保証されています。

オフセット・エラー **(OFFSET ERROR)** は、理想的な値 (GND + 0.5LSB) に対する、(000...000) から (000...001) に移る最初のコード遷移の偏差です。

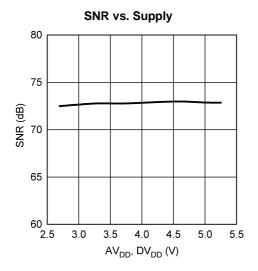

信号 / ノイズ比 (SIGNAL TO NOISE RATIO: SNR) は、クロック信号の 1/2 以下の周波数における、歪みと DC 成分を除いたその他すべてのスペクトラル成分の実効値に対する入力信号の実効値の比として dB で表されます。

信号 /( ノイズ + 歪み ) 比 (SIGNAL TO NOISE PLUS DISTORTION RATIO: (S/N + D) or SINAD) は、クロック信号の 1/2 以下の周波数における、歪みを含め DC 成分を除いたその他すべてのスペクトラル成分の実効値に対する入力信号の実効値の比として dB で表されます。

スプリアス・フリー・ダイナミック・レンジ (SPURIOUS FREE DYNAMIC RANGE: SFDR) は、入力信号の実効値に対するピーク・スプリアス信号との差で、dBで表されます。ここで言うピーク・スプリアス信号とは、出力スペクトラムに現われる任意のスプリアス信号であり、入力に現われるものではありません。

全高調波歪み (TOTAL HARMONIC DISTORTION: THD) は、2 次から 6 次までの高調波の合計出力レベルと基本周波数の出力レベルの比で、dBc で表されます。 全高調波歪み THD は次式から求められます。

THD = 20 x log

$$\sqrt{\frac{f_2^2 + \dots + f_6^2}{f_1^2}}$$

$f_1$  は基本周波数 ( 出力 ) パワーの実効値 (RMS 値 )、 $f_2$  から  $f_6$  は高調波のうち 2 次から 6 次までの高調波のパワーです。

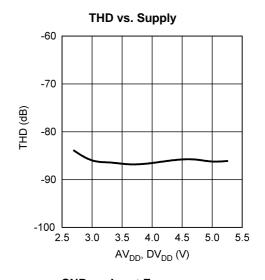

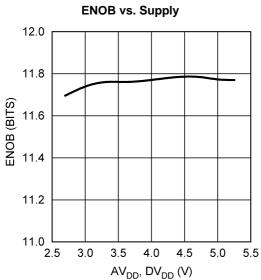

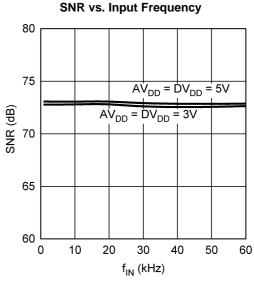

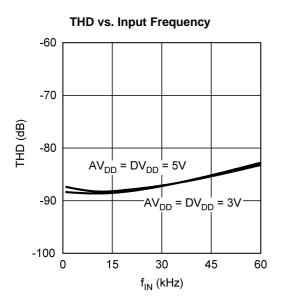

### 代表的な性能特性

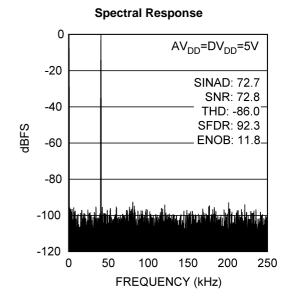

特記のない限り、  $T_{\rm A}$  = + 25 、  $f_{\rm SAMPLE}$  = 500kSPS、  $f_{\rm SCLK}$  = 8MHz、  $f_{\rm IN}$  = 40.2kHz。

### **Spectral Response** 0 $AV_{DD}=DV_{DD}=3V$ -20 SINAD: 72.8 SNR: 73.0 -40 THD: -85.1 SFDR: 90.5 **BFS** ENOB: 11.8--60 -80 -100 -120 50 100 150 200 250 FREQUENCY (kHz)

# 代表的な性能特性(つづき)

特記のない限り、 $T_{\rm A}$  = + 25  $\,$  、 $f_{\rm SAMPLE}$  = 500kSPS、 $f_{\rm SCLK}$  = 8MHz、 $f_{\rm IN}$  = 40.2kHz。

# 代表的な性能特性(つづき)

特記のない限り、 $T_{\rm A}$  = + 25  $\,$  、 $f_{\rm SAMPLE}$  = 500kSPS、 $f_{\rm SCLK}$  = 8MHz、 $f_{\rm IN}$  = 40.2kHz。

### アプリケーション情報

### 1.0 ADC78H89 を使用する

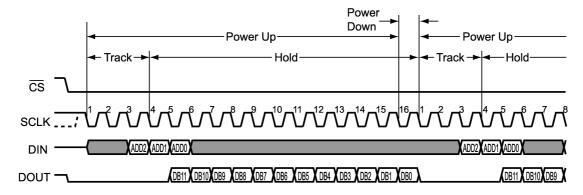

Figure 1 に、ADC78H89 の機能図を示します。また、ADC78H89 のシリアル・インタフェースのタイミング図を、前述の「タイミング図」の項にそれぞれ示します。 CS はチップ・セレクトを表し、ADC78H89 の変換サイクルとシリアル・データ転送フレームの開

始をトリガします。また SCLK(シリアル・クロック)は、変換処理 とシリアル・データ・タイミングの両方を制御します。 DOUT はシリ アル・データ出力ピンで、変換結果がシリアル・データ・ストリー ムとして出力されます。 シリアル・データ・ピン DIN のデータは ADC78H89 の制御レジスタに書き込まれます。

FIGURE 1. ADC78H89 Functional Diagram

変換処理とシリアル・データ・タイミングは SCLK によって制御されます。 1 回の変換処理には 16 SCLK サイクルが必要です。 CSを LOW にすると変換処理が始まります。 複数の変換処理は、 CSの立ち下がりエッジから立ち上がりエッジまでの単一のシリアル・フレームとして連続して実行されます。 CSを LOW に保持している間は ADC78H89 は変換を継続します。

CS を LOW にすると、変換処理が始まると同時に制御レジスタに書き込みが行われます。 制御レジスタに書き込まれた新しい設定値は次の変換処理に作用します。 すなわち、入力チャネル選択の設定と対応する出力との間には 1 サンプル分の遅延が存在します。

でSをLOWにするとADC78H89の基本動作である変換処理とデータ出力が始まります。この時点でDOUT ピンは TRI-STATE から復帰します。でSがLOWになったあと最初のSCLKの立ち下がリでコンバータはトラック・モードに移り、入力信号の取り込みを開始します。でSがLOWになった時点から数えて、入力信号の取り込み処理に必要な時間は3SCLKです。この取り込み時間はtACQとして規定されています。SCLKの4番目の立ち下がリエッジでコンバータはトラック・モードからホールド・モードへと移り、アナログ入力信号はこの時点でサンブルされます(Figure 1参照)。変換処理の完了には続いて13SCLKサイクルを必要とします。

でS が HIGH となっていて変換が行われていないときは、SCLK を HIGH または LOW に保持して ADC78H89 をアイドル状態にできます (でS が HIGH のときに、当然ながら SCLK を入力したままにしても構いません)。 クロックがアイドルかどうかによらず、でS が LOW になったあとの最初の SCLK の立ち下がフェッジで変換処理が始ま)ます (Figure 1 参照)。 SCLKを LOW の状態でアイドルさせた場合、SCLK の最初の立ち上がフェッジは動作には関係

しません。 続く立ち下がリエッジでデバイスはトラック・モードに移り変換処理が始まります。 どのような場合でも変換処理の完了には合計で16個の立ち下がリエッジが必要です。

ADC78H89からの読み出し完了には16 SCLK サイクルを必要とします。サンプルの各ビット(先頭の4つのゼロを含む)は SCLK の立ち下がりで出力され、次の立ち上がりエッジの時点で DOUT 上のデータは有効となります。 ADC78H89は4ビットの先頭ゼロを DOUT から出力したあと、最上位ビットから順に12ビットのデータを出力します。 最終データビット DB0は16番目の SCLK の立ち下がりエッジで出力され、次の立ち上がりエッジの時点で DOUT 上のデータは有効となります。 CS が LOW になった直後の SCLK エッジは、アプリケーションによって立ち上がりエッジになる場合と立ち下がりエッジになる場合があります。

変換の実行とともに制御情報を制御レジスタに書き込まなければ なりません。 各変換の最初の 8 個の SCLK 立ち上がりエッジで 制御レジスタへの書き込みが行われます。 ADC78H89 を動作させるには、DIN に適切なデータを与えて制御レジスタを設定する 必要があります。 現在の変換処理で制御レジスタに書き込んだデータによって、次の変換処理でサンプルされる入力チャネルが 決まります。

制御レジスタへの書き込みは CS が LOW になったあとの SCLK の立ち上がリエッジで行われ、DIN データは最上位ビットから順に書き込まれます。DIN ピンからのデータ書き込みは 16 SCLK を必要とする変換データの読み出しと並行して行われます。 制御レジスタには前半の 8 SCLK の立ち上がリエッジで書き込まれ、後半の8 SCLK の立ち上がリエッジの DIN は無視されます。 Table 1 はビットの機能で、MSB は書き込みデータの最初のビットを示します。電源立ち上げ時のデフォルト値は、制御レジスタの全ビットゼロです。

**Table 1. Control Register Bits**

| Bit 7 (MSB) | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------------|-------|-------|-------|-------|-------|-------|-------|

| DONTC       | DONTC | ADD2  | ADD1  | ADD0  | DONTC | DONTC | DONTC |

www.national.com/JPN/

### アプリケーション情報(つづき)

**Table 2. Control Register Bit Descriptions**

| ビット           | シンボル  | 説明                                        |

|---------------|-------|-------------------------------------------|

| 7, 6, 2, 1, 0 | DONTC | Don't care です。 このビットの値はデバイスの動作には影響を与えません。 |

| 5             | ADD2  | この 3 ビットで、次の CS の立ち下がりエッジでサンプルおよび変換処理を行う  |

| 4             | ADD1  | 入力チャネルを指定します。ビット・パターンと選択されるチャネルの対応を Table |

| 3             | ADD0  | 3 に示します。                                  |

**Table 3. Input Channel Selection**

| ADD2 | ADD1 | ADD0 | Input Channel  |

|------|------|------|----------------|

| 0    | 0    | 0    | AIN1 (Default) |

| 0    | 0    | 1    | AIN2           |

| 0    | 1    | 0    | AIN3           |

| 0    | 1    | 1    | AIN4           |

| 1    | 0    | 0    | AIN5           |

| 1    | 0    | 1    | AIN6           |

| 1    | 1    | 0    | AIN7           |

| 1    | 1    | 1    | GND            |

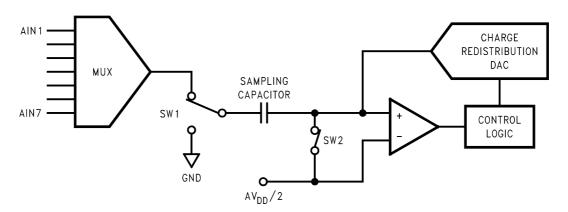

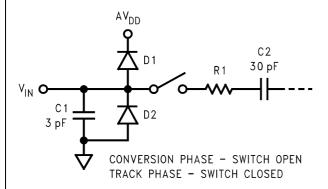

### 2.0 ADC78H89 の動作

ADC78H89 は、電荷再配分 D/A コンバータを採用した逐次比較型の A/D コンバータです。 トラック・モードとホールド・モードで

の ADC78H89 の簡略ブロック図を Figure 2、3 にそれぞれ示します。 Figure 2 では ADC78H89 はトラック・モードになっています。 スイッチ SW1 によってマルチプレクサで選択された 7 チャネルのうちの 1 つのチャネルがサンプリング・コンデンサに接続され、SW2 によってコンパレータ入力は平衡に保たれます。 ADC78H89 は、CS が LOW になったあと 3 SCLK サイクルにわたってこの状態を保ちます。

Figure 3 では ADC78H89 はホールド・モードにあります。 サンプリング・コンデンサは入力電圧 (正確には AV<sub>DD</sub>/2 と VIN との電位差)を保持したまま SW1 によってグラウンドに接続され、またスイッチ SW2 はコンパレータを非平衡状態にします。制御回路はコンパレータが平衡状態になるまで、サンプリング・コンデンサに一定量の電荷 (電位)を加算または減算するように電荷再配分型DACを制御します。 コンパレータが平衡になった時点で DAC に与えられているデジタル・ワードがアナログ入力電圧のデジタル値を表します。 ADC78H89 は、CS が LOW になったあと後半の 13 SCLK サイクルにわたってこの状態を保ちます。

FIGURE 2. ADC78H89 in Track Mode

FIGURE 3. ADC78H89 in Hold Mode

# アプリケーション情報(つづき)

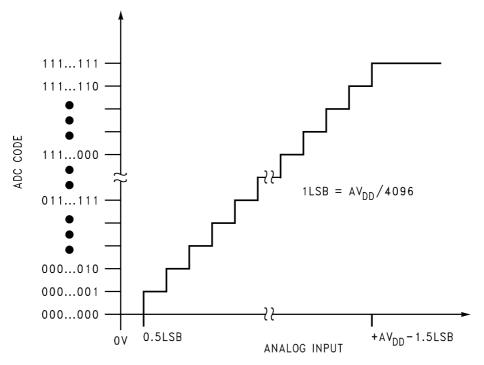

### 3.0 ADC78H89 の伝達関数

ADC78H89 の出力フォーマットはストレート・バイナリ形式です。 コード遷移は連続する LSB と LSB の中点付近で生じます。 ADC78H89 の LSB の大きさは AV $_{

m DD}/4096$  です。 理想的な伝達特性を Figure 4 に示します。

FIGURE 4. Ideal Transfer Characteristics

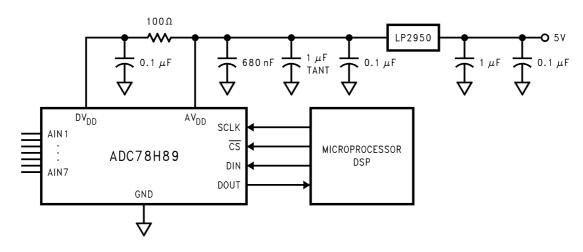

### 4.0 回路例

ADC78H89 の代表的アプリケーション回路の例を Figure 5 に示します。この例では、固定電圧出力または電圧外部設定機能を備えるナショナルの LP2950 低ドロップアウト電圧レギュレータを用いて、アナログ電圧とデジタル電圧の両方を供給しています。アナログ電源は ADC78H89 近傍に配置したコンデンサ・ネットワークでバイパスしています。 デジタル電源は直列抵抗を介してアナ

ログ電源と分離し、さらにバイパス・コンデンサで安定化を図っています。 ADC78H89 はアナログ電圧 (AV<sub>DD</sub>) をリファレンス電圧として使用するため、AV<sub>DD</sub> を可能なかぎリクリーンにすることが重要です。 ADC78H89 の消費電力は小さいため、高精度な電圧リファレンスを電源として用いて性能を最大限に引き出すことも可能です。図では4本の信号をマイクロプロセッサまたは DSP に接続しています。

FIGURE 5. Sample Circuit

### アプリケーション情報(つづき)

### 5.0 アナログ入力

ADC78H89 入力段の等価回路を Figure 6 に示します。 各変換の始まりでは ADC78H89 が持つ 7 つのチャネルのうち 1 つが単純なトランスファ・ゲート回路によって選択されます。 したがって、等価回路は Figure 6 のように表せます。 ダイオード D1 と D2 はアナログ入力の ESD 保護を目的としています。 アナログ入力電圧が AV<sub>DD</sub> + 300mV を超えるか GND - 300mV を下回ると、これら ESD ダイオードが即座に導通し電流をサブストレートに流します

Figure 6に示すコンデンサ C1の代表値は3pFで、主にピンの容量成分です。抵抗R1はマルチプレクサとトラック/ホールド回路のスイッチに起因するもので代表値は500です。コンデンサ C2はADC78H89のサンプリング・コンデンサで代表値は30pFです。サンプリング・コンデンサの充電で生じる入力の変動を吸収させる意味で、ADC78H89は低インピーダンスの信号源で駆動されたときに最も高い性能を発揮します。そのため、動的な性能がクリティカルなアプリケーションでは、入力信号は低出力インピーダンス・アンプで駆動しなければなりません。また、ADC78H89をAC信号のサンプルに使用する場合は、バンドパス・フィルタまたはローパス・フィルタを使用して高調波やノイズを排除するとTHDとSNRの改善が図れます。

FIGURE 6. Equivalent Input Circuit

### 6.0 デジタル入力とデジタル出力

ADC78H89 のデジタル入力 (SCLK、 $\overline{\text{CS}}$ 、DIN) は上限電圧が規定されており、また  $\text{AV}_{\text{DD}}$  を超えてはなりません。デジタル入力 ピンはラッチアップが起こらない よう設計されていますが、 $\text{DV}_{\text{DD}}$  確定後に SCLK、 $\overline{\text{CS}}$ 、DIN に印加したほうがリスクを低減できます。

### 7.0 パワー・マネージメント

ADC78H89 はデュアル電源のデバイスです。 2 系統の電源は ESD 保護回路を共有しているため、電源を適切な順序で印加しなければならない点に注意が必要です。 ESD ダイオードの導通を避けるため、デジタル電源  $(DV_{DD})$  電圧はアナログ電源  $(AV_{DD})$  電圧を 300mV 以上超えてはなりません。したがって、ADC78H89のアナログ電源はデジタル電源はりまたに (または同時に) 印加する必要があります。

でSをLOW にすると ADC78H89 は全面的にパワーアップし、でSを HIGH にすると全面的にパワーダウンします。 ただし例外があり、変換処理の 16番目の SCLK 立ち下がりエッジから、次の変換処理の 1番目の SCLK 立ち下がりエッジまでの間は、ADC78H89 は自動的にパワーダウン・モードに移ります (Figure 1参照)。

ADC78H89 では、パワーアップ後の待ち動作やダミー変換サイク ルは必要ありません。 デバイスはパワーアップ直後の最初の変換から、完全な分解能でアナログ入力を取り込みます。

ADC78H89 は連続して複数の変換を実行します。 各変換には 16 SCLK サイクルがかかります。 ADC78H89 は  $\overline{CS}$  が LOW の 間は変換を継続して実行します。

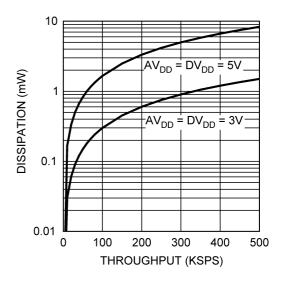

単位時間あたりの変換数を減らせば、設計者はスループットと消費電力のどちらかを優先できます。ADC78H89の最大消費電力の代表値とスループットの関係を Figure 7 に示します。パワーアップ状態への移行はきわめて高速なため、消費電力の計算に考慮する必要はありません。消費電力は単純に、ノーマル・モードで動作する時間の割り合いにノーマル・モード時の消費電力 (たとえば  $AV_{DD}=DV_{DD}=+2.7V~+3.6V$  の場合で 8.3mW)を乗算し、シャットダウン・モードで動作する時間の割り合いにシャットダウン・モード時の消費電力 ( $AV_{DD}=DV_{DD}=+2.7V~+3.6V$ で 0.3mW)を乗算して、両者を加算すれば求められます。

FIGURE 7. Typical Power Dissipation vs. Throughput

# 外形寸法図 単位は millimeters Α 6.4 (16X 0.42) 3.2 (14X 0.65) GAGE PLANE RECOMMENDED LAND PATTERN 0.2 C B A ALL LEAD TIPS SEATING PLANE 0.6±0.1 DETAIL A SEE DETAIL A 1.1 MAX TYP (0.9) Ç

16-Lead TSSOP

Order Number ADC78H89CIMT, ADC78H89CIMTX

NS Package Number MTC16

DIMENSIONS ARE IN MILLIMETERS

DIMENSIONS IN ( ) FOR REFERENCE ONL

# 生命維持装置への使用について

14X 0.65

弊社の製品はナショナル セミコンダクター社の書面による許可なくしては、生命維持用の装置またはシステム内の重要な部品として使用することはできません。

1. 生命維持用の装置またはシステムとは (a) 体内に外科的に使用されることを意図されたもの、または (b) 生命を維持あるいは支持するものをいい、ラベルにより表示される使用法に従って適切に使用された場合に、これの不具合が使用者に身体的障害を与えると予想されるものをいいます。

16X 0.19-0.30 ⊕ 0.13M A BS CS

2. 重要な部品とは、生命維持にかかわる装置またはシステム内のすべての部品をいい、これの不具合が生命維持用の装置またはシステムの不具合の原因となりそれらの安全性や機能に影響を及ぼすことが予想されるものをいいます。

MTC16 (Rev D)

# ナショナル セミコンダクター ジャパン株式会社

本社 / 〒 135-0042 東京都江東区木場 2-17-16

TEL.(03)5639-7300

技術資料(日本語/英語)はホームページより入手可能です。

その他のお問い合わせはフリーダイヤルをご利用ください。

www.national.com/JPN/

0120-666-116