## ADC574A

# Microprocessor-Compatible ANALOG-TO-DIGITAL CONVERTER

## **FEATURES**

- COMPLETE 12-BIT A/D CONVERTER WITH REFERENCE, CLOCK, AND 8-, 12-, or 16-BIT MICROPROCESSOR BUS INTERFACE

- IMPROVED PERFORMANCE SECOND SOURCE FOR 574A-TYPE A/D CONVERTERS

Conversion Time: 25µs max Bus Access Time: 150ns max

Ao Input: Bus Contention During Read

**Operation Eliminated**

- DUAL IN-LINE PLASTIC, PLCC AND HERMETIC CERAMIC

- FULLY SPECIFIED FOR OPERATION ON ±12V OR ±15V SUPPLIES

- NO MISSING CODES OVER TEMPERATURE:

0°C to +75°C: ADC574AJ and K Grades -55°C to +125°C: ADC574ASH, TH

### **DESCRIPTION**

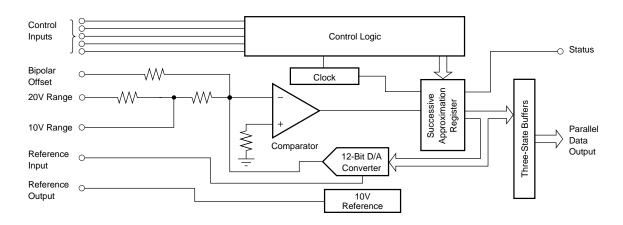

The ADC574A is a 12-bit successive approximation analog-to-digital converter, utilizing state-of-the-art CMOS and laser-trimmed bipolar die custom-designed

for freedom from latch-up and for optimum AC performance. It is complete with a self-contained +10V reference, internal clock, digital interface for microprocessor control, and three-state outputs.

The reference circuit, containing a buried zener, is laser-trimmed for minimum temperature coefficient. The clock oscillator is current-controlled for excellent stability over temperature. Full-scale and offset errors may be externally trimmed to zero. Internal scaling resistors are provided for the selection of analog input signal ranges of 0V to  $\pm$ 10V, 0V to  $\pm$ 20V,  $\pm$ 5V, and  $\pm$ 10V.

The converter may be externally programmed to provide 8- or 12-bit resolution. The conversion time for 12 bits is factory set for 25µs maximum.

Output data are available in a parallel format from TTL-compatible three-state output buffers. Output data are coded in straight binary for unipolar input signals and bipolar offset binary for bipolar input signals.

The ADC574A, available in both industrial and military temperature ranges, requires supply voltages of +5V and  $\pm 12V$  or  $\pm 15V$ . It is packaged in a 28-pin plastic DIP, and a hermetic side-brazed ceramic DIP.

International Airport Industrial Park

• Mailing Address: PO Box 11400

• Tucson, AZ 85734

• Street Address: 6730 S. Tucson Blvd.

• Tucson, AZ 85706

Tel: (520) 746-1111

• Twx: 910-952-1111

• Cable: BBRCORP

• Telex: 066-6491

• FAX: (520) 889-1510

• Immediate Product Info: (800) 548-6132

## **SPECIFICATIONS**

#### **ELECTRICAL**

At  $T_A$  = +25°C,  $V_{CC}$  = +12V or +15V,  $V_{EE}$  = -12V or -15V, and  $V_{LOGIC}$  = +5V unless otherwise specified.

|                                                                                                 | А          | DC574AJP, JH     | I, SH                 | AD                                |     |          |                        |  |

|-------------------------------------------------------------------------------------------------|------------|------------------|-----------------------|-----------------------------------|-----|----------|------------------------|--|

| PARAMETER                                                                                       | MIN        | TYP              | MAX                   | MIN                               | TYP | MAX      | UNITS                  |  |

| RESOLUTION                                                                                      |            |                  | 12                    |                                   |     | *        | Bits                   |  |

| INPUTS                                                                                          |            |                  |                       | 1                                 |     |          | 1                      |  |

| ANALOG                                                                                          |            |                  |                       |                                   |     |          |                        |  |

| Voltage Ranges: Unipolar                                                                        |            | 0 to +10, 0 to + | 20                    |                                   | *   |          | V                      |  |

| Bipolar                                                                                         | l          | ±5, ±10          |                       |                                   | *   |          | V                      |  |

| Impedance: 0 to +10V, ±5V<br>±10V, 0V to +20V                                                   | 4.7<br>9.4 | 5<br>10          | 5.3<br>10.6           | *                                 | *   | *        | kΩ<br>kΩ               |  |

| <b>DIGITAL</b> (CE, $\overline{CS}$ , R/ $\overline{C}$ , A <sub>O</sub> , 12/ $\overline{8}$ ) |            |                  |                       |                                   |     |          |                        |  |

| Over Temperature Range<br>Voltages: Logic 1                                                     | +2         |                  | +5.5                  | *                                 |     | *        | V                      |  |

| Logic 0                                                                                         | -0.5       |                  | +0.8                  | *                                 |     | *        | ľ                      |  |

| Current                                                                                         | <b>-</b> 5 | 0.1              | +5                    | *                                 | *   | *        | μA                     |  |

| Capacitance                                                                                     |            | 5                |                       |                                   | *   |          | pF                     |  |

| TRANSFER CHARACTERISTICS                                                                        | •          | •                | •                     | •                                 | •   | '        | •                      |  |

| ACCURACY                                                                                        |            |                  |                       |                                   |     |          |                        |  |

| At +25°C                                                                                        |            |                  |                       | 1                                 |     |          |                        |  |

| Linearity Error Unipolar Offset Error (Adjustable to Zero)                                      |            |                  | ±1<br>±2              | 1                                 |     | ±1/2     | LSB<br>LSB             |  |

| Bipolar Offset Error (Adjustable to Zero)                                                       |            |                  | ±2<br>±10             |                                   |     | ±4       | LSB                    |  |

| Full-Scale Calibration Error <sup>(1)</sup>                                                     |            |                  |                       | 1                                 |     |          |                        |  |

| (Adjustable to Zero)                                                                            |            |                  | ±0.25                 |                                   |     | *        | % of FS <sup>(2)</sup> |  |

| No Missing Codes Resolution (Diff. Linearity)                                                   | 11         |                  |                       | 12                                |     |          | Bits                   |  |

| Inherent Quantization Error                                                                     |            | ±1/2             |                       |                                   | *   |          | LSB                    |  |

| T <sub>MIN</sub> to T <sub>MAX</sub> Linearity Error: J, K Grades                               |            |                  | ±1                    |                                   |     | ±1/2     | LSB                    |  |

| S, T Grades                                                                                     |            |                  | ±1                    |                                   |     | ±3/4     | LSB                    |  |

| Full-Scale Calibration Error                                                                    |            |                  |                       |                                   |     |          |                        |  |

| Without Initial Adjustment(1): J, K Grades                                                      |            |                  | ±0.47                 |                                   |     | ±0.37    | % of FS                |  |

| S, T Grades                                                                                     |            |                  | ±0.75                 |                                   |     | ±0.5     | % of FS                |  |

| Adjusted to Zero at +25°C: J, K Grades                                                          |            |                  | ±0.22                 |                                   |     | ±0.12    | % of FS                |  |

| S, T Grades No Missing Codes Resolution (Diff. Linearity)                                       | 1 11       |                  | ±0.5                  | 12                                |     | ±0.25    | % of FS<br>Bits        |  |

| TEMPERATURE COEFFICIENTS (T <sub>MIN</sub> to T <sub>MAX</sub> ) <sup>(3)</sup>                 |            |                  |                       |                                   |     |          |                        |  |

| Unipolar Offset: J, K Grades                                                                    |            |                  | ±10                   |                                   |     | ±5       | ppm/°C                 |  |

| S, T Grades                                                                                     |            |                  | ±5                    |                                   |     | ±2.5     | ppm/°C                 |  |

| Max Change: All Grades                                                                          |            |                  | ±2                    |                                   |     | ±1       | LSB                    |  |

| Bipolar Offset: All Grades                                                                      |            |                  | ±10                   |                                   |     | ±5       | ppm/°C                 |  |

| Max Change: J, K Grades<br>S. T Grades                                                          |            |                  | ±2<br>±4              |                                   |     | ±1<br>±2 | LSB<br>LSB             |  |

| Full-Scale Calibration: J, K Grades                                                             |            |                  | ±45                   |                                   |     | ±25      | ppm/°C                 |  |

| S, T Grades                                                                                     |            |                  | ±50                   |                                   |     | ±25      | ppm/°C                 |  |

| Max Change: J, K Grades                                                                         |            |                  | ±9                    |                                   |     | ±5       | LSB                    |  |

| S, T Grades                                                                                     |            |                  | ±20                   |                                   |     | ±10      | LSB                    |  |

| POWER SUPPLY SENSITIVITY                                                                        |            |                  |                       |                                   |     |          |                        |  |

| Change in Full-Scale Calibration $+13.5V < V_{CC} < +16.5V$ or $+11.4V < V_{CC} < +12.6V$       |            |                  | ±2                    | 1                                 |     | ±1       | LSB                    |  |

| $-16.5V < V_{EE} < -13.5V \text{ or } -12.6V < V_{EE} < -11.4V$                                 |            |                  | ±2                    | 1                                 |     | ±1       | LSB                    |  |

| +4.5V < V <sub>LOGIC</sub> < +5.5V                                                              |            |                  | ±1/2                  |                                   |     | *        | LSB                    |  |

| CONVERSION TIME (4)                                                                             |            |                  |                       |                                   |     |          |                        |  |

| 8-Bit Cycle                                                                                     | 10         | 13               | 17                    | *                                 | *   | *        | μs                     |  |

| 12-Bit Cycle                                                                                    | 15         | 20               | 25                    | *                                 | •   | •        | μs                     |  |

| OUTPUTS                                                                                         | ı          | T                | 1                     | T                                 | I   | 1        | I                      |  |

| DIGITAL (DB <sub>11</sub> –DB <sub>0</sub> , STATUS)                                            |            |                  |                       |                                   |     |          |                        |  |

| (Over Temperature Range)                                                                        |            |                  | <br>  Inipolar Strain | ht Binon (USB)                    | I   |          |                        |  |

| Output Codes: Unipolar Bipolar                                                                  |            |                  |                       | ht Binary (USB)<br>t Binary (BOB) |     |          |                        |  |

| Logic Levels: Logic 0 (I <sub>SINK</sub> = 1.6mA)                                               |            |                  | +0.4                  | <br>                              | l   | *        | V                      |  |

| Logic 1 (I <sub>SOURCE</sub> = 500μA)                                                           | +2.4       |                  |                       | *                                 |     |          | V                      |  |

| Leakage, Data Bits Only, High -Z State                                                          | -5         | 0.1              | +5                    | *                                 | *   | *        | μΑ                     |  |

| Capacitance                                                                                     |            | 5                |                       | 1                                 | *   |          | pF                     |  |

## SPECIFICATIONS (CONT)

#### **ELECTRICAL**

At  $T_A = +25^{\circ}C$ ,  $V_{CC} = +12V$  or +15V,  $V_{EE} = -12V$  or -15V, and  $V_{LOGIC} = +5V$  unless otherwise specified.

|                                                                       | AD          | C574AJP, JH, | SH    | AD  |         |   |         |

|-----------------------------------------------------------------------|-------------|--------------|-------|-----|---------|---|---------|

| PARAMETERS                                                            | MIN         | TYP          | MAX   | MIN | MIN TYP |   | UNITS   |

| INTERNAL REFERENCE VOLTAGE                                            | .00         | .40.0        | .404  | *   |         | * | , ,     |

| Voltage<br>Source Current Available for External Loads <sup>(5)</sup> | +9.9<br>2.0 | +10.0        | +10.1 | *   |         |   | V<br>mA |

| POWER SUPPLY REQUIREMENTS                                             | •           | •            |       |     |         | • | •       |

| Voltage: V <sub>CC</sub>                                              | +11.4       |              | +16.5 | *   |         | * | V       |

| V <sub>EE</sub>                                                       | -11.4       |              | -16.5 | *   |         | * | V       |

| V <sub>LOGIC</sub>                                                    | +4.5        |              | +5.5  | *   |         | * | V       |

| Current: I <sub>CC</sub>                                              |             | 3.5          | 5     |     | *       | * | mA      |

| I <sub>EE</sub>                                                       |             | 15           | 20    |     | *       | * | mA      |

| I <sub>LOGIC</sub>                                                    |             | 9            | 15    |     | *       | * | mA      |

| Power Dissipation (±15V Supplies)                                     |             | 325          | 450   |     | *       | * | mW      |

| <b>TEMPERATURE RANGE</b> (Ambient: $T_{MIN}$ , $T_{MAX}$ )            |             |              |       |     |         |   |         |

| Specifications: J, K Grades                                           | 0           |              | +75   | *   |         | * | °C      |

| S, T Grades                                                           | <b>-</b> 55 |              | +125  | *   |         | * | °C      |

| Storage                                                               | -65         |              | +150  | *   |         | * | °C      |

<sup>\*</sup> Same specifications as ADC574AJP, AJH, ASH.

NOTES: (1) With fixed 50Ω resistor from REF OUT to REF IN. This parameter is also adjustable to zero at ±25°C (see Optional External Full Scale and Offset Adjustments section). (2) FS in this specification table means Full Scale Range. That is, for a ±10V input range, FS means 20V; for a 0 to +10V range, FS means 10V. The term Full Scale for these specifications instead of Full-Scale Range is used to be consistent with other vendors' 574 and 574A type specifications tables. (3) Using internal reference. (4) See Controlling the ADC574A section for detailed information concerning digital timing. (5) External loading must be constant during conversion. The reference output requires no buffer amplifier with either ±12V or ±15V power supplies.

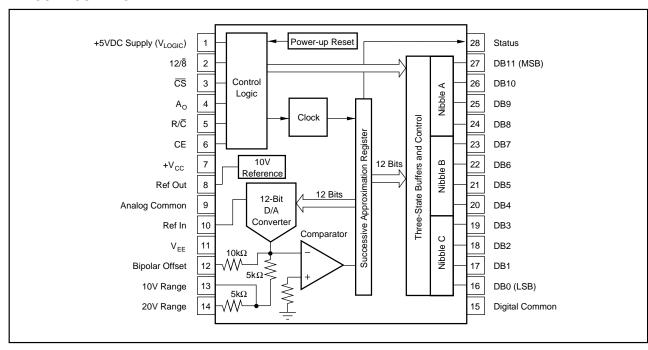

#### **PIN CONFIGURATION**

#### **ABSOLUTE MAXIMUM RATINGS**

| V <sub>CC</sub> to Digital Common                                                | 0V to +16.5V                       |

|----------------------------------------------------------------------------------|------------------------------------|

| V <sub>EE</sub> to Digital Common                                                | 0V to -16.5V                       |

| V <sub>LOGIC</sub> Digital Common                                                |                                    |

| Analog Common to Digital Common                                                  | ±1V                                |

| Control Inputs (CE, $\overline{CS}$ , A <sub>O</sub> , 12/8, R/ $\overline{C}$ ) |                                    |

| to Digital Common                                                                | 0.5V to V <sub>LOGIC</sub> +0.5V   |

| Analog Inputs (Ref In, Bipolar Offset, 10VIN)                                    |                                    |

| to Analog Common                                                                 | ±16.5V                             |

| 20V <sub>IN</sub> to Analog Common                                               | ±24V                               |

| Ref Out                                                                          | Indefinite Short to Common,        |

|                                                                                  | Momentary Short to V <sub>CC</sub> |

| Max Junction Temperature                                                         |                                    |

| Power Dissipation                                                                | 1000mW                             |

| Lead Temperature (soldering,10s)                                                 |                                    |

| Thermal Resistance, $\theta_{JA}$ : Ceramic                                      | 50°C/W                             |

| Plastic                                                                          | 100°C/W                            |

|                                                                                  |                                    |

CAUTION: These devices are sensitive to electrostatic discharge. Appropriate I.C. handling procedures should be followed.

#### **BURN-IN SCREENING**

Burn-in screening is available for both plastic and ceramic package ADC574s. Burn-in duration is 160 hours at the temperature (or equivalent combination of time and temperature) indicated below:

Plastic "-BI" models: +85°C Ceramic "-BI" models: +125°C

All units are 100% electrically tested after burn-in is completed. To order burn-in, add "-BI" to the base model number (e.g., ADC574AKP-BI).

#### **ORDERING INFORMATION**

| MODEL     | PACKAGE                                                                             | TEMPERATURE<br>RANGE | LINEARITY<br>ERROR MAX<br>(T <sub>MIN</sub> TO T <sub>MAX</sub> ) |

|-----------|-------------------------------------------------------------------------------------|----------------------|-------------------------------------------------------------------|

| ADC574AJP | Plastic DIP Plastic DIP Ceramic DIP Ceramic DIP Ceramic DIP Ceramic DIP Ceramic DIP | 0°C to +75°C         | ±1LSB                                                             |

| ADC574AKP |                                                                                     | 0°C to +75°C         | ±1/2LSB                                                           |

| ADC574AJH |                                                                                     | 0°C to +75°C         | ±1LSB                                                             |

| ADC574AKH |                                                                                     | 0°C to +75°C         | ±1/2LSB                                                           |

| ADC574ASH |                                                                                     | -55°C to +125°C      | ±1/SB                                                             |

| ADC574ATH |                                                                                     | -55°C to +125°C      | ±3/4LSB                                                           |

#### **BURN-IN SCREENING OPTION**

See text for details.

| MODEL                                                                                        | PACKAGE                                                                             | TEMPERATURE<br>RANGE                                                                               | BURN-IN TEMP<br>(160 Hours)                            |

|----------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|--------------------------------------------------------|

| ADC574AJP-BI<br>ADC574AKP-BI<br>ADC574AJH-BI<br>ADC574AKH-BI<br>ADC574ASH-BI<br>ADC574ATH-BI | Plastic DIP Plastic DIP Ceramic DIP Ceramic DIP Ceramic DIP Ceramic DIP Ceramic DIP | 0°C to +75°C<br>0°C to +75°C<br>0°C to +75°C<br>0°C to +75°C<br>-55°C to +125°C<br>-55°C to +125°C | +85°C<br>+85°C<br>+125°C<br>+125°C<br>+125°C<br>+125°C |

#### **PACKAGE INFORMATION**

| MODEL     | PACKAGE     | PACKAGE DRAWING<br>NUMBER <sup>(1)</sup> |

|-----------|-------------|------------------------------------------|

| ADC574AJP | Plastic DIP | 215                                      |

| ADC574AKP | Plastic DIP | 215                                      |

| ADC574AJH | Ceramic DIP | 149                                      |

| ADC574AKH | Ceramic DIP | 149                                      |

| ADC574ASH | Ceramic DIP | 149                                      |

| ADC574ATH | Ceramic DIP | 149                                      |

NOTE: (1) For detailed drawing and dimension table, please see end of data sheet, or Appendix D of Burr-Brown IC Data Book.

The information provided herein is believed to be reliable; however, BURR-BROWN assumes no responsibility for inaccuracies or omissions. BURR-BROWN assumes no responsibility for the use of this information, and all use of such information shall be entirely at the user's own risk. Prices and specifications are subject to change without notice. No patent rights or licenses to any of the circuits described herein are implied or granted to any third party. BURR-BROWN does not authorize or warrant any BURR-BROWN product for use in life support devices and/or systems.

# DISCUSSION OF SPECIFICATIONS

#### **LINEARITY ERROR**

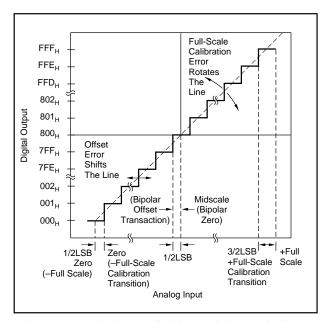

Linearity error is defined as the deviation of actual code transition values from the ideal transition values. Ideal transition values lie on a line drawn through zero (or minus full scale for bipolar operation) and plus full scale. The zero value is located at an analog input value 1/2LSB before the first code transition ( $000_H$  to  $001_H$ ). The full-scale value is located at an analog value 3/2LSB beyond the last code transition (FFE $_H$  to FFF $_H$ ) (see Figure 1).

FIGURE 1. ADC574A Transfer Characteristics Terminology.

Thus, for a converter connected for biopolar operation and with a full-scale range (or span) of 20V ( $\pm 10$ V), the zero value of -10V is 2.44mV below the first code transition ( $000_H$  to  $001_H$  at -9.99756V) and the plus full-scale value of +10V is 7.32mV above the last code transition (FFE<sub>H</sub> to FFF<sub>H</sub> at +9.99268) (see Table I).

## NO MISSING CODES (DIFFERENTIAL LINEARITY ERROR)

A specification which guarantees no missing codes requires that every code combination to appear in a monotonicallyincreasing sequence as the analog input is increased throughout the range. Thus, every input code width (quantum) must have a finite width. If an input quantum has a value of zero (a differential linearity error of -1LSB), a missing code will occur.

ADC574AKP, KN, KH and TH grades are guaranteed to have no missing codes to 12-bit resolution over their respective specification temperature ranges.

#### UNIPOLAR OFFSET ERROR

An ADC574A connected for unipolar operation has an analog input range of 0V to plus full scale. The first output code transition should occur at an analog input value 1/2 LSB above 0V. Unipolar offset error is defined as the deviation of the actual transition value from the ideal value. The unipolar offset temperature coefficient specifies the change of this transition value versus a change in ambient temperature.

#### **BIPOLAR OFFSET ERROR**

A/D converter specifications have historically defined bipolar offset as the first transition value above the minus full-scale value. The ADC574A specification, however, follows the terminology defined for the 574 converter several years ago. Thus, bipolar offset is located near the midscale value of 0V (bipolar zero) at the output code transition  $7FF_{\rm H}$  to  $800_{\rm H}$ .

Bipolar offset error for the ADC574A is defined as the deviation of the actual transition value from the ideal transition value located 1/2LSB below 0V. The bipolar offset temperature coefficient specifies the maximum change of the code transition value versus a change in ambient temperature.

#### **FULL SCALE CALIBRATION ERROR**

The last output transition (FFE $_{\rm H}$  to FFF $_{\rm H}$ ) occurs for an analog input value 3/2LSB below the nominal full-scale value. The full-scale calibration error is the deviation of the actual analog value at the last transition point from the ideal value. The full-scale calibration temperature coefficient specifies the maximum change of the code transition value versus a change in ambient temperature.

#### POWER SUPPLY SENSITIVITY

Electrical specifications for the ADC574A assume the application of the rated power supply voltages of +5V and  $\pm 12V$  or  $\pm 15V$ . The major effect of power supply voltage

| BINARY (BIN) OUTPUT                                                                                      | INPUT VOLTAGE RANGE AND LSB VALUES                               |                                            |                                            |                                            |                                            |  |  |  |  |  |  |  |

|----------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|--------------------------------------------|--------------------------------------------|--------------------------------------------|--------------------------------------------|--|--|--|--|--|--|--|

| Analog Input Voltage Range                                                                               | Defined as:                                                      | ±10V                                       | ±5V                                        | 0 to +10V                                  | 0 to +20V                                  |  |  |  |  |  |  |  |

| One Least Significant Bit (LSB)                                                                          | FSR<br>2 <sup>n</sup><br>n = 8<br>n = 12                         | 20V<br>2 <sup>n</sup><br>78.13mV<br>4.88mV | 10V<br>2 <sup>n</sup><br>39.06mV<br>2.44mV | 10V<br>2 <sup>n</sup><br>39.06mV<br>2.44mV | 20V<br>2 <sup>n</sup><br>78.13mV<br>4.88mV |  |  |  |  |  |  |  |

| Output Transition Values<br>FFE <sub>H</sub> to FFF <sub>H</sub><br>7FF <sub>H</sub> to 800 <sub>H</sub> | +Full-Scale Calibration<br>Midscale Calibration (Bipolar Offset) | +10V - 3/2LSB<br>0 - 1/2LSB                | +5 - 3/2LSB<br>0 - 1/2LSB                  | +10V - 3/2LSB<br>+5V - 1/2LSB              | +10V - 3/2LSB<br>±10V - 1/2LSB             |  |  |  |  |  |  |  |

TABLE I. Input Voltages, Transition Values, and LSB Values.

deviations from the rated values will be a small change in the full-scale calibration value. This change, of course, results in a proportional change in all code transition values (i.e., a gain error). The specification describes the maximum change in the full-scale calibration value from the initial value for a change in each power supply voltage.

#### **TEMPERATURE COEFFICIENTS**

The temperature coefficients for full-scale calibration, unipolar offset and bipolar offset specify the maximum change from the  $+25^{\circ}$ C value to the value at  $T_{MIN}$  or  $T_{MAX}$

#### **QUANTIZATION UNCERTAINTY**

Analog-to-digital converters have an inherent quantization error of  $\pm 1/2$ LSB. This error is a fundamental property of the quantization process and cannot be eliminated.

#### **CODE WIDTH (QUANTUM)**

Code width, or quantum, is defined as the range of analog input values for which a given output code will occur. The ideal code width is 1LSB.

### INSTALLATION

#### LAYOUT PRECAUTIONS

Analog (pin 9) and digital (pin 15) commons are not connected together internally in the ADC574A, but should be connected together as close to the unit as possible and to an analog common ground plane beneath the converter on the component side of the board. In addition, a wide conductor pattern should run directly from pin 9 to the analog supply common, and a separate wide conductor pattern from pin 15 to the digital supply common. Analog common (pin 9) typically carries +8mA.

If the single-point system common cannot be established directly at the converter, pin 9 and 15 should still be connected together at the converter; a single wide conductor pattern then connects these two pins to the system common. In either case, the common return of the analog input signal should be referenced to pin 9 of the ADC. This prevents any voltage drops that might occur in the power supply common returns from appearing in series with the input signal.

Coupling between analog input and digital lines should be minimized by careful layout. For instance, if the lines must cross, they should do so at right angles. Parallel analog and digital lines should be separated from each other by a pattern connected to common.

If external full scale and offset potentiometers are used, the potentiometers and associated resistors should be located as close to the ADC574A as possible. If no trim adjustments are used, the fixed resistors should likewise be as close as possible.

#### POWER SUPPLY DECOUPLING

Logic and analog power supplies should be bypassed with  $10\mu F$  tantalum-type capacitors located close to the converter

to obtain noise-free operation. Noise on the power supply lines can degrade the converter's performance. Noise and spikes from a switching power supply are especially troublesome.

#### **ANALOG SIGNAL SOURCE IMPEDANCE**

The signal source supplying the analog input signal to the ADC574A will be driving into a nominal DC input impedance of either  $5k\Omega$  or  $10k\Omega$ . However, the output impedance of the driving source should be very low, such as the output impedance provided by a wideband, fast-settling operational amplifier. Transients in A/D input current are caused by the changes in output current of the internal D/A converter as it tests the various bits. The output voltage of the driving source must remain constant while furnishing these fast current changes. If the application requires a sample/hold, select a sample/hold with sufficient bandwidth to preserve the accuracy or use a separate wideband buffer amplifier to lower the output impedance.

#### RANGE CONNECTIONS

The ADC574A offers four standard input ranges: 0V to +10V, 0V to +20V,  $\pm5V$ , and  $\pm10V$ . If a 10V input range is required, the analog input signal should be connected to pin 13 of the converter. A signal requiring a 20V range is connected to pin 14. In either case the other pin of the two is left unconnected. Full-scale and offset adjustments are described below.

To operate the converter with a 10.24V~(2.5mV~LSB) or 20.48V~(5mV~LSB) input range, insert a  $120\Omega,~1\%$  metal-film resistor in series with pin 13 for the 10.24V range, or a  $240\Omega,~1\%$  metal-film resistor in series with pin 14 for the 20.48V range. Offset and gain adjustments are still performed as described below. However, you must recalculate full-scale adjustment voltages proportionately. A fixed metal-film resistor can be used because the input impedance of the ADC574A is trimmed to less than  $\pm 6\%$  of the nominal value.

#### CALIBRATION

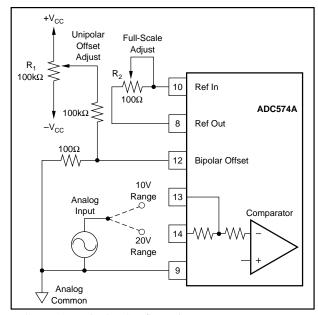

## OPTIONAL EXTERNAL FULL-SCALE AND OFFSET ADJUSTMENTS

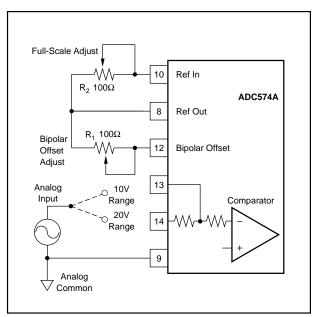

Offset and full-scale errors may be trimmed to zero using external offset and full-scale trim potentiometers connected to the ADC574A as shown in Figures 2 and 3 for unipolar and bipolar operation.

# CALIBRATION PROCEDURE — UNIPOLAR RANGES

If adjustment of unipolar offset and full scale is not required, replace  $R_2$  with a 50 $\Omega$ , 1% metal-film resistor and connect pin 12 to pin 9, omitting the adjustment network.

If adjustment is required, connect the converter as shown in Figure 2. Sweep the input through the end-point transition voltage (0V + 1/2LSB; +1.22mV for the 10V range, +2.44mV

FIGURE 2. Unipolar Configuration.

for the 20V range) that causes the output code to be DB0 ON (high). Adjust potentiometer  $R_1$  until DB0 is alternately toggling ON and OFF with all other bits OFF. Then adjust full scale by applying an input voltage of nominal full-scale value minus 3/2LSB, the value which should cause all bits to be ON. This value is +9.9963V for the 10V range and +19.9927V for the 20V range. Adjust potentiometer  $R_2$  until bits DB1-DB11 are ON and DB0 is toggling ON and OFF.

#### **CALIBRATION PROCEDURE—BIPOLAR RANGES**

If external adjustments of full-scale and bipolar offset are not required, the potentiometers may be replaced by  $50\Omega$ , 1% metal-film resistors.

If adjustments are required, connect the converter as shown in Figure 3. The calibration procedure is similar to that described above for unipolar operation, except that the offset adjustment is performed with an input voltage which is 1/2LSB above the minus full-scale value (-4.9988V for the  $\pm 5V$  range, -9.9976V for the  $\pm 10V$  range). Adjust  $R_1$  for

FIGURE 3. Bipolar Configuration.

DB0 to toggle ON and OFF with all other bits OFF. To adjust full-scale, apply a DC input signal which is 3/2LSB below the nominal plus full-scale value (+4.9963V for  $\pm 5V$  range, +9.9927V for  $\pm 10V$  range) and adjust  $R_2$  for DB0 to toggle ON and OFF with all other bits ON.

## **CONTROLLING THE ADC574A**

The Burr-Brown ADC574A can be easily interfaced to most microprocessor systems and other digital systems. The microprocessor may take full control of each conversion, or the converter may operate in a stand-alone mode, controlled only by the  $R/\overline{C}$  input. Full control consists of selecting an 8- or 12-bit conversion cycle, initiating the conversion, and reading the output data when ready—choosing either 12 bits all at once, or 8 bits followed by 4 bits in a left-justified format. The five control inputs (12/ $\overline{8}$ ,  $\overline{CS}$ ,  $A_O$ ,  $R/\overline{C}$ , and CE) are all TTL/CMOS-compatible. The functions of the control inputs are described in Table III. The control function truth table is listed in Table III.

| PIN<br>DESIGNATION     | DEFINITION                                            | FUNCTION                                                                                                                                                                                                                                                   |

|------------------------|-------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CE (Pin 6)             | Chip Enable (active high)                             | Must be high ("1") to either initiate a conversion or read output data. 0-1 edge may be used to initiate a conversion.                                                                                                                                     |

| CS (Pin 3)             | Chip Select (active low)                              | Must be low ("0") to either initiate a conversion or read output data. 1-0 edge may be used to initiate a conversion.                                                                                                                                      |

| R/Ĉ(Pin 5)             | Read/Convert<br>("1" = read)<br>("0" = convert)       | Must be low ("0") to initiate either 8- or 12-bit conversions. 1-0 edge may be used to initiate a conversion.  Must be high ("1") to read output data. 0-1 edge may be used to initiate a read operation.                                                  |

| A <sub>O</sub> (Pin 4) | Byte Address<br>Short Cycle                           | In the start-convert mode, $A_O$ selects 8-bit ( $A_O$ = "1") or 12-bit ( $A_O$ = "0") conversion mode. When reading output data in two 8-bit bytes, $A_O$ = "0" accesses 8 MSBs (high byte) and $A_O$ = "1" accesses 4 LSBs and trailing "0s" (low byte). |

| 12/8 (Pin 2)           | Data Mode Select<br>("1" = 12 bits)<br>("0" = 8 bits) | When reading output data, $12/\overline{8}$ = "1" enables all 12 output bits simultaneously. $12/\overline{8}$ = "0" will enable the MSBs or LSBs as determined by the A <sub>O</sub> line.                                                                |

TABLE II. ADC574A Control Line Functions.

| CE                                   | cs                                                                                                    | R/Ĉ                                                 | 12/8                                      | A <sub>o</sub>                                 | OPERATION                                                                                                                                                                                                                           |

|--------------------------------------|-------------------------------------------------------------------------------------------------------|-----------------------------------------------------|-------------------------------------------|------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0<br>X<br>^<br>1<br>1<br>1<br>1<br>1 | X<br>1<br>0<br>0<br>\<br>\<br>\<br>\<br>\<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0 | X<br>X<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>1<br>1 | X<br>X<br>X<br>X<br>X<br>X<br>X<br>1<br>0 | X<br>X<br>0<br>1<br>0<br>1<br>0<br>1<br>X<br>0 | None None Initiate 12-bit conversion Initiate 8-bit conversion Initiate 12-bit conversion Initiate 8-bit conversion Initiate 12-bit conversion Initiate 8-bit conversion Enable 12-bit output Enable 8 MSBs only Enable 4 LSBs plus |

|                                      |                                                                                                       |                                                     |                                           |                                                | 4 trailing zeros                                                                                                                                                                                                                    |

TABLE III. Control Input Truth Table.

#### STAND-ALONE OPERATION

For stand-alone operation, control of the converter is accomplished by a single control line connected to  $R/\overline{C}$ . In this mode  $\overline{CS}$  and  $A_O$  are connected to digital common and CE and  $12/\overline{8}$  are connected to  $V_{LOGIC}$  (+5V). The output data are presented as 12-bit words. The stand-alone mode is used in systems containing dedicated input ports which do not require full bus interface capability.

Conversion is initiated by a high-to-low transition of  $R/\overline{C}$ . The three-state data output buffers are enabled when  $R/\overline{C}$  is high and STATUS is low. Thus, there are two possible modes of operation; conversion can be initiated with either positive or negative pulses. In either case the  $R/\overline{C}$  pulse must remain low for a minimum of 50ns.

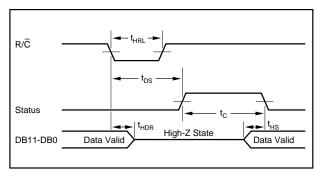

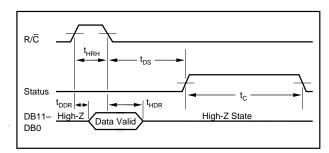

Figure 4 illustrates timing when conversion is initiated by an  $R/\overline{C}$  pulse which goes low and returns to the high state during the conversion. In this case, the three-state outputs go to the high-impedance state in response to the falling edge of  $R/\overline{C}$  and are enabled for external access of the data after completion of the conversion. Figure 5 illustrates the timing when conversion is initiated by a positive  $R/\overline{C}$  pulse. In this mode the output data from the previous conversion is enabled during the positive portion of  $R/\overline{C}$ . A new conversion is started on the falling edge of  $R/\overline{C}$ , and the three-state outputs return to the high-impedance state until the next occurrence of a high  $R/\overline{C}$  pulse. Table IV lists timing specifications for stand-alone operation.

| SYMBOL                                                                     | PARAMETER                                                                                           | MIN             | TYP | MAX | UNITS                |

|----------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|-----------------|-----|-----|----------------------|

| t <sub>HRL</sub><br>t <sub>DS</sub><br>t <sub>HDR</sub><br>t <sub>HS</sub> | Low R/C Pulse Width<br>STS Delay from R/C<br>Data Valid After R/C Low<br>STS Delay After Data Valid | 50<br>25<br>300 | 400 | 200 | ns<br>ns<br>ns<br>ns |

| t <sub>HRH</sub><br>t <sub>DDR</sub>                                       | High R/C Pulse Width Data Access Time                                                               | 150             |     | 150 | ns<br>ns             |

TABLE IV. Stand-Alone Mode Timing.

#### **FULLY CONTROLLED OPERATION**

#### **Conversion Length**

Conversion length (8-bit or 12-bit) is determined by the state of the  $A_O$  input, which is latched upon receipt of a conversion start transition (described below). If  $A_O$  is latched high, the conversion continues for 8 bits. The full 12-bit conversion will occur if  $A_O$  is low. If all 12 bits are read following

FIGURE 4. R/C Pulse Low—Outputs Enabled After Conversion

FIGURE 5. R/C Pulse High—Outputs Enabled Only While R/C Is High.

an 8-bit conversion, the 3LSBs (DB0-DB2) will be low (logic 0) and DB3 will be high (logic 1). A<sub>O</sub> is latched because it is also involved in enabling the output buffers. No other control inputs are latched.

#### **CONVERSION START**

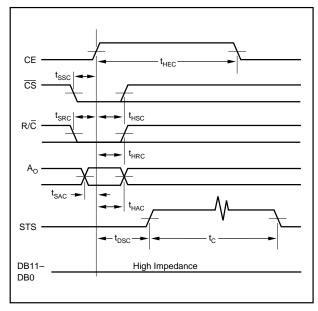

The converter is commanded to initiate a conversion by a transition occurring on any of three logic inputs (CE,  $\overline{CS}$ , and  $R/\overline{C}$ ) as shown in Table III. Conversion is initiated by the last of the three to reach the required state and thus all three may be dynamically controlled. If necessary, all three may change states simultaneously, and the nominal delay time is the same regardless of which input actually starts conversion. If it is desired that a particular input establish the actual start of conversion, the other two should be stable a minimum of 50ns prior to the transition of that input. Timing relationships for start of conversion timing are illustrated in Figure 6. The specifications for timing are contained in Table V.

The STATUS output indicates the current state of the converter by being in a high state only during conversion. During this time the three state output buffers remain in a high-impedance state, and therefore data cannot be read during conversion. During this period additional transitions of the three digital inputs which control conversion will be ignored, so that conversion cannot be prematurely terminated or restarted. However, if  $A_{\rm O}$  changes state after the beginning of conversion, any additional start conversion transition will latch the new state of  $A_{\rm O}$ , possibly resulting in an incorrect conversion length (8 bits vs 12 bits) for that conversion.

| SYMBOL           | PARAMETER                           | MIN | TYP | MAX  | UNIT |

|------------------|-------------------------------------|-----|-----|------|------|

| Convert Mode     |                                     |     |     |      |      |

| t <sub>DSC</sub> | STS Delay from CE                   |     | 60  | 200  | ns   |

| t <sub>HEC</sub> | CE Pulse Width                      | 50  | 30  |      | ns   |

| t <sub>SSC</sub> | CS to CE Setup time                 | 50  | 20  |      | ns   |

| t <sub>HSC</sub> | CS low during CE high               | 50  | 20  |      | ns   |

| t <sub>SRC</sub> | $R/\overline{C}$ to CE setup        | 50  | 0   |      | ns   |

| t <sub>HRC</sub> | R/C low during CE high              | 50  | 20  |      | ns   |

| t <sub>SAC</sub> | A <sub>O</sub> to CE setup          | 0   |     |      | ns   |

| t <sub>HAC</sub> | A <sub>O</sub> valid during CE high | 50  | 20  |      | ns   |

| t <sub>C</sub>   | Conversion time, 12-bit cycle       | 15  | 20  | 25   | μs   |

|                  | 8-bit cycle                         | 10  | 13  | 17   | μs   |

| Read Mode        |                                     |     |     |      |      |

| t <sub>DD</sub>  | Access time from CE                 |     | 75  | 150  | ns   |

| t <sub>HD</sub>  | Data valid after CE low             | 25  | 35  |      | ns   |

| t <sub>HL</sub>  | Output float delay                  |     | 100 | 150  | ns   |

| t <sub>SSR</sub> | CS to CE setup                      | 50  | 0   |      | ns   |

| t <sub>SRR</sub> | R/C to CE setup                     | 0   |     |      | ns   |

| t <sub>SAR</sub> | A <sub>O</sub> to CE setup          | 50  | 25  |      | ns   |

| t <sub>HSR</sub> | CS valid after CE low               | 0   |     |      | ns   |

| t <sub>HRR</sub> | R/C high after CE low               | 0   |     |      | ns   |

| t <sub>HAR</sub> | A <sub>O</sub> valid after CE low   | 50  |     |      | ns   |

|                  | STS delay after data valid          | 300 | 400 | 1000 | ns   |

TABLE V. Timing Specifications.

FIGURE 6. Conversion Cycle Timing.

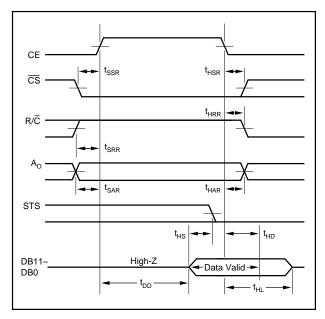

#### **READING OUTPUT DATA**

After conversion is initiated, the output data buffers remain in a high-impedance state until the following four logic conditions are simultaneously met: R/ $\overline{C}$  high, STATUS low, CE high, and  $\overline{CS}$  low. Upon satisfaction of these conditions the data lines are enabled according to the state of inputs  $12/\overline{8}$  and  $A_O$ . See Figure 7 and Table V for timing relationships and specifications.

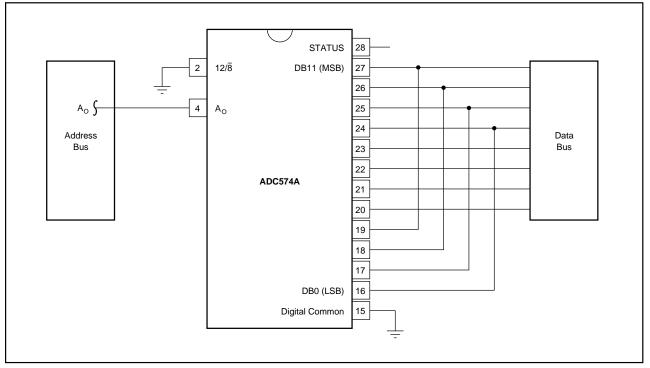

In most applications the  $12/\overline{8}$  input will be hard-wired in either the high or low condition, although it is fully TTL-and CMOS-compatible and may be actively driven if

FIGURE 7. Read Cycle Timing.

desired. When  $12/\overline{8}$  is high, all 12 output lines (DB0–DB11) are enabled simultaneously for full data word transfer to a 12-bit or 16-bit bus. In this situation the  $A_O$  state is ignored.

When  $12/\overline{8}$  is low, the data is presented in the form of two 8-bit bytes, with selection of the byte of interest accomplished by the state of  $A_O$  during the read cycle. Connection of the ADC574A to an 8-bit bus for transfer of left-justified data is illustrated in Figure 8. The  $A_O$  input is usually driven by the least significant bit of the address bus, allowing storage of the output data word in two consecutive memory locations.

When  $A_{\rm O}$  is low, the byte addressed contains the 8MSBs. When  $A_{\rm O}$  is high, the byte addressed contains the 4LSBs from the conversion followed by four logic zeros which have been forced by the control logic. The left-justified formats of the two 8-bit bytes are shown in Figure 8. The design of the ADC574A guarantees that the  $A_{\rm O}$  input may be toggled at any time with no damage to the converter; the outputs which are tied together as illustrated in Figure 9 cannot be enabled at the same time.

In the majority of applications the read operation will be attempted only after the conversion is complete and the STATUS output has gone low. In those situations requiring the earliest possible access to the data, the read may be started as much as  $1.15\mu s$  ( $t_{DD}$  max +  $t_{HS}$  min) before STATUS goes low. Refer to Figure 7 for these timing relationships.

| Word 1    |      |      |     |     |     |     |     |     |     |     | Word | 2   |     |     |     |     |

|-----------|------|------|-----|-----|-----|-----|-----|-----|-----|-----|------|-----|-----|-----|-----|-----|

| Processor | DB7  | DB6  | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 | DB7 | DB6 | DB5  | DB4 | DB3 | DB2 | DB1 | DB0 |

| Converter | DB11 | DB10 | DB9 | DB8 | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1  | DB0 | 0   | 0   | 0   | 0   |

| l '       |      |      |     |     |     |     |     |     |     |     | •    |     |     |     |     |     |

FIGURE 8. 12-Bit Data Format for 8-Bit Systems.

FIGURE 9. Connection to an 8-Bit Bus.