#### ADVANCE INFORMATION

September 2006

# ADC14C065/ADC14C080/ADC14C095/ADC14C105 14-Bit, 65/80/95/105 MSPS A/D Converter

## **General Description**

NOTE: This is Advance Information for products currently in development. ALL specifications are design targets and are subject to change.

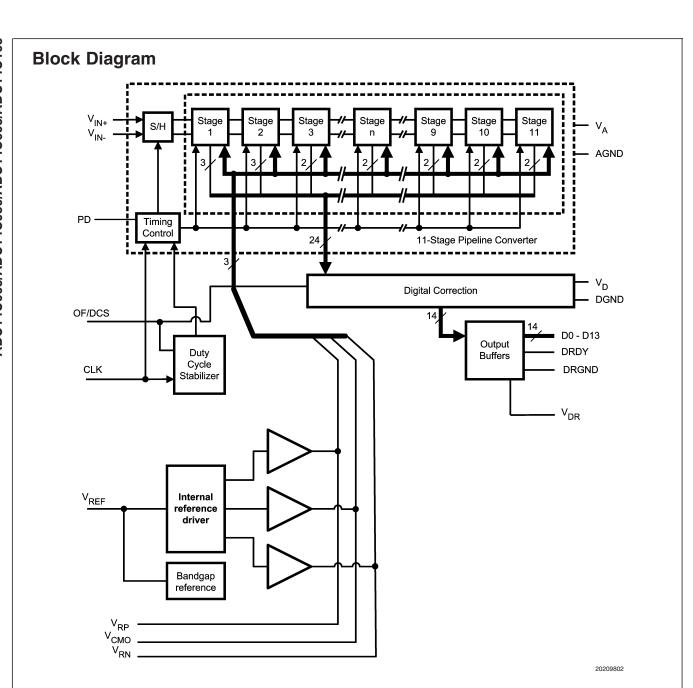

The ADC14C065, ADC14C080, ADC14C095, and ADC14105 are high-performance CMOS analog-to-digital converters capable of converting analog input signals into 14-bit digital words at rates up to 65/80/95/105 Mega Samples Per Second (MSPS) respectively. These converters use a differential, pipelined architecture with digital error correction and an on-chip sample-and-hold circuit to minimize power consumption and the external component count, while providing excellent dynamic performance. A unique sample-and-hold stage yields a full-power bandwidth of 1 GHz. The ADC14C065/080/095/105 may be operated from a single +3.3V power supply and consumes low power.

A separate +2.5V supply may be used for the digital output interface which allows lower power operation with reduced noise. A power-down feature reduces the power consumption to very low levels while still allowing fast wake-up time to full operation. The differential inputs provide a 2V full scale differential input swing. A stable 1.2V internal voltage reference is provided, or the ADC14C065/080/095/105 can be operated with an external 1.2V reference. Output data format (offset binary versus 2's complement) and duty cycle stabilizer are pin-selectable. The duty cycle stabilizer maintains performance over a wide range of clock duty cycles.

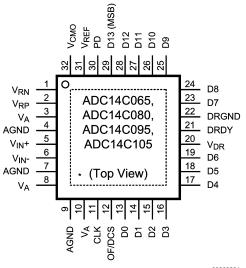

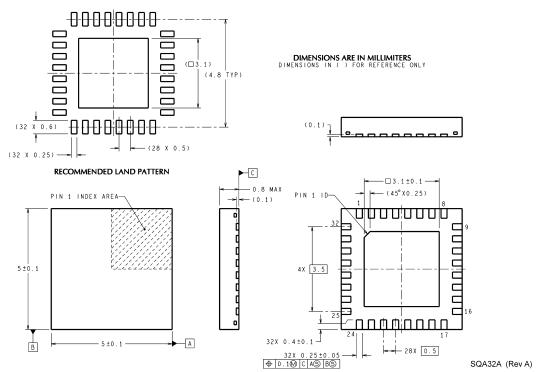

The ADC14C065/080/095/105 is available in a 32-lead LLP package and operates over the industrial temperature range of  $-40^{\circ}$ C to  $+85^{\circ}$ C.

#### **Features**

- 1 GHz Full Power Bandwidth

- Internal sample-and-hold circuit

- Low power consumption

- Internal precision reference

- Data Ready output clock

- Clock Duty Cycle Stabilizer

- Single +3.3V supply operation

- Power-down mode

- Offset binary or 2's complement output data format

- 32-pin LLP package, (5x5x0.8mm, 0.5mm pin-pitch)

## **Key Specifications**

- For ADC14C105

- Resolution■ Conversion Rate14 Bits■ Conversion Rate105 MSPS

- SNR (f<sub>IN</sub> = 240 MHz) 72 dBFS (typ)

- SFDR (f<sub>IN</sub> = 240 MHz) 83 dBFS (typ)

- Full Power Bandwidth 1 GHz (typ)

- Power Consumption 400 mW (typ)

## **Applications**

- High IF Sampling Receivers

- Wireless Base Station Receivers

- Test and Measurement Equipment

- Communications Instrumentation

- Portable Instrumentation

## **Connection Diagram**

# **Ordering Information**

| Industrial ( $-40^{\circ}$ C $\leq$ T <sub>A</sub> $\leq$ +85 $^{\circ}$ C) | Package    |

|-----------------------------------------------------------------------------|------------|

| ADC14C065CISQ                                                               | 32 Pin LLP |

| ADC14C080CISQ                                                               | 32 Pin LLP |

| ADC14C095CISQ                                                               | 32 Pin LLP |

| ADC14C105CISQ                                                               | 32 Pin LLP |

| Pin No.    | Symbol              | Equivalent Circuit                      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|------------|---------------------|-----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ANALOG I/O |                     | =quivalent en out                       | 2000.1911011                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 5          | V <sub>IN</sub> +   | V <sub>A</sub>                          | Differential analog input pins. The differential full-scale input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 6          | 6 V <sub>IN</sub> - |                                         | signal level is $2V_{P-P}$ with each input pin signal centered on a common mode voltage, $V_{\text{CM}}$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 2          | $V_RP$              | v <sup>^</sup> A v <sup>^</sup> A       | These pins should each be bypassed to AGND with a low ES (equivalent series inductance) 1 µF capacitor placed very clost to the pin to minimize stray inductance. A 0.1 µF capacitor                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 32         | $V_{CMO}$           | *************************************** | should be placed between $V_{RP}$ and $V_{RN}$ as close to the pins possible, and a 1 $\mu$ F capacitor should be placed in parallel. $V_{RP}$ and $V_{RN}$ should not be loaded. $V_{CMO}$ may be loaded to                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 1          | $V_{RN}$            | AGND AGND                               | 1mA for use as a temperature stable 1.5V reference. It is recommended to use $V_{CMO}$ to provide the common mode voltage, $V_{CM}$ , for the differential analog inputs, $V_{IN}$ + and $V_{IN}$ -                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 31         | $V_{REF}$           | V <sub>A</sub> O  AGND                  | Reference Voltage. This device provides an internally developed 1.2V reference. When using the internal reference $V_{REF}$ should be decoupled to AGND with a 0.1 $\mu$ F and a 1 $\mu$ F low equivalent series inductance (ESL) capacitor . This pin may be driven with an external 1.2V reference voltage. This pin should not be used to source or sink current.                                                                                                                                                                                                                                                                       |

| IGITAL I/O |                     |                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 11         | CLK                 | V <sub>A</sub> AGND                     | The clock input pin. The analog input is sampled on the rising edge of the clock input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 12         | OF/DCS              | VA<br>AGND                              | This is a four-state pin controlling the input clock mode and output data format. $ \label{eq:controlling}  \mbox{OF/DCS} = V_A, \mbox{ output data format is 2's complement without duty cycle stabilization applied to the input clock  \mbox{OF/DCS} = \mbox{AGND}, \mbox{ output data format is offset binary, without duty cycle stabilization applied to the input clock. } \mbox{OF/DCS} = (2/3)^*V_A, \mbox{ output data is 2's complement with duty cycle stabilization applied to the input clock } \mbox{OF/DCS} = (1/3)^*V_A, \mbox{ output data is offset binary with duty cycle stabilization applied to the input clock.} $ |

| 30         | PD                  | AGNU                                    | This is a two-state input controlling Power Down.  PD = V <sub>A</sub> , Power Down is enabled and power dissipation is reduced.  PD = AGND, Normal operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

#### Pin Descriptions and Equivalent Circuits (Continued) Pin No. **Symbol Equivalent Circuit** Description Digital data output pins that make up the 14-bit conversion 13-19, D0-D13 result. D0 (pin 13) is the LSB, while D13 (pin 29) is the MSB of 23-29 the output word. Output levels are CMOS compatible. Data Ready Strobe. The data output transition is synchronized 21 DRDY with the falling edge of this signal. This signal switches at the same frequency as the CLK input. **ANALOG POWER** Positive analog supply pins. These pins should be connected 3, 8, 10, $V_A$ to a quiet voltage source and be bypassed to AGND with 0.1 μF capacitors located close to the power pins. 4, 7, 9, Exposed **AGND** The ground return for the analog supply. Pad **DIGITAL POWER** Positive driver supply pin for the output drivers. This pin should 20 $V_{DR}$ be connected to a quiet voltage source and be bypassed to DRGND with a 0.1 µF capacitor located close to the power pin. The ground return for the digital output driver supply. This pins 22 **DRGND** should be connected to the system digital ground, but not be connected in close proximity to the ADC's AGND pins.

### Absolute Maximum Ratings (Notes 1,

3)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

Supply Voltage (V<sub>A</sub>, V<sub>DR</sub>) -0.3V to 4.2V Voltage on Any Pin -0.3V to  $(V_A + 0.3V)$ (Not to exceed 4.2V) Input Current at Any Pin other ±5 mA than Supply Pins (Note 4) Package Input Current (Note ±50 mA

4) Max Junction Temp (T<sub>.1</sub>)

Thermal Resistance (0,1A) **ESD** Rating

Human Body Model (Note 6)

Machine Model (Note 6) Storage Temperature

Soldering process must comply with National Semiconductor's Reflow Temperature Profile specifications. Refer to www.national.com/packaging.

(Note 7)

### Operating Ratings (Notes 1, 3)

Supply Voltage (V<sub>A</sub>) (ADC14C065, ADC14C080) +2.7V to +3.6V (ADC14C095,ADC14C105) +3.0V to +3.6V +2.25V to  $V_A$ Output Driver Supply (V<sub>DR</sub>)

$-40^{\circ}C \le T_A \le +85^{\circ}C$

Clock Duty Cycle

Operating Temperature

(DCS Enabled) 30/70 % (DCS disabled) 45/55 % 1.4V to 1.6V  $V_{CM}$ **IAGND-DRGNDI** ≤100mV

#### ADC14C065 Converter Electrical Characteristics

This product is currently under development. As such, the parameters specified are DESIGN TARGETS. The specifications cannot be guaranteed until device characterization has taken place.

+150°C

30°C/W

2500V

250V

-65°C to +150°C

Unless otherwise specified, the following specifications apply: AGND = DRGND = 0V,  $V_A = +3.0V$ ,  $V_{DR} = +2.5V$ , Internal  $V_{REF} = +2.5V$ ,  $V_{DR} = +2.5V$ = +1.2V,  $f_{CLK}$  = 65 MHz,  $V_{CM}$  =  $V_{CMO}$ ,  $C_L$  = 5 pF/pin. Typical values are for  $T_A$  = 25°C. **Boldface limits apply for T\_{MIN} \le T\_A \le T\_{MAX}.** All other limits apply for  $T_A$  = 25°C (Notes 8, 9)

| Symbol                           | Parameter                                      | Conditions                 | Typical    | Limits    | Units    |            |  |  |  |

|----------------------------------|------------------------------------------------|----------------------------|------------|-----------|----------|------------|--|--|--|

| Syllibol                         | Faranietei                                     |                            | (Note 10)  | LIIIIII   | (Limits) |            |  |  |  |

| STATIC CONVERTER CHARACTERISTICS |                                                |                            |            |           |          |            |  |  |  |

|                                  | Resolution with No Missing Codes               |                            |            |           | 14       | Bits (min) |  |  |  |

| INL                              | Integral Non Linearity (Note 11)               |                            |            | ±1.5      |          | LSB (max)  |  |  |  |

| IINL                             | integral Non Lineality (Note 11)               |                            |            | ±1.5      |          | LSB (min)  |  |  |  |

| DNL                              | IL Differential Non Linearity ±0.5             | 105                        |            | LSB (max) |          |            |  |  |  |

| DINL                             | Differential Non Linearity                     |                            |            | ±0.5      |          | LSB (min)  |  |  |  |

|                                  | Under Range Output Code                        |                            |            | 0         | 0        |            |  |  |  |

|                                  | Over Range Output Code                         |                            |            | 16383     | 16383    |            |  |  |  |

| REFERE                           | NCE AND ANALOG INPUT CHARACT                   | TERISTICS                  |            | •         |          |            |  |  |  |

| \/                               | Common Mode Output Voltage                     |                            |            | 1.5       | 1.45     | V (min)    |  |  |  |

| V <sub>CMO</sub>                 | Common Mode Odiput Voltage                     |                            |            | 1.5       | 1.55     | V (max)    |  |  |  |

| V <sub>CM</sub>                  | Analog Input Common Mode                       |                            |            | 1.5       | 1.4      | V (min)    |  |  |  |

| V CM                             | Voltage                                        |                            |            | 1.5       | 1.6      | V (max)    |  |  |  |

| C <sub>IN</sub>                  | V <sub>IN</sub> Input Capacitance (each pin to | $V_{IN} = 1.5 \text{ Vdc}$ | (CLK LOW)  | 8.5       |          | pF         |  |  |  |

| OIN                              | GND) (Note 12)                                 | ± 0.5 V                    | (CLK HIGH) | 3.5       |          | pF         |  |  |  |

| \/                               | External Reference Voltage                     |                            |            | 1.20      | 1.176    | V (min)    |  |  |  |

| V <sub>REF</sub>                 | External Neterence Voltage                     |                            |            | 1.20      | 1.224    | V (max)    |  |  |  |

|                                  |                                                |                            |            |           |          |            |  |  |  |

## **ADC14C065 Dynamic Converter Electrical Characteristics**

Unless otherwise specified, the following specifications apply: AGND = DRGND = 0V,  $V_A$  = +3.0V,  $V_{DR}$  = +2.5V, Internal  $V_{REF}$  = +1.2V,  $f_{CLK}$  = 65 MHz,  $V_{CM}$  =  $V_{CMO}$ ,  $C_L$  = 5 pF/pin, . Typical values are for  $T_A$  = 25°C. **Boldface limits apply for T\_{MIN} \le T\_{A}**  $\le T_{MAX}$ . All other limits apply for  $T_A$  = 25°C (Note 8) (Note 9)

| Symbol  | Parameter                                                   | Conditions                  | Typical<br>(Note 10) | Limits | Units<br>(Limits) |  |  |  |

|---------|-------------------------------------------------------------|-----------------------------|----------------------|--------|-------------------|--|--|--|

| DYNAMIC | DYNAMIC CONVERTER CHARACTERISTICS, A <sub>IN</sub> = -1dBFS |                             |                      |        |                   |  |  |  |

| FPBW    | Full Power Bandwidth                                        | -1 dBFS Input, -3 dB Corner | 1.0                  |        | GHz               |  |  |  |

|         |                                                             | f <sub>IN</sub> = 10 MHz    | 74.3                 |        | dBFS              |  |  |  |

| SNR     | Signal-to-Noise Ratio                                       | f <sub>IN</sub> = 70 MHz    | 72                   |        | dBFS              |  |  |  |

|         |                                                             | f <sub>IN</sub> = 170 MHz   | 72                   |        | dBFS              |  |  |  |

|         |                                                             | f <sub>IN</sub> = 10 MHz    | 90                   |        | dBFS              |  |  |  |

| SFDR    | Spurious Free Dynamic Range                                 | f <sub>IN</sub> = 70 MHz    | 88                   |        | dBFS              |  |  |  |

|         |                                                             | f <sub>IN</sub> = 170 MHz   | 83                   |        | dBFS              |  |  |  |

|         | Effective Number of Bits                                    | f <sub>IN</sub> = 10 MHz    | 12                   |        | Bits              |  |  |  |

| ENOB    |                                                             | f <sub>IN</sub> = 70 MHz    | 11.6                 |        | Bits              |  |  |  |

|         |                                                             | f <sub>IN</sub> = 170 MHz   | 11.6                 |        | Bits              |  |  |  |

|         | Total Harmonic Disortion                                    | f <sub>IN</sub> = 10 MHz    | -88                  |        | dBFS              |  |  |  |

| THD     |                                                             | f <sub>IN</sub> = 70 MHz    | -85                  |        | dBFS              |  |  |  |

|         |                                                             | f <sub>IN</sub> = 170 MHz   | -80                  |        | dBFS              |  |  |  |

|         |                                                             | f <sub>IN</sub> = 10 MHz    | -100                 |        | dBFS              |  |  |  |

| H2      | Second Harmonic Distortion                                  | f <sub>IN</sub> = 70 MHz    | -95                  |        | dBFS              |  |  |  |

|         |                                                             | f <sub>IN</sub> = 170 MHz   | -85                  |        | dBFS              |  |  |  |

|         |                                                             | f <sub>IN</sub> = 10 MHz    | -90                  |        | dBFS              |  |  |  |

| НЗ      | Third Harmonic Distortion                                   | f <sub>IN</sub> = 70 MHz    | -88                  |        | dBFS              |  |  |  |

|         |                                                             | f <sub>IN</sub> = 170 MHz   | -83                  |        | dBFS              |  |  |  |

|         | Cianal to Naine and Distortion                              | f <sub>IN</sub> = 10 MHz    | 74.1                 |        | dBFS              |  |  |  |

| SINAD   | Signal-to-Noise and Distortion Ratio                        | f <sub>IN</sub> = 70 MHz    | 71.8                 |        | dBFS              |  |  |  |

|         | Παιιο                                                       | f <sub>IN</sub> = 170 MHz   | 71.4                 |        | dBFS              |  |  |  |

## **ADC14C065 Logic and Power Supply Electrical Characteristics**

Unless otherwise specified, the following specifications apply: AGND = DRGND = 0V,  $V_A$  = +3.0V,  $V_{DR}$  = +2.5V, Internal  $V_{REF}$  = +1.2V,  $f_{CLK}$  = 65 MHz,  $V_{CM}$  =  $V_{CMO}$ ,  $C_L$  = 5 pF/pin. Typical values are for  $T_A$  = 25°C. **Boldface limits apply for T\_{MIN} \le T\_A \le T\_{MAX}.** All other limits apply for  $T_A$  = 25°C (Notes 8, 9)

| Symbol             | Parameter                              | Conditions                                            | Typical<br>(Note 10) | Limits | Units<br>(Limits) |

|--------------------|----------------------------------------|-------------------------------------------------------|----------------------|--------|-------------------|

| DIGITAL            | INPUT CHARACTERISTICS (CLK, F          | PD)                                                   |                      |        |                   |

| V <sub>IN(1)</sub> | Logical "1" Input Voltage              | V <sub>D</sub> = 3.6V                                 |                      | 2.0    | V (min)           |

| V <sub>IN(0)</sub> | Logical "0" Input Voltage              | V <sub>D</sub> = 3.0V                                 |                      | 0.8    | V (max)           |

| I <sub>IN(1)</sub> | Logical "1" Input Current              | V <sub>IN</sub> = 3.3V                                | 10                   |        | μA                |

| I <sub>IN(0)</sub> | Logical "0" Input Current              | V <sub>IN</sub> = 0V                                  | -10                  |        | μA                |

| C <sub>IN</sub>    | Digital Input Capacitance              |                                                       | 5                    |        | pF                |

| DIGITAL            | <b>OUTPUT CHARACTERISTICS (D0-</b>     | D13, DRDY)                                            |                      |        |                   |

| $V_{OUT(1)}$       | Logical "1" Output Voltage             | $I_{OUT} = -0.5 \text{ mA}$ , $V_{DR} = 1.8 \text{V}$ |                      | 1.2    | V (min)           |

| $V_{OUT(0)}$       | Logical "0" Output Voltage             | I <sub>OUT</sub> = 1.6 mA, V <sub>DR</sub> = 1.8V     |                      | 0.4    | V (max)           |

| +I <sub>SC</sub>   | Output Short Circuit Source<br>Current | V <sub>OUT</sub> = 0V                                 | -10                  |        | mA                |

| -I <sub>sc</sub>   | Output Short Circuit Sink Current      | $V_{OUT} = V_{DR}$                                    | 10                   |        | mA                |

| C <sub>OUT</sub>   | Digital Output Capacitance             |                                                       | 5                    |        | pF                |

| POWER              | SUPPLY CHARACTERISTICS                 |                                                       |                      |        |                   |

| I <sub>A</sub>     | Analog Supply Current                  | Full Operation                                        | 90                   |        | mA (max)          |

| I <sub>DR</sub>    | Digital Output Supply Current          | Full Operation (Note 13)                              | 11.5                 |        | mA                |

## ADC14C065 Logic and Power Supply Electrical Characteristics (Continued)

Unless otherwise specified, the following specifications apply: AGND = DRGND = 0V,  $V_A$  = +3.0V,  $V_{DR}$  = +2.5V, Internal  $V_{REF}$  = +1.2V,  $f_{CLK}$  = 65 MHz,  $V_{CM}$  =  $V_{CMO}$ ,  $C_L$  = 5 pF/pin. Typical values are for  $T_A$  = 25°C. **Boldface limits apply for T\_{MIN} \le T\_A \le T\_{MAX}.** All other limits apply for  $T_A$  = 25°C (Notes 8, 9)

| Symbol | Parameter                    | Conditions                         | Typical<br>(Note 10) | Limits | Units<br>(Limits) |

|--------|------------------------------|------------------------------------|----------------------|--------|-------------------|

|        | Power Consumption            | Excludes I <sub>DR</sub> (Note 13) | 270                  |        | mW (max)          |

|        | Power Down Power Consumption | Clock disabled                     | 5                    |        | mW                |

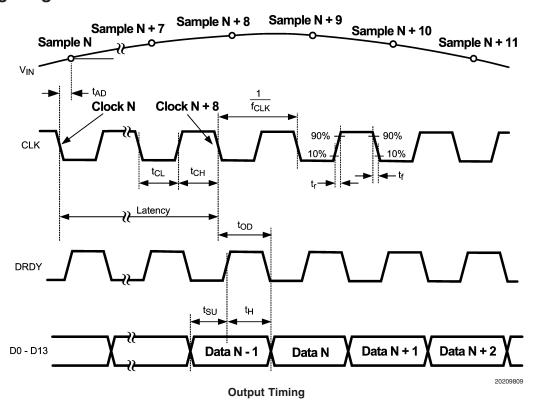

## **ADC14C065 Timing and AC Characteristics**

Unless otherwise specified, the following specifications apply: AGND = DRGND = 0V,  $V_A$  = +3.0V,  $V_{DR}$  = +2.5V, Internal  $V_{REF}$  = +1.2V,  $f_{CLK}$  = 65 MHz,  $V_{CM}$  =  $V_{CMO}$ ,  $C_L$  = 5 pF/pin. Typical values are for  $T_A$  = 25°C. Timing measurements are taken at 50% of the signal amplitude. **Boldface limits apply for T\_{MIN} \le T\_A \le T\_{MAX}.** All other limits apply for  $T_A$  = 25°C (Notes 8, 9)

| Symb              | Parameter                   | Conditions                     | Typical<br>(Note 10) | Limits | Units<br>(Limits)   |

|-------------------|-----------------------------|--------------------------------|----------------------|--------|---------------------|

|                   | Maximum Clock Frequency     |                                |                      | 65     | MHz (max)           |

|                   | Minimum Clock Frequency     |                                |                      | 20     | MHz (min)           |

| t <sub>CH</sub>   | Clock High Time             |                                | 7                    |        | ns                  |

| t <sub>CL</sub>   | Clock Low Time              |                                | 7                    |        | ns                  |

| t <sub>CONV</sub> | Conversion Latency          |                                |                      | 7      | Clock<br>Cycles     |

| t <sub>OD</sub>   | Output Delay of CLK to DATA | Relative to rising edge of CLK | 4                    | 2<br>6 | ns (min)<br>ns(max) |

| t <sub>SU</sub>   | Data Output Setup Time      | Relative to DRDY               | 6                    |        | ns (min)            |

| t <sub>H</sub>    | Data Output Hold Time       | Relative to DRDY               | 6                    |        | ns (min)            |

| t <sub>AD</sub>   | Aperture Delay              |                                | 0.6                  |        | ns                  |

| t <sub>AJ</sub>   | Aperture Jitter             |                                | 0.1                  |        | ps rms              |

### **ADC14C080 Converter Electrical Characteristics**

This product is currently under development. As such, the parameters specified are DESIGN TARGETS. The specifications cannot be guaranteed until device characterization has taken place.

Unless otherwise specified, the following specifications apply: AGND = DRGND = 0V,  $V_A = +3.0V$ ,  $V_{DR} = +2.5V$ , Internal  $V_{REF} = +1.2V$ ,  $f_{CLK} = 80$  MHz,  $V_{CM} = V_{CMO}$ ,  $C_L = 5$  pF/pin. Typical values are for  $T_A = 25^{\circ}C$ . Boldface limits apply for  $T_{MIN} \le T_A \le T_{MAX}$ . All other limits apply for  $T_A = 25^{\circ}C$  (Notes 8, 9)

| Symbol                           | Parameter                                   | Conditions                |            | Typical<br>(Note 10) | Limits         | Units<br>(Limits)      |  |  |

|----------------------------------|---------------------------------------------|---------------------------|------------|----------------------|----------------|------------------------|--|--|

| STATIC CONVERTER CHARACTERISTICS |                                             |                           |            |                      |                |                        |  |  |

|                                  | Resolution with No Missing Codes            |                           |            |                      | 14             | Bits (min)             |  |  |

| INL                              | Integral Non Linearity (Note 11)            |                           |            | ±1.5                 |                | LSB (max)<br>LSB (min) |  |  |

| DNL                              | Differential Non Linearity                  |                           |            | ±0.5                 |                | LSB (max)<br>LSB (min) |  |  |

|                                  | Under Range Output Code                     |                           |            | 0                    | 0              |                        |  |  |

|                                  | Over Range Output Code                      |                           |            | 16383                | 16383          |                        |  |  |

| REFERE                           | NCE AND ANALOG INPUT CHARAC                 | TERISTICS                 |            |                      |                |                        |  |  |

| V <sub>CMO</sub>                 | Common Mode Output Voltage                  |                           |            | 1.5                  | 1.45<br>1.55   | V (min)<br>V (max)     |  |  |

| V <sub>CM</sub>                  | Analog Input Common Mode<br>Voltage         |                           |            | 1.5                  | 1.4<br>1.6     | V (min)<br>V (max)     |  |  |

| C                                | V <sub>IN</sub> Input Capacitance (each pin | V <sub>IN</sub> = 1.5 Vdc | (CLK LOW)  | 8.5                  |                | pF                     |  |  |

| C <sub>IN</sub>                  | to GND) (Note 12)                           | ± 0.5 V                   | (CLK HIGH) | 3.5                  |                | pF                     |  |  |

| $V_{REF}$                        | External Reference Voltage                  |                           |            | 1.20                 | 1.176<br>1.224 | V (min)<br>V (max)     |  |  |

## **ADC14C080 Dynamic Converter Electrical Characteristics**

Unless otherwise specified, the following specifications apply: AGND = DRGND = 0V,  $V_A$  = +3.0V,  $V_{DR}$  = +2.5V, Internal  $V_{REF}$  = +1.2V,  $f_{CLK}$  = 80 MHz,  $V_{CM}$  =  $V_{CMO}$ ,  $C_L$  = 5 pF/pin, . Typical values are for  $T_A$  = 25°C. **Boldface limits apply for T\_{MIN} \le T\_A**  $\le T_{MAX}$ . All other limits apply for  $T_A$  = 25°C (Note 8) (Note 9)

| Symbol  | Parameter                                                   | Conditions                  | Typical<br>(Note 10) | Limits | Units<br>(Limits) |  |  |  |

|---------|-------------------------------------------------------------|-----------------------------|----------------------|--------|-------------------|--|--|--|

| DYNAMIC | DYNAMIC CONVERTER CHARACTERISTICS, A <sub>IN</sub> = -1dBFS |                             |                      |        |                   |  |  |  |

| FPBW    | Full Power Bandwidth                                        | -1 dBFS Input, -3 dB Corner | 1.0                  |        | GHz               |  |  |  |

|         |                                                             | f <sub>IN</sub> = 10 MHz    | 74.2                 |        | dBFS              |  |  |  |

| SNR     | Signal-to-Noise Ratio                                       | f <sub>IN</sub> = 70 MHz    | 72                   |        | dBFS              |  |  |  |

|         |                                                             | f <sub>IN</sub> = 170 MHz   | 72                   |        | dBFS              |  |  |  |

|         |                                                             | f <sub>IN</sub> = 10 MHz    | 90                   |        | dBFS              |  |  |  |

| SFDR    | Spurious Free Dynamic Range                                 | f <sub>IN</sub> = 70 MHz    | 88                   |        | dBFS              |  |  |  |

|         |                                                             | f <sub>IN</sub> = 170 MHz   | 83                   |        | dBFS              |  |  |  |

|         |                                                             | f <sub>IN</sub> = 10 MHz    | 12                   |        | Bits              |  |  |  |

| ENOB    | Effective Number of Bits                                    | f <sub>IN</sub> = 70 MHz    | 11.6                 |        | Bits              |  |  |  |

|         |                                                             | f <sub>IN</sub> = 170 MHz   | 11.6                 |        | Bits              |  |  |  |

|         |                                                             | f <sub>IN</sub> = 10 MHz    | -90                  |        | dBFS              |  |  |  |

| THD     | Total Harmonic Disortion                                    | f <sub>IN</sub> = 70 MHz    | -85                  |        | dBFS              |  |  |  |

|         |                                                             | f <sub>IN</sub> = 170 MHz   | -80                  |        | dBFS              |  |  |  |

|         |                                                             | f <sub>IN</sub> = 10 MHz    | -100                 |        | dBFS              |  |  |  |

| H2      | Second Harmonic Distortion                                  | f <sub>IN</sub> = 70 MHz    | -95                  |        | dBFS              |  |  |  |

|         |                                                             | f <sub>IN</sub> = 170 MHz   | -85                  |        | dBFS              |  |  |  |

|         |                                                             | f <sub>IN</sub> = 10 MHz    | -90                  |        | dBFS              |  |  |  |

| H3      | Third Harmonic Distortion                                   | f <sub>IN</sub> = 70 MHz    | -88                  |        | dBFS              |  |  |  |

|         |                                                             | f <sub>IN</sub> = 170 MHz   | -83                  |        | dBFS              |  |  |  |

## **ADC14C080 Dynamic Converter Electrical Characteristics** (Continued)

Unless otherwise specified, the following specifications apply: AGND = DRGND = 0V,  $V_A$  = +3.0V,  $V_{DR}$  = +2.5V, Internal  $V_{REF}$  = +1.2V,  $f_{CLK}$  = 80 MHz,  $V_{CM}$  =  $V_{CMO}$ ,  $C_L$  = 5 pF/pin, . Typical values are for  $T_A$  = 25°C. **Boldface limits apply for T\_{MIN} \le T\_A**  $\le T_{MAX}$ . All other limits apply for  $T_A$  = 25°C (Note 8) (Note 9)

| Symbol                         | Parameter                      | Conditions                | Typical<br>(Note 10) | Limits | Units<br>(Limits) |

|--------------------------------|--------------------------------|---------------------------|----------------------|--------|-------------------|

| SINAD Signal-to-Noise<br>Ratio | Oissand to Naissand Distantian | f <sub>IN</sub> = 10 MHz  | 74                   |        | dBFS              |

|                                | Signal-to-Noise and Distortion | f <sub>IN</sub> = 70 MHz  | 71.8                 |        | dBFS              |

|                                | Hatio                          | f <sub>IN</sub> = 170 MHz | 71.4                 |        | dBFS              |

## **ADC14C080 Logic and Power Supply Electrical Characteristics**

Unless otherwise specified, the following specifications apply: AGND = DRGND = 0V,  $V_A = +3.0V$ ,  $V_{DR} = +2.5V$ , Internal  $V_{REF} = +1.2V$ ,  $f_{CLK} = 80$  MHz,  $V_{CM} = V_{CMO}$ ,  $C_L = 5$  pF/pin. Typical values are for  $T_A = 25^{\circ}C$ . Boldface limits apply for  $T_{MIN} \le T_A \le T_{MAX}$ . All other limits apply for  $T_A = 25^{\circ}C$  (Notes 8, 9)

| Symbol              | Parameter                              | Conditions                                            | Typical<br>(Note 10) | Limits | Units<br>(Limits) |

|---------------------|----------------------------------------|-------------------------------------------------------|----------------------|--------|-------------------|

| DIGITAL             | INPUT CHARACTERISTICS (CLK, F          | (ספ                                                   |                      |        |                   |

| V <sub>IN(1)</sub>  | Logical "1" Input Voltage              | V <sub>D</sub> = 3.6V                                 |                      | 2.0    | V (min)           |

| V <sub>IN(0)</sub>  | Logical "0" Input Voltage              | V <sub>D</sub> = 3.0V                                 |                      | 0.8    | V (max)           |

| I <sub>IN(1)</sub>  | Logical "1" Input Current              | $V_{IN} = 3.3V$                                       | 10                   |        | μA                |

| I <sub>IN(0)</sub>  | Logical "0" Input Current              | $V_{IN} = 0V$                                         | -10                  |        | μA                |

| C <sub>IN</sub>     | Digital Input Capacitance              |                                                       | 5                    |        | pF                |

| DIGITAL             | OUTPUT CHARACTERISTICS (D0-            | D13, DRDY)                                            | •                    |        |                   |

| V <sub>OUT(1)</sub> | Logical "1" Output Voltage             | $I_{OUT} = -0.5 \text{ mA}$ , $V_{DR} = 1.8 \text{V}$ |                      | 1.2    | V (min)           |

| V <sub>OUT(0)</sub> | Logical "0" Output Voltage             | $I_{OUT} = 1.6 \text{ mA}, V_{DR} = 1.8 \text{V}$     |                      | 0.4    | V (max)           |

| +l <sub>SC</sub>    | Output Short Circuit Source<br>Current | V <sub>OUT</sub> = 0V                                 | -10                  |        | mA                |

| -I <sub>sc</sub>    | Output Short Circuit Sink Current      | $V_{OUT} = V_{DR}$                                    | 10                   |        | mA                |

| C <sub>OUT</sub>    | Digital Output Capacitance             |                                                       | 5                    |        | pF                |

| POWER               | SUPPLY CHARACTERISTICS                 |                                                       |                      |        |                   |

| I <sub>A</sub>      | Analog Supply Current                  | Full Operation                                        | 100                  |        | mA (max)          |

| I <sub>DR</sub>     | Digital Output Supply Current          | Full Operation (Note 13)                              | 13                   |        | mA                |

|                     | Power Consumption                      | Excludes I <sub>DR</sub> (Note 13)                    | 300                  |        | mW (max)          |

|                     | Power Down Power Consumption           | Clock disabled                                        | 5                    |        | mW                |

## **ADC14C080 Timing and AC Characteristics**

Unless otherwise specified, the following specifications apply: AGND = DRGND = 0V,  $V_A$  = +3.0V,  $V_{DR}$  = +2.5V, Internal  $V_{REF}$  = +1.2V,  $f_{CLK}$  = 80 MHz,  $V_{CM}$  =  $V_{CMO}$ ,  $C_L$  = 5 pF/pin. Typical values are for  $T_A$  = 25°C. Timing measurements are taken at 50% of the signal amplitude. **Boldface limits apply for T\_{MIN} \le T\_A \le T\_{MAX}.** All other limits apply for  $T_A$  = 25°C (Notes 8, 9)

| Symb              | Parameter                   | Conditions                     | Typical<br>(Note 10) | Limits | Units<br>(Limits)   |

|-------------------|-----------------------------|--------------------------------|----------------------|--------|---------------------|

|                   | Maximum Clock Frequency     |                                |                      | 80     | MHz (max)           |

|                   | Minimum Clock Frequency     |                                |                      | 20     | MHz (min)           |

| t <sub>CH</sub>   | Clock High Time             |                                | 6                    |        | ns                  |

| t <sub>CL</sub>   | Clock Low Time              |                                | 6                    |        | ns                  |

| t <sub>CONV</sub> | Conversion Latency          |                                |                      | 7      | Clock<br>Cycles     |

| t <sub>OD</sub>   | Output Delay of CLK to DATA | Relative to rising edge of CLK | 4                    | 2<br>6 | ns (min)<br>ns(max) |

| t <sub>su</sub>   | Data Output Setup Time      | Relative to DRDY               | 5                    |        | ns (min)            |

| t <sub>H</sub>    | Data Output Hold Time       | Relative to DRDY               | 5                    |        | ns (min)            |

| t <sub>AD</sub>   | Aperture Delay              |                                | 0.6                  |        | ns                  |

| t <sub>AJ</sub>   | Aperture Jitter             |                                | 0.1                  |        | ps rms              |

### **ADC14C095 Converter Electrical Characteristics**

This product is currently under development. As such, the parameters specified are DESIGN TARGETS. The specifications cannot be guaranteed until device characterization has taken place.

Unless otherwise specified, the following specifications apply: AGND = DRGND = 0V,  $V_A$  = +3.3V,  $V_{DR}$  = +2.5V, Internal  $V_{REF}$  = +1.2V,  $f_{CLK}$  = 95 MHz,  $V_{CM}$  =  $V_{CMO}$ ,  $C_L$  = 5 pF/pin. Typical values are for  $T_A$  = 25°C. **Boldface limits apply for T\_{MIN} \le T\_A \le T\_{MAX}.** All other limits apply for  $T_A$  = 25°C (Notes 8, 9)

| Symbol           | Parameter                                      | Conditions                |            | Typical<br>(Note 10) | Limits | Units<br>(Limits) |

|------------------|------------------------------------------------|---------------------------|------------|----------------------|--------|-------------------|

| STATIC (         | CONVERTER CHARACTERISTICS                      |                           |            |                      |        |                   |

|                  | Resolution with No Missing Codes               |                           |            |                      | 14     | Bits (min)        |

| INL              | Integral New Linearity (Nets 11)               |                           |            | +15                  |        | LSB (max)         |

| IINL             | Integral Non Linearity (Note 11)               |                           |            | ±1.5                 |        | LSB (min)         |

| DNL              | D''' '' IN I' ''                               |                           |            | ±0.5                 |        | LSB (max)         |

| DINL             | Differential Non Linearity                     |                           |            | ±0.5                 |        | LSB (min)         |

|                  | Under Range Output Code                        |                           |            | 0                    | 0      |                   |

|                  | Over Range Output Code                         |                           |            | 16383                | 16383  |                   |

| REFERE           | NCE AND ANALOG INPUT CHARACT                   | TERISTICS                 |            | •                    |        |                   |

|                  | Common Mode Output Voltage                     |                           |            | 1.5                  | 1.45   | V (min)           |

| $V_{CMO}$        | Common Mode Output Voltage                     |                           |            | 1.5                  | 1.55   | V (max)           |

| V <sub>CM</sub>  | Analog Input Common Mode                       |                           |            | 1.5                  | 1.4    | V (min)           |

| V CM             | Voltage                                        |                           |            | 1.5                  | 1.6    | V (max)           |

|                  | V <sub>IN</sub> Input Capacitance (each pin to | V <sub>IN</sub> = 1.5 Vdc | (CLK LOW)  | 8.5                  |        | pF                |

| C <sub>IN</sub>  | GND) (Note 12)                                 | ± 0.5 V                   | (CLK HIGH) | 3.5                  |        | pF                |

|                  | External Reference Voltage                     |                           |            | 1.20                 | 1.176  | V (min)           |

| V <sub>REF</sub> | External neference voltage                     |                           |            | 1.20                 | 1.224  | V (max)           |

### ADC14C095 Dynamic Converter Electrical Characteristics

Unless otherwise specified, the following specifications apply: AGND = DRGND = 0V,  $V_A$  = +3.3V,  $V_{DR}$  = +2.5V, Internal  $V_{REF}$  = +1.2V,  $f_{CLK}$  = 95 MHz,  $V_{CM}$  =  $V_{CMO}$ ,  $C_L$  = 5 pF/pin, . Typical values are for  $T_A$  = 25°C. **Boldface limits apply for T\_{MIN} \le T\_A**  $\le T_{MAX}$ . All other limits apply for  $T_A$  = 25°C (Note 8) (Note 9)

| Symbol  | Parameter                    | Conditions                  | Typical   | Limits | Units    |

|---------|------------------------------|-----------------------------|-----------|--------|----------|

|         |                              |                             | (Note 10) |        | (Limits) |

| DYNAMIC | C CONVERTER CHARACTERISTICS, | A <sub>IN</sub> = -1dBFS    |           |        |          |

| FPBW    | Full Power Bandwidth         | -1 dBFS Input, -3 dB Corner | 1.0       |        | GHz      |

|         |                              | f <sub>IN</sub> = 10 MHz    | 73.7      |        | dBFS     |

| SNR     | Signal-to-Noise Ratio        | f <sub>IN</sub> = 70 MHz    | 72        |        | dBFS     |

|         |                              | f <sub>IN</sub> = 240 MHz   | 72        |        | dBFS     |

|         |                              | f <sub>IN</sub> = 10 MHz    | 90        |        | dBFS     |

| SFDR    | Spurious Free Dynamic Range  | f <sub>IN</sub> = 70 MHz    | 88        |        | dBFS     |

|         |                              | f <sub>IN</sub> = 240 MHz   | 83        |        | dBFS     |

|         | Effective Number of Bits     | f <sub>IN</sub> = 10 MHz    | 11.9      |        | Bits     |

| ENOB    |                              | f <sub>IN</sub> = 70 MHz    | 11.6      |        | Bits     |

|         |                              | f <sub>IN</sub> = 240 MHz   | 11.6      |        | Bits     |

|         |                              | f <sub>IN</sub> = 10 MHz    | -88       |        | dBFS     |

| THD     | Total Harmonic Disortion     | f <sub>IN</sub> = 70 MHz    | -85       |        | dBFS     |

|         |                              | f <sub>IN</sub> = 240 MHz   | -80       |        | dBFS     |

|         |                              | f <sub>IN</sub> = 10 MHz    | -95       |        | dBFS     |

| H2      | Second Harmonic Distortion   | f <sub>IN</sub> = 70 MHz    | -90       |        | dBFS     |

|         |                              | f <sub>IN</sub> = 240 MHz   | -85       |        | dBFS     |

|         |                              | f <sub>IN</sub> = 10 MHz    | -90       |        | dBFS     |

| НЗ      | Third Harmonic Distortion    | f <sub>IN</sub> = 70 MHz    | -88       |        | dBFS     |

|         |                              | f <sub>IN</sub> = 240 MHz   | -83       |        | dBFS     |

## **ADC14C095 Dynamic Converter Electrical Characteristics** (Continued)

Unless otherwise specified, the following specifications apply: AGND = DRGND = 0V,  $V_A$  = +3.3V,  $V_{DR}$  = +2.5V, Internal  $V_{REF}$  = +1.2V,  $f_{CLK}$  = 95 MHz,  $V_{CM}$  =  $V_{CMO}$ ,  $C_L$  = 5 pF/pin, . Typical values are for  $T_A$  = 25°C. Boldface limits apply for  $T_{MIN} \le T_A$   $\le T_{MAX}$ . All other limits apply for  $T_A$  = 25°C (Note 8) (Note 9)

| Symbol                                     | Parameter                      | Conditions                | Typical<br>(Note 10) | Limits | Units<br>(Limits) |

|--------------------------------------------|--------------------------------|---------------------------|----------------------|--------|-------------------|

| SINAD Signal-to-Noise and Distortion Ratio | Circulate Naise and Distortion | f <sub>IN</sub> = 10 MHz  | 73.5                 |        | dBFS              |

|                                            | f <sub>IN</sub> = 70 MHz       | 71.7                      |                      | dBFS   |                   |

|                                            | nauo                           | f <sub>IN</sub> = 240 MHz | 71.6                 |        | dBFS              |

## **ADC14C095 Logic and Power Supply Electrical Characteristics**

Unless otherwise specified, the following specifications apply: AGND = DRGND = 0V,  $V_A = +3.3V$ ,  $V_{DR} = +2.5V$ , Internal  $V_{REF} = +1.2V$ ,  $f_{CLK} = 95$  MHz,  $V_{CM} = V_{CMO}$ ,  $C_L = 5$  pF/pin. Typical values are for  $T_A = 25^{\circ}C$ . **Boldface limits apply for T\_{MIN} \le T\_A \le T\_{MAX}.** All other limits apply for  $T_A = 25^{\circ}C$  (Notes 8, 9)

| Symbol              | Parameter                                     | Conditions                                            | Typical<br>(Note 10) | Limits | Units<br>(Limits) |  |  |  |

|---------------------|-----------------------------------------------|-------------------------------------------------------|----------------------|--------|-------------------|--|--|--|

| DIGITAL             | INPUT CHARACTERISTICS (CLK, P                 | D)                                                    |                      |        |                   |  |  |  |

| V <sub>IN(1)</sub>  | Logical "1" Input Voltage                     | V <sub>D</sub> = 3.6V                                 |                      | 2.0    | V (min)           |  |  |  |

| V <sub>IN(0)</sub>  | Logical "0" Input Voltage                     | V <sub>D</sub> = 3.0V                                 |                      | 0.8    | V (max)           |  |  |  |

| I <sub>IN(1)</sub>  | Logical "1" Input Current                     | $V_{IN} = 3.3V$                                       | 10                   |        | μΑ                |  |  |  |

| I <sub>IN(0)</sub>  | Logical "0" Input Current                     | $V_{IN} = 0V$                                         | -10                  |        | μΑ                |  |  |  |

| C <sub>IN</sub>     | Digital Input Capacitance                     |                                                       | 5                    |        | pF                |  |  |  |

| DIGITAL             | DIGITAL OUTPUT CHARACTERISTICS (D0-D13, DRDY) |                                                       |                      |        |                   |  |  |  |

| V <sub>OUT(1)</sub> | Logical "1" Output Voltage                    | $I_{OUT} = -0.5 \text{ mA}$ , $V_{DR} = 1.8 \text{V}$ |                      | 1.2    | V (min)           |  |  |  |

| V <sub>OUT(0)</sub> | Logical "0" Output Voltage                    | $I_{OUT} = 1.6 \text{ mA}, V_{DR} = 1.8 \text{V}$     |                      | 0.4    | V (max)           |  |  |  |

| +l <sub>sc</sub>    | Output Short Circuit Source<br>Current        | V <sub>OUT</sub> = 0V                                 | -10                  |        | mA                |  |  |  |

| -I <sub>SC</sub>    | Output Short Circuit Sink Current             | $V_{OUT} = V_{DR}$                                    | 10                   |        | mA                |  |  |  |

| C <sub>OUT</sub>    | Digital Output Capacitance                    |                                                       | 5                    |        | pF                |  |  |  |

| POWER               | SUPPLY CHARACTERISTICS                        |                                                       |                      |        | _                 |  |  |  |

| I <sub>A</sub>      | Analog Supply Current                         | Full Operation                                        | 115                  |        | mA (max)          |  |  |  |

| I <sub>DR</sub>     | Digital Output Supply Current                 | Full Operation (Note 13)                              | 14.5                 |        | mA                |  |  |  |

|                     | Power Consumption                             | Excludes I <sub>DR</sub> (Note 13)                    | 380                  |        | mW (max)          |  |  |  |

|                     | Power Down Power Consumption                  | Clock disabled                                        | 5                    |        | mW                |  |  |  |

## **ADC14C095 Timing and AC Characteristics**

Unless otherwise specified, the following specifications apply: AGND = DRGND = 0V,  $V_A$  = +3.3V,  $V_{DR}$  = +2.5V, Internal  $V_{REF}$  = +1.2V,  $f_{CLK}$  = 95 MHz,  $V_{CM}$  =  $V_{CMO}$ ,  $C_L$  = 5 pF/pin. Typical values are for  $T_A$  = 25°C. Timing measurements are taken at 50% of the signal amplitude. **Boldface limits apply for T\_{MIN} \le T\_A \le T\_{MAX}.** All other limits apply for  $T_A$  = 25°C (Notes 8, 9)

| Symb              | Parameter                   | Conditions                     | Typical<br>(Note 10) | Limits | Units<br>(Limits)    |

|-------------------|-----------------------------|--------------------------------|----------------------|--------|----------------------|

|                   | Maximum Clock Frequency     |                                |                      | 95     | MHz (max)            |

|                   | Minimum Clock Frequency     |                                |                      | 20     | MHz (min)            |

| t <sub>CH</sub>   | Clock High Time             |                                | 5                    |        | ns                   |

| t <sub>CL</sub>   | Clock Low Time              |                                | 5                    |        | ns                   |

| t <sub>CONV</sub> | Conversion Latency          |                                |                      | 7      | Clock<br>Cycles      |

| t <sub>OD</sub>   | Output Delay of CLK to DATA | Relative to rising edge of CLK | 4                    | 2<br>6 | ns (min)<br>ns (max) |

| t <sub>SU</sub>   | Data Output Setup Time      | Relative to DRDY               | 4                    |        | ns (min)             |

| t <sub>H</sub>    | Data Output Hold Time       | Relative to DRDY               | 4                    |        | ns (min)             |

| t <sub>AD</sub>   | Aperture Delay              |                                | 0.6                  |        | ns                   |

| t <sub>AJ</sub>   | Aperture Jitter             |                                | 0.1                  |        | ps rms               |

### **ADC14C105 Converter Electrical Characteristics**

This product is currently under development. As such, the parameters specified are DESIGN TARGETS. The specifications cannot be guaranteed until device characterization has taken place.

Unless otherwise specified, the following specifications apply: AGND = DRGND = 0V,  $V_A$  = +3.3V,  $V_{DR}$  = +2.5V, Internal  $V_{REF}$  = +1.2V,  $f_{CLK}$  = 105 MHz,  $V_{CM}$  =  $V_{CMO}$ ,  $C_L$  = 5 pF/pin. Typical values are for  $T_A$  = 25°C. **Boldface limits apply for T\_{MIN} \le T\_A \le T\_{MAX}.** All other limits apply for  $T_A$  = 25°C (Notes 8, 9)

| Symbol           | Parameter                                      | Con                        | ditions    | Typical   | Limits | Units      |

|------------------|------------------------------------------------|----------------------------|------------|-----------|--------|------------|

| STATIC (         | ONVERTER CHARACTERISTICS                       |                            |            | (Note 10) |        | (Limits)   |

| - CIANO C        | Resolution with No Missing Codes               |                            |            |           | 14     | Bits (min) |

|                  |                                                |                            |            |           |        | LSB (max)  |

| INL              | Integral Non Linearity (Note 11)               |                            |            | ±1.5      |        | LSB (min)  |

| DNL              | Differential Non Linearity                     |                            |            | ±0.5      |        | LSB (max)  |

| DINL             | Differential Non Linearity                     |                            |            | ±0.5      |        | LSB (min)  |

|                  | Under Range Output Code                        |                            |            | 0         | 0      |            |

|                  | Over Range Output Code                         |                            |            | 16383     | 16383  |            |

| REFERE           | NCE AND ANALOG INPUT CHARACT                   | TERISTICS                  |            |           |        |            |

| $V_{CMO}$        | Common Mode Output Voltage                     |                            |            | 1.5       | 1.45   | V (min)    |

| * CMO            | Common wode Calput Voltage                     |                            |            | 1.5       | 1.55   | V (max)    |

| $V_{CM}$         | Analog Input Common Mode                       |                            |            | 1.5       | 1.4    | V (min)    |

| V CM             | Voltage                                        |                            |            | 1.5       | 1.6    | V (max)    |

|                  | V <sub>IN</sub> Input Capacitance (each pin to | $V_{IN} = 1.5 \text{ Vdc}$ | (CLK LOW)  | 8.5       |        | pF         |

| C <sub>IN</sub>  | GND) (Note 12)                                 | ± 0.5 V                    | (CLK HIGH) | 3.5       |        | pF         |

| V <sub>REF</sub> | External Reference Voltage                     |                            |            | 1.20      | 1.176  | V (min)    |

| ▼ REF            | External Helerence Voltage                     |                            |            | 1.20      | 1.224  | V (max)    |

### ADC14C105 Dynamic Converter Electrical Characteristics

Unless otherwise specified, the following specifications apply: AGND = DRGND = 0V,  $V_A$  = +3.3V,  $V_{DR}$  = +2.5V, Internal  $V_{REF}$  = +1.2V,  $f_{CLK}$  = 105 MHz,  $V_{CM}$  =  $V_{CMO}$ ,  $C_L$  = 5 pF/pin, . Typical values are for  $T_A$  = 25°C. **Boldface limits apply for T\_{MIN} \le T\_A**  $\le T_{MAX}$ . All other limits apply for  $T_A$  = 25°C (Note 8) (Note 9)

| Symbol  | Parameter                    | Conditions                  | Typical   | Limits | Units    |

|---------|------------------------------|-----------------------------|-----------|--------|----------|

|         |                              |                             | (Note 10) |        | (Limits) |

| DYNAMIC | C CONVERTER CHARACTERISTICS, | A <sub>IN</sub> = -1dBFS    |           |        |          |

| FPBW    | Full Power Bandwidth         | -1 dBFS Input, -3 dB Corner | 1.0       |        | GHz      |

|         |                              | f <sub>IN</sub> = 10 MHz    | 73        |        | dBFS     |

| SNR     | Signal-to-Noise Ratio        | f <sub>IN</sub> = 70 MHz    | 72.5      |        | dBFS     |

|         |                              | f <sub>IN</sub> = 240 MHz   | 72        |        | dBFS     |

|         |                              | f <sub>IN</sub> = 10 MHz    | 88        |        | dBFS     |

| SFDR    | Spurious Free Dynamic Range  | f <sub>IN</sub> = 70 MHz    | 85        |        | dBFS     |

|         |                              | f <sub>IN</sub> = 240 MHz   | 83        |        | dBFS     |

|         | Effective Number of Bits     | f <sub>IN</sub> = 10 MHz    | 11.8      |        | Bits     |

| ENOB    |                              | f <sub>IN</sub> = 70 MHz    | 11.7      |        | Bits     |

|         |                              | f <sub>IN</sub> = 240 MHz   | 11.6      |        | Bits     |

|         |                              | f <sub>IN</sub> = 10 MHz    | -86       |        | dBFS     |

| THD     | Total Harmonic Disortion     | f <sub>IN</sub> = 70 MHz    | -85       |        | dBFS     |

|         |                              | f <sub>IN</sub> = 240 MHz   | -80       |        | dBFS     |

|         |                              | f <sub>IN</sub> = 10 MHz    | -95       |        | dBFS     |

| H2      | Second Harmonic Distortion   | f <sub>IN</sub> = 70 MHz    | -90       |        | dBFS     |

|         |                              | f <sub>IN</sub> = 240 MHz   | -85       |        | dBFS     |

|         |                              | f <sub>IN</sub> = 10 MHz    | -88       |        | dBFS     |

| H3      | Third Harmonic Distortion    | f <sub>IN</sub> = 70 MHz    | -85       |        | dBFS     |

|         |                              | f <sub>IN</sub> = 240 MHz   | -83       |        | dBFS     |

## ADC14C105 Dynamic Converter Electrical Characteristics (Continued)

Unless otherwise specified, the following specifications apply: AGND = DRGND = 0V,  $V_A$  = +3.3V,  $V_{DR}$  = +2.5V, Internal  $V_{REF}$  = +1.2V,  $f_{CLK}$  = 105 MHz,  $V_{CM}$  =  $V_{CMO}$ ,  $C_L$  = 5 pF/pin, . Typical values are for  $T_A$  = 25°C. **Boldface limits apply for T\_{MIN} \le T\_A**  $\le T_{MAX}$ . All other limits apply for  $T_A$  = 25°C (Note 8) (Note 9)

| Symbol                               | Parameter                     | Conditions                | Typical<br>(Note 10) | Limits | Units<br>(Limits) |

|--------------------------------------|-------------------------------|---------------------------|----------------------|--------|-------------------|

| SINAD Signal-to-Noise and Distortion | Circulto Naise and Distantian | f <sub>IN</sub> = 10 MHz  | 72.8                 |        | dBFS              |

|                                      | f <sub>IN</sub> = 70 MHz      | 72.3                      |                      | dBFS   |                   |

|                                      | Ratio                         | f <sub>IN</sub> = 240 MHz | 71.4                 |        | dBFS              |

## **ADC14C105 Logic and Power Supply Electrical Characteristics**

Unless otherwise specified, the following specifications apply: AGND = DRGND = 0V,  $V_A$  = +3.3V,  $V_{DR}$  = +2.5V, Internal  $V_{REF}$  = +1.2V,  $f_{CLK}$  = 105 MHz,  $V_{CM}$  =  $V_{CMO}$ ,  $C_L$  = 5 pF/pin. Typical values are for  $T_A$  = 25°C. **Boldface limits apply for T\_{MIN} \le T\_A**  $\le T_{MAX}$ . All other limits apply for  $T_A$  = 25°C (Notes 8, 9)

| Symbol              | Parameter                              | Conditions                                            | Typical<br>(Note 10) | Limits | Units<br>(Limits) |

|---------------------|----------------------------------------|-------------------------------------------------------|----------------------|--------|-------------------|

| DIGITAL             | INPUT CHARACTERISTICS (CLK, F          | (D)                                                   |                      |        |                   |

| V <sub>IN(1)</sub>  | Logical "1" Input Voltage              | V <sub>D</sub> = 3.6V                                 |                      | 2.0    | V (min)           |

| V <sub>IN(0)</sub>  | Logical "0" Input Voltage              | $V_{\rm D} = 3.0 \rm{V}$                              |                      | 0.8    | V (max)           |

| I <sub>IN(1)</sub>  | Logical "1" Input Current              | V <sub>IN</sub> = 3.3V                                | 10                   |        | μA                |

| I <sub>IN(0)</sub>  | Logical "0" Input Current              | V <sub>IN</sub> = 0V                                  | -10                  |        | μA                |

| C <sub>IN</sub>     | Digital Input Capacitance              |                                                       | 5                    |        | pF                |

| DIGITAL             | <b>OUTPUT CHARACTERISTICS (D0-</b>     | D13, DRDY)                                            | •                    |        |                   |

| V <sub>OUT(1)</sub> | Logical "1" Output Voltage             | $I_{OUT} = -0.5 \text{ mA}$ , $V_{DR} = 1.8 \text{V}$ |                      | 1.2    | V (min)           |

| V <sub>OUT(0)</sub> | Logical "0" Output Voltage             | $I_{OUT} = 1.6 \text{ mA}, V_{DR} = 1.8 \text{V}$     |                      | 0.4    | V (max)           |

| +l <sub>SC</sub>    | Output Short Circuit Source<br>Current | V <sub>OUT</sub> = 0V                                 | -10                  |        | mA                |

| -I <sub>sc</sub>    | Output Short Circuit Sink Current      | $V_{OUT} = V_{DR}$                                    | 10                   |        | mA                |

| C <sub>OUT</sub>    | Digital Output Capacitance             |                                                       | 5                    |        | pF                |

| POWER               | SUPPLY CHARACTERISTICS                 |                                                       |                      |        |                   |

| I <sub>A</sub>      | Analog Supply Current                  | Full Operation                                        | 121                  |        | mA (max)          |

| I <sub>DR</sub>     | Digital Output Supply Current          | Full Operation (Note 13)                              | 16                   |        | mA                |

|                     | Power Consumption                      | Excludes I <sub>DR</sub> (Note 13)                    | 400                  |        | mW (max)          |

|                     | Power Down Power Consumption           | Clock disabled                                        | 5                    |        | mW                |

## **ADC14C105 Timing and AC Characteristics**

Unless otherwise specified, the following specifications apply: AGND = DRGND = 0V,  $V_A$  = +3.3V,  $V_{DR}$  = +2.5V, Internal  $V_{REF}$  = +1.2V,  $f_{CLK}$  = 105 MHz,  $V_{CM}$  =  $V_{CMO}$ ,  $C_L$  = 5 pF/pin. Typical values are for  $T_A$  = 25°C. Timing measurements are taken at 50% of the signal amplitude. **Boldface limits apply for T\_{MIN} \le T\_A \le T\_{MAX}.** All other limits apply for  $T_A$  = 25°C (Notes 8, 9)

| Symb              | Parameter                   | Conditions                     | Typical<br>(Note 10) | Limits | Units<br>(Limits)    |

|-------------------|-----------------------------|--------------------------------|----------------------|--------|----------------------|

|                   | Maximum Clock Frequency     |                                |                      | 105    | MHz (max)            |

|                   | Minimum Clock Frequency     |                                |                      | 20     | MHz (min)            |

| t <sub>CH</sub>   | Clock High Time             |                                | 4                    |        | ns                   |

| t <sub>CL</sub>   | Clock Low Time              |                                | 4                    |        | ns                   |

| t <sub>CONV</sub> | Conversion Latency          |                                |                      | 7      | Clock<br>Cycles      |

| t <sub>OD</sub>   | Output Delay of CLK to DATA | Relative to rising edge of CLK | 4                    | 2<br>6 | ns (min)<br>ns (max) |

| t <sub>su</sub>   | Data Output Setup Time      | Relative to DRDY               | 3                    |        | ns (min)             |

| t <sub>H</sub>    | Data Output Hold Time       | Relative to DRDY               | 3                    |        | ns (min)             |

| t <sub>AD</sub>   | Aperture Delay              |                                | 0.6                  |        | ns                   |

| t <sub>AJ</sub>   | Aperture Jitter             |                                | 0.1                  |        | ps rms               |

### ADC14C105 Timing and AC Characteristics (Continued)

**Note 1:** Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is guaranteed to be functional, but do not guarantee specific performance limits. For guaranteed specifications and test conditions, see the Electrical Characteristics. The guaranteed specifications apply only for the test conditions listed. Some performance characteristics may degrade when the device is not operated under the listed test conditions. Operation of the device beyond the maximum Operating Ratings is not recommended.

Note 2: Parameters specified in dBFS indicate the value that would be attained with a full-scale input signal.

Note 3: All voltages are measured with respect to GND = AGND = DRGND = 0V, unless otherwise specified.

**Note 4:** When the input voltage at any pin exceeds the power supplies (that is,  $V_{IN} \le AGND$ , or  $V_{IN} \ge V_A$ ), the current at that pin should be limited to  $\pm 5$  mA. The  $\pm 50$  mA maximum package input current rating limits the number of pins that can safely exceed the power supplies with an input current of  $\pm 5$  mA to 10.

Note 5: The maximum allowable power dissipation is dictated by  $T_{J,max}$ , the junction-to-ambient thermal resistance,  $(\theta_{JA})$ , and the ambient temperature,  $(T_A)$ , and can be calculated using the formula  $P_{D,max} = (T_{J,max} - T_A)/\theta_{JA}$ . The values for maximum power dissipation listed above will be reached only when the device is operated in a severe fault condition (e.g. when input or output pins are driven beyond the power supply voltages, or the power supply polarity is reversed). Such conditions should always be avoided.

Note 6: Human Body Model is 100 pF discharged through a 1.5 k $\Omega$  resistor. Machine Model is 220 pF discharged through 0  $\Omega$

Note 7: Reflow temperature profiles are different for lead-free and non-lead-free packages.

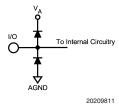

Note 8: The inputs are protected as shown below. Input voltage magnitudes above V<sub>A</sub> or below GND will not damage this device, provided current is limited per (Note 4). However, errors in the A/D conversion can occur if the input goes above 2.6V or below GND as described in the Operating Ratings section.

Note 9: With a full scale differential input of  $2V_{\text{P-P}}$  , the 14-bit LSB is 122.1  $\mu V\!.$

Note 10: Typical figures are at  $T_A = 25^{\circ}C$  and represent most likely parametric norms at the time of product characterization. The typical specifications are not quaranteed.

Note 11: Integral Non Linearity is defined as the deviation of the analog value, expressed in LSBs, from the straight line that passes through positive and negative full-scale

Note 12: The input capacitance is the sum of the package/pin capacitance and the sample and hold circuit capacitance.

Note 13:  $I_{DR}$  is the current consumed by the switching of the output drivers and is primarily determined by load capacitance on the output pins, the supply voltage,  $V_{DR}$ , and the rate at which the outputs are switching (which is signal dependent).  $I_{DR}=V_{DR}(C_0 x f_0 + C_1 x f_1 + ... C_{11} x f_{11})$  where  $V_{DR}$  is the output driver power supply voltage,  $C_n$  is total capacitance on the output pin, and  $f_n$  is the average frequency at which that pin is toggling.

### **Specification Definitions**

**APERTURE DELAY** is the time after the falling edge of the clock to when the input signal is acquired or held for conversion.

**APERTURE JITTER (APERTURE UNCERTAINTY)** is the variation in aperture delay from sample to sample. Aperture jitter manifests itself as noise in the output.

**CLOCK DUTY CYCLE** is the ratio of the time during one cycle that a repetitive digital waveform is high to the total time of one period. The specification here refers to the ADC clock input signal.

**COMMON MODE VOLTAGE (V<sub>CM</sub>)** is the common DC voltage applied to both input terminals of the ADC.

**CONVERSION LATENCY** is the number of clock cycles between initiation of conversion and when that data is presented to the output driver stage. Data for any given sample is available at the output pins the Pipeline Delay plus the Output Delay after the sample is taken. New data is available at every clock cycle, but the data lags the conversion by the pipeline delay.

**DIFFERENTIAL NON-LINEARITY (DNL)** is the measure of the maximum deviation from the ideal step size of 1 LSB.

**EFFECTIVE NUMBER OF BITS (ENOB, or EFFECTIVE BITS)** is another method of specifying Signal-to-Noise and Distortion Ratio or SINAD. ENOB is defined as (SINAD - 1.76) / 6.02 and says that the converter is equivalent to a perfect ADC of this (ENOB) number of bits.

**FULL POWER BANDWIDTH** is a measure of the frequency at which the reconstructed output fundamental drops 3 dB below its low frequency value for a full scale input.

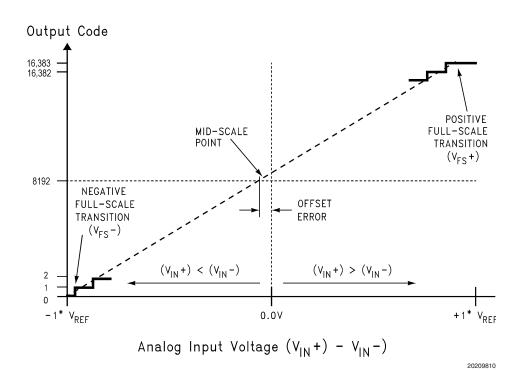

**GAIN ERROR** is the deviation from the ideal slope of the transfer function. It can be calculated as:

Gain Error = Positive Full Scale Error - Negative Full Scale Error

It can also be expressed as Positive Gain Error and Negative Gain Error, which are calculated as:

PGE = Positive Full Scale Error - Offset Error NGE = Offset Error - Negative Full Scale Error