Complete 12-Bit A/D converters with reference

Pin-to-pin compatible with industry standard

No missing codes over temperature

250 mW maximum power dissipation

## **PRODUCT OVERVIEW**

The ADC-674 A/D converters are available in both ceramic leadless chip carrier and industry standard DIP packages.

These units include a reference, clock, threestate outputs, and digital interface circuit which allows direct connection to the microprocessor address bus and control lines. The ADC-674 completes a 12-bit conversion in 8 microseconds.

Four user selectable input ranges are provided: 0 to +10V, 0 to +20V, +/-5V, and +/-10V dc. Laser trimming ensures specified linearity, gain and offset accuracy.

|     | INPUT/OUTPUT CONNECTIONS                  |     |                  |  |  |  |  |

|-----|-------------------------------------------|-----|------------------|--|--|--|--|

| PIN | FUNCTION                                  | PIN | FUNCTION         |  |  |  |  |

| 1   | V <sub>logic</sub> , +5V                  | 15  | D <sub>GND</sub> |  |  |  |  |

| 2   | 12/8, DATA MODE SELECT                    | 16  | DB0 (LSB)        |  |  |  |  |

| 3   | CS, CHIP SELECT                           | 17  | DB1              |  |  |  |  |

| 4   | A <sub>0</sub> , BYTE ADDRESS/SHORT CYCLE | 18  | DB2              |  |  |  |  |

| 5   | r/c, read/convert                         | 19  | DB3              |  |  |  |  |

| 6   | CE, CHIP ENABLE                           | 20  | DB4              |  |  |  |  |

| 7   | V <sub>cc</sub>                           | 21  | DB5              |  |  |  |  |

| 8   | REFERENCE OUT                             | 22  | DB6              |  |  |  |  |

| 9   | AGND                                      | 23  | DB7              |  |  |  |  |

| 10  | REFERENCE IN                              | 23  | DB8              |  |  |  |  |

| 11  | V <sub>ee</sub> *                         | 25  | DB9              |  |  |  |  |

| 12  | BIPOLAR OFFSET                            | 26  | DB10             |  |  |  |  |

| 13  | 10V IN                                    | 27  | DB11 (MSB)       |  |  |  |  |

| 14  | 20V IN                                    | 28  | STS              |  |  |  |  |

#### \* For applications with no -15V supply, contact our factory.

#### Vec Vis Auto (7) (1) (9) CON **28)**515 BIPOLAR (12) 27) DB11 (MSB) OFFSET 26 DB10 25 DB9 10V IN (13 rt. 24) DBS 20V IN (14 23 DB7 capacitance dac THREE 20066 STATE S.A.R 21) DB5 BUFFERS 20 DB4 19 DB3 18 DB2 17 DB1 (**16)** DBO (LSB) V logic (1 D GND (15 10V CONTROL REF OSCILLATO LOGIC 10 REF IN 8 REF OUT 23456

### Figure 1. ADC-674 Functional Block Diagram

DATEL, Inc. 11 Cabot Boulevard, Mansfield, MA 02048-1151 USA • Tel: (508) 339-3000 • www.datel.com • e-mail: help@datel.com

## **BLOCK DIAGRAM**

and clock

574A/674A Series

8 µSec. Conversion time

| ABSOLUTE MAXIMUM RATINGS                            |                                                    |

|-----------------------------------------------------|----------------------------------------------------|

| V <sub>CC</sub> TO GND                              | 0 to +16.5V                                        |

| V <sub>ee</sub> to GND                              | 0 to -16.5V                                        |

| Logic Supply Voltage (Pin 1)                        | OV to +7V                                          |

| Analog Common (Pin 9) to Digital Common (Pin 15)    | 0.5V to + 1V                                       |

| Digital Control Inputs (Pins 2-6) to Digital Common | -0.3V to V <sub>logic</sub> +0.3V                  |

| Analog Inputs (Pins 10,12,13) to Analog Common      | ±16.5V                                             |

| 20V Input (Pin 14) to Analog Common                 | ±24V                                               |

| Ref. Out (Pin 8) Short Circuit Duration             | Indefinite to common, momentary to V <sub>CC</sub> |

| Chip Temperature                                    | -55°C to 125°C                                     |

| Package Dissipation                                 | 1000 mW                                            |

| Lead Temperature, soldering                         | 300°C, 10 Sec.                                     |

| Thermal Resistance, Junction-to-Ambient             | 48°C/W                                             |

#### **FUNCTIONAL SPECIFICATIONS**

Typical at 25°C,  $\pm$ 15V, and +5V dc supply ranges, unless otherwise noted.

| ANALOG INPUTS                  |                                                                                        |                                      |

|--------------------------------|----------------------------------------------------------------------------------------|--------------------------------------|

| Input Voltage Range            | unipolar                                                                               | 0 to +10V, 0 to +20V                 |

|                                | bipolar                                                                                | ±5V, ±10V                            |

| Input Impedance                | 10V range                                                                              | 5KΩ ±2KΩ                             |

|                                | 20V range                                                                              | 10ΚΩ ±4ΚΩ                            |

| ANALOG OUTPUTS ①               |                                                                                        |                                      |

| Internal Reference             | voltage                                                                                | +10.00V ±0.1 max.                    |

|                                | current                                                                                | 8 mA max.                            |

| DIGITAL INPUTS ②               |                                                                                        |                                      |

| Logic Levels:                  | logic "1"                                                                              | +2.0 min. to +5.5V max.              |

|                                | logic "0"                                                                              | -0.5V min. to +0.8V max.             |

| Loading:                       | $V_{IN} = 0$ to $V_{logic}$                                                            | ±5 μA                                |

| Capacitance                    |                                                                                        | 5pF                                  |

| DIGITAL OUTPUTS ③              |                                                                                        |                                      |

| Logic Levels:                  | logic "0" (I sink, 1.6 mA)                                                             | +0.4V max.                           |

|                                | logic "1" (I source, 500 µA)                                                           | +2.4V min.                           |

| Leakage (high impedance state) |                                                                                        | -10 $\mu$ A min. to +10 $\mu$ A max. |

| Capacitance                    |                                                                                        | 5pF                                  |

| POWER REQUIREMENTS             |                                                                                        |                                      |

| Analog Supply Voltage Range    |                                                                                        | ±11.4V to ±16.5V                     |

| Logic Supply Voltage Range     |                                                                                        | +4.5V to +5.5V                       |

| Supply-Current max.            | V <sub>cc</sub> , V <sub>ee</sub>                                                      | +7mA, -9mA                           |

|                                | Logic Supply                                                                           | +7mA                                 |

| Power Consumption              | $V_{CC} = +15V, V_{ee} = -15V, V_{logic} = +5V$                                        | 250 mW                               |

| PHYSICAL/ENVIRONMENTAL         |                                                                                        |                                      |

| Operating Temperature Range    |                                                                                        | -55°C to +125°C                      |

| Storage Temperature Range      |                                                                                        | -65°C to +150°C                      |

| Package Type                   |                                                                                        | 28 pin LCC ceramic                   |

| PERFORMANCE (TYPICAL)          |                                                                                        |                                      |

| Resolution                     |                                                                                        | 12 Bits                              |

| Conversion Time, max.          |                                                                                        | 8 µSec                               |

| Power Supply Rejection ®       | $V_{CC} = +15V \pm 1.5V$ , $V_{ee} = -15V \pm 1.5V$ , or<br>$V_{logic} = +5V \pm 0.5V$ | ±0.001% FSR / %V                     |

| Differential Linearity Error   | max. ④, no missing codes                                                               | ±1 LSB                               |

| Linearity Error                | max. ④                                                                                 | ±1 LSB                               |

| PERFORMANCE (TYPICAL, CONT.) |                         |       |  |  |  |

|------------------------------|-------------------------|-------|--|--|--|

| Unipolar Offset              | Max. 6                  | ±2LSB |  |  |  |

| Unipolar Offset              | Max. tempco ⑥ ⑦         | ±1LSB |  |  |  |

| Bipolar Offset               | Max. (5) (6)            | ±3LSB |  |  |  |

| Bipolar Offset               | Max. tempco (5) (6) (7) | ±2LSB |  |  |  |

| Full Scale Calibration.      | Max. 6                  | ±5LSB |  |  |  |

| Full Scale Calibration.      | Max. tempco ⑥ ⑦         | ±6LSB |  |  |  |

#### Footnotes:

- ① Available for external loads. External load should not change during conversion. When supplying an external load using a +12V supply, a buffer amplifier must be provided for the reference output.

- 2 Logic Inputs CE, CS, R/C, A, 12/8.

- 3 Logic Outputs DB11-DB0, STS.

- ④ Over temperature.

- **TECHNICAL NOTES**

- The ADC-674 may interface directly to a microprocessor which can take full control of each conversion, or the device can be operated in the "stand alone" mode (controlled only by the R/Cinput). Full control consists of selecting an 8- or 12-bit conversion cycle, initiating the conversion and reading the output data when ready. The data may be read 12 bits at once or 8 followed by 4 in a left-justified format. There are five control inputs (12/8, CS, A<sub>p</sub>, R/C: and CE) and all are TTL/CMOS compatible. (See Control Input Truth Table.)

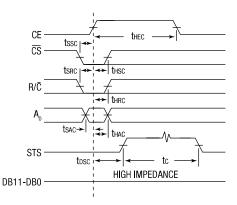

- A conversion is initiated by a logic transition on any of the three inputs: CE, CS, R/C. One, two, or all three may be dynamically controlled. The nominal delay for each of the three inputs is the same and if necessary, all three may change states simultaneously. If it is required that a particular input controls the start of conversion, the other two should be set up at least 50 nanoseconds earlier. (See Start Convert Timing, Figure 3).

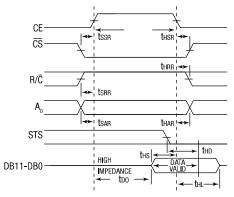

- 3. To read the output data, four conditions must be met (or the output buffers will remain in high impedance state): R/C taken high, STS low, CE high and  $\overline{CS}$  low. When this is accomplished, the data lines are activated according to the state of the 12/8 and  $A_n$  inputs. (See TIMING DIAGRAM on Figure 4).

- 4. The analog signal source driving the ADC-674's input will see a nominal load of 5 K $\Omega$  (10V range) or 10 K $\Omega$  (20V range). However, the other end of

5 With 50  $\Omega$  fixed resistor from REF OUT to BIP OFF. Adjustable to zero.

- $\circledast$  With 50  $\Omega$  fixed resistor from REF OUT to REF IN. Adjustable to zero.

- $\ensuremath{\oslash}$  Guaranteed maximum change, Tmin to Tmax (using internal reference).

- ⑧ Maximum change in full scale calibration.

these input resistors may change 400 mV with each bit decision, causing sudden changes in current at the analog input. Therefore, the signal source must maintain its output voltage while supplying these step changes in load current which occur at 1.6 microsecond intervals. This requires low output impedance and fast settling by the signal source.

- 5. The power supply used should be low noise and well regulated. Voltage spikes can affect accuracy. If a switching supply is used, the outputs should be carefully filtered to assure "noise free" dc voltage to the converter. Decoupling capacitors should be used on all power supply pins; the +5V dc supply decoupling capacitor should be connected directly from + $V_{ogic}$  (Pin 1) to digital common (Pin 15).  $V_{CC}$  (Pin 7) and  $V_{ee}$  (Pin 11) should be decoupled directly to A<sub>GND</sub> (Pin 9). It is recommended that a 10 µF tantalum type in parallel with a 0.1 µF ceramic type be used for decoupling.

- 6. The use of good circuit board layout techniques is required for rated performance. It is recommended that a double sided printed circuit board with a ground plane on the component side be used. Other techniques, such as wirewrapping or point-to-point wiring on vectorboard will have an unpredictable effect on accuracy. Sensitive analog signals should be routed between ground traces and kept away from digital lines. If analog and digital lines must cross, they should do so at right angles.

# **ADC-674** 12-Bit, µP-Compatible A/D Converter

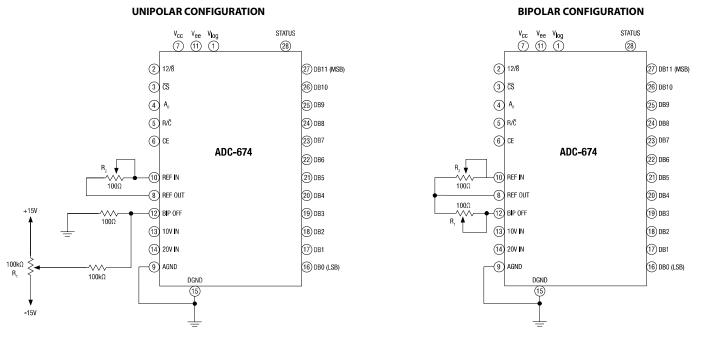

#### **TYPICAL CONNECTIONS**

NOTES: The trimpots shown are for calibration of offset and gain. If adjustment is not required in unipolar, replace R<sub>2</sub> with a 50Ω, 1% metal film resistor, omit the network on Pin 12 and connect Pin 12 to Pin 9. In bipolar, either R or R<sub>2</sub> or both can be replaced by 50Ω, 1% metal film resistors.

#### **CODING TABLES**

| INPUT RANGE |           | OUTPUT CODING |      |       |

|-------------|-----------|---------------|------|-------|

| 0 to + 10V  | 0 to +20V | MSB           |      | LSB   |

| +10.000     | +20.0000  | 1111          | 1111 | 1111  |

| +9.9963     | +19.9927  | 1111          | 1111 | 111Ø* |

| +5.0012     | +10.0024  | 1000          | 0000 | 000Ø* |

| +4.9988     | +9.9976   | Ø000          | 0000 | 000Ø* |

| +4.9963     | +9.9927   | 0111          | 1111 | 111Ø* |

| +0.0012     | +0.0024   | 0000          | 0000 | 000Ø* |

| 0.0000      | +0.0000   | 0000          | 0000 | 0000  |

\* Voltages shown are theoretical values for the transitions indicated. Ideally, In the continuous conversion mode, the output bits indicated as will change from "1" to "0" or "0" to "1" as the input voltage passes through the level indicated.

Output coding is straight binary for unipolar and offset binary for bipolar.

#### CALIBRATION

### **UNIPOLAR CALIBRATION**

#### **Offset Adjust**

Apply an input of +½ LSB (+1.22 mV for the 10V range; +2.44 mV for the 20V range). Adjust the offset trimpot ( $R_1$ ) until the first code transition flickers between 0000 0000 0000 and 0000 0000 0001.

#### **Gain Adjust**

Apply 1½ LSB's below the nominal full-scale (+9.9963V for the 10V range; +19.9927V for the 20V range). Adjust the gain-trimpot ( $R_2$ ) so that the output flickers between 1111 1111 1110 and 1111 1111 1111.

# BIPOLAR CALIBRATION Offset Adjust

Apply ½ LSB above negative full-scale (-4.9988V for the ±5V range; -9.9976V for the ±10V range.) Adjust the offset trimpot ( $R_1$ ) so that the output flickers between 0000 0000 0000 and 0000 0000 0001.

## Gain Adjust

Apply 1½ LSB's below positive full scale (+4.9963V for the  $\pm$ 5V range; +9.9927V for the  $\pm$ 10V range). Adjust the gain trimpot (R) so that the output flickers between 1111 1111 1110 and 1111 1111 1111.

DATEL, Inc. 11 Cabot Boulevard, Mansfield, MA 02048-1151 USA • Tel: (508) 339-3000 • www.datel.com • e-mail: help@datel.com

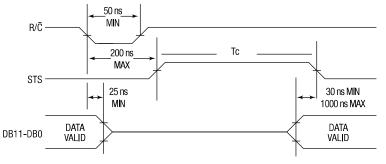

#### TIMING CONTROL

The variety of the ADC-674's control modes (as shown in the "CONTROL INPUTS TRUTH TABLE") allow for simple interface in most system applications.

The output signal STS indicates the status of the device; high during a conversion, and low at the completion of a conversion. During a conversion (STS output high), the output buffers remain in the high impedance state and data cannot be read. A start convert during conversion will not reset the converter or reinitiate a conversion. However, if  $A_b$  changes state after a conversion begins, an additional start convert pulse will latch the new state of  $A_b$  causing a wrong cycle length for that conversion.

| CE  | <u>c</u> | R/Ċ | 12/8 | A <sub>o</sub> | OPERATION                              |

|-----|----------|-----|------|----------------|----------------------------------------|

| 0   | х        | Х   | Х    | Х              | None                                   |

| Х   | 1        | Х   | Х    | Х              | None                                   |

| 0-1 | 0        | 0   | Х    | 0              | Initiate 12-bit conversion             |

| 0-1 | 0        | 0   | Х    | 1              | Initiate 8-bit conversion              |

| 1   | 1-0      | 0   | Х    | 0              | Initiate 12-bit conversion             |

| 1   | 1-0      | 0   | Х    | 1              | Initiate 8-bit conversion              |

| 1   | 0        | 1-0 | Х    | 0              | Initiate 12-bit conversion             |

| 1   | 0        | 1-0 | Х    | 1              | Initiate 8-bit conversion              |

| 1   | 0        | 1   | 1    | Х              | Enable 12-bit Output                   |

| 1   | 0        | 1   | 0    | 0              | Enables 8 MSB's only                   |

| 1   | 0        | 1   | 0    | 1              | Enables 4 LSB's plus 4 trailing zeroes |

# **Control Inputs Truth Table**

### TIMING AND OPERATION

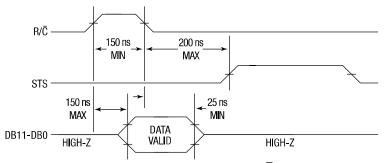

#### **Stand-Alone Mode Timing**

For stand-alone operation, all that is required is a single control line to R/C CE and 12/8 are tied high,  $\overline{CS}$  and  $A_0$  are tied low, and the output appears in words of 12 bits

The R/C signal may have any duty cycle within the limits shown in the diagrams below

The data may be read when R/C is high unless STS is also high indicating a conversion is in progress.

Figure 2. Outputs Enabled With R/CHigh

#### **Figure 3. Start Convert Timing**

A read operation in most applications begins after the conversion is complete and STS is low. For earliest access to the data, however, the read should begin no later than ( $bD + t_{HS}$ ) before STS goes low. (See Technical Note 3.)

DATEL, Inc. 11 Cabot Boulevard, Mansfield, MA 02048-1151 USA • Tel: (508) 339-3000 • www.datel.com • e-mail: help@datel.com

Figure 4. Read Cycle Timing

ADC-674 TIMING

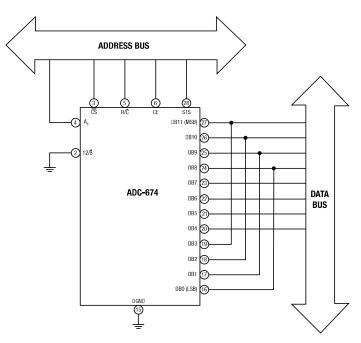

### Interface To An 8-Bit Data Bus

The 12/8 input will be tied either high or low in most applications. With 12/8 high, all 12 output lines become active simultaneously for interface to a 12- or 16-bit data bus.  $A_0$  is ignored. Taking 12/8 low organizes the output in two 8-bit bytes, which are selected one at a time by  $A_0$ . This allows an 8-bit data bus to be connected as shown below.  $A_0$  is normally tied to the LSB of the address bus for storing the converter's output in two consecutive memory locations. This two byte format is called "left justified data" for which a decimal point is assumed to the left of byte 1. In addition,  $A_0$  may be toggled at any time without damage to the converter. Break-before-make switching is guaranteed between two data bytes, which assures that the outputs strapped together as shown are never enabled at the same time.

| Symbol           | Parameter, Read Mode              | Min.  | Тур. | Max.   |

|------------------|-----------------------------------|-------|------|--------|

| t <sub>DD</sub>  | Access Time from CE               | -     | -    | 150 nS |

| thd              | Data Valid after CE low           | 25 nS | -    | -      |

| t <sub>HL</sub>  | Output Float Delay                | -     | -    | 120 nS |

| tSSR             | CS to CE Setup                    | 50 nS | 0    | -      |

| t <sub>SRR</sub> | $R/\overline{C}$ to CE Setup      | 0     | 0    | -      |

| <sup>t</sup> SAR | A <sub>0</sub> to CE Setup        | 50 nS | -    | -      |

| tHSR             | CS Valid after CE Low             | 0     | 0    | 0      |

| t <sub>HRR</sub> | RIC High after CE Low             | 0     | 0    | 0      |

| thar             | A <sub>0</sub> Valid after CE Low | 0 nS  | -    | -      |

| ths              | STS Delay after Data Valid        | 30 nS | -    | 300 nS |

| Symbol         | Parameter, Read Mode                | Min.  | Тур. | Max.   |

|----------------|-------------------------------------|-------|------|--------|

| tDSC           | STS Delay From CE                   | -     | -    | 200 nS |

| thec           | CE Pulse Width                      | 50 nS | -    | -      |

| tSSC           | CS to CE Setup                      | 50 nS | -    | -      |

| thsc           | CS Low during CE High               | 50 nS | -    | -      |

| tSRC           | R/C to CE Setup                     | 50 nS | -    | -      |

| thrc           | R/C Low during CE High              | 50 nS | -    | -      |

| tSAC           | A <sub>0</sub> to CE Setup          | 0     | -    | 0      |

| thac           | A <sub>0</sub> Valid during CD High | 50 nS | -    | -      |

| t <sub>C</sub> | Conversion Time:                    | ~     |      |        |

|                | 12-bit cycle                        | 6 µS  | -    | 8 µS   |

|                | 8-bit cycle                         | 4 µS  | -    | 6 µS   |

Figure 5 8-Bit Data Bus

# **ADC-674** 12-Bit, µP-Compatible A/D Converter

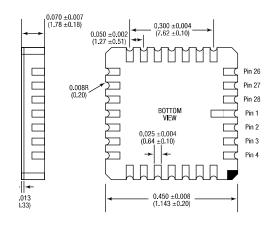

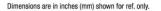

## MECHANICAL DIMENSIONS - INCHES (mm)

#### **CLCC** Package

Tolerances (unless otherwise specified): .XX  $\pm$  0.02 (0.5) .XXX  $\pm$  0.010 (0.25) Angles  $\pm$  2°

Components are shown for reference only.

28-PIN Ceramic DIP Package

| ORDERING INFORMATION |                       |            |      |  |  |  |

|----------------------|-----------------------|------------|------|--|--|--|

| MODEL NUMBER         | OPERATING TEMP. RANGE | PACKAGE    | ROHS |  |  |  |

| ADC-674LC            | 0°C TO 70°C           | 28-Pin LCC | No   |  |  |  |

| ADC-674LC-C          | 0°C TO 70°C           | 28-Pin LCC | Yes  |  |  |  |

| ADC-674LE            | -40°C T0 +100°C       | 28-Pin LCC | No   |  |  |  |

| ADC-674LE-C          | -40°C T0 +100°C       | 28-Pin LCC | Yes  |  |  |  |

| ADC-674LM            | -55°C T0 +125°C       | 28-Pin LCC | No   |  |  |  |

| ADC-674LM-C          | -55°C T0 +125°C       | 28-Pin LCC | Yes  |  |  |  |

| ADC-674L/883         | -55°C T0 +125°C       | 28-Pin LCC | No   |  |  |  |

| ADC-674L/883-C       | -55°C T0 +125°C       | 28-Pin LCC | Yes  |  |  |  |

| ADC-674AMC           | 0°C TO 70°C           | 28-Pin DIP | No   |  |  |  |

| ADC-674AMC-C         | 0°C TO 70°C           | 28-Pin DIP | Yes  |  |  |  |

| ADC-674AME           | -40°C T0 +100°C       | 28-Pin DIP | No   |  |  |  |

| ADC-674AME-C         | -40°C T0 +100°C       | 28-Pin DIP | Yes  |  |  |  |

| ADC-674AMM           | -55°C T0 +125°C       | 28-Pin DIP | No   |  |  |  |

| ADC-674AMM-C         | -55°C T0 +125°C       | 28-Pin DIP | Yes  |  |  |  |

| ADC-674A/883         | -55°C T0 +125°C       | 28-Pin DIP | No   |  |  |  |

| ADC-674A/883-C       | -55°C T0 +125°C       | 28-Pin DIP | Yes  |  |  |  |

DATEL is a registered trademark of DATEL, Inc. 11 Cabot Boulevard, Mansfield, MA 02048-1151 USA ITAR and ISO 9001/14001 REGISTERED DATEL, Inc. makes no representation that the use of its products in the circuits described herein, or the use of other technical information contained herein, will not infringe upon existing or future patent rights. The descriptions contained herein do not imply the granting of licenses to make, use, or sell equipment constructed in accordance therewith. Specifications are subject to change without notice.

© 2016 DATEL, Inc.

www.datel.com • e-mail: help@datel.com