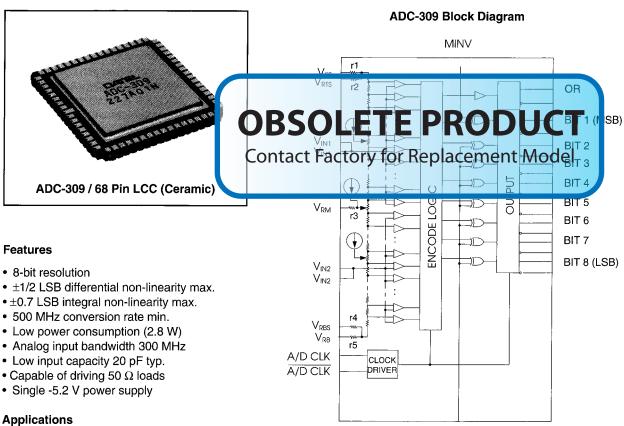

# PRODUCT DATA SHEET

# 8-BIT, 500 MHz FLASH A/D CONVERTER

- Digital oscilloscopes

- · Radar systems

- · Other high-speed data acquisition systems

# **General Description**

The ADC-309 is a monolithic 8-bit ultrahighspeed bipolar silicon flash A/D converter IC capable of digitizing analog signals from -2 V to 0 V at a maximum rate of 500 MSPS. The digital I/O levels of this A/D converter are compatible with the ECL 100 k/10 kH/10 k.

It features a built-in integral linearity compensation circuit, low error rate and excellent temperature characteristics.

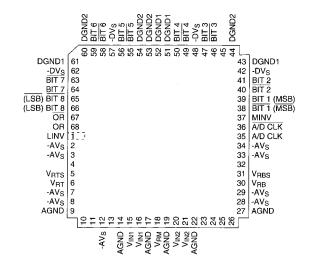

#### ADC-309 Input/Output Connections (Top View)

LINV

Pins without names are NC pins (internally not connected)

#### Description

| Electrical Characteristics:<br>$-AV_{S} = -DV_{S} = -5.2 V_{DC}, V_{RT} = V_{RTS} = 0 V, V_{RB} = V_{RBS} = -2 V_{DC}$ |                                                            |                  |                                                  |                 |                 |  |  |  |  |

|------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|------------------|--------------------------------------------------|-----------------|-----------------|--|--|--|--|

| $-AV_s = -DV_s = -5.2 V_{DC}, V$ Analog Inputs                                                                         | $V_{RB} = V_{RBS} = -2 V_{DC}$   Min.   Typ.   Max.   Unit |                  |                                                  |                 |                 |  |  |  |  |

|                                                                                                                        |                                                            | 141111.          | <del>                                     </del> | IVIAA.          | +               |  |  |  |  |

| Analog Input Voltage Analog Input Capacitance                                                                          | _                                                          | -2 to 0<br>20    | _                                                | V <sub>DC</sub> |                 |  |  |  |  |

| Analog Input Resistance                                                                                                | 30                                                         | 70               | -                                                | pF              |                 |  |  |  |  |

|                                                                                                                        | 30                                                         | ′                | 600                                              | kΩ              |                 |  |  |  |  |

| Input Bias Current (V <sub>IN</sub> =                                                                                  | 200                                                        | -                | 620                                              | μA              |                 |  |  |  |  |

| Full Scale Input Bandwid                                                                                               | 300                                                        | L –              |                                                  | MHz             |                 |  |  |  |  |

| Reference                                                                                                              |                                                            | T                |                                                  | Г               | T :             |  |  |  |  |

| Reference Input Voltage                                                                                                | V <sub>RT</sub>                                            | -0.1             | 0                                                | +0.1            | V <sub>DC</sub> |  |  |  |  |

|                                                                                                                        | $V_{RB}$                                                   | -2.2             | -2                                               | -1.8            | V <sub>DC</sub> |  |  |  |  |

| Reference Resistance *1                                                                                                | $R_{REF}$                                                  | 70               | 110                                              | 160             | Ω               |  |  |  |  |

| Residual Resistance                                                                                                    | r1                                                         | 0.1              | 0.5                                              | 2.0             | Ω               |  |  |  |  |

| (see block diagram)                                                                                                    | r2                                                         | 0.5              | 5.2                                              | 10              | Ω               |  |  |  |  |

|                                                                                                                        | r3                                                         | 0.5              | 1.6                                              | 5.0             | Ω               |  |  |  |  |

|                                                                                                                        | r4                                                         | 0.5              | 8.7                                              | 20              | Ω               |  |  |  |  |

|                                                                                                                        | r5                                                         | 0.1              | 0.5                                              | 2.0             | Ω               |  |  |  |  |

| Digital Inputs                                                                                                         |                                                            |                  |                                                  |                 |                 |  |  |  |  |

| Logic High Level                                                                                                       | V <sub>IH</sub>                                            | -1.10            |                                                  | _               | V <sub>DC</sub> |  |  |  |  |

| Logic Low Level                                                                                                        | $V_{_{\rm IL}}$                                            | _                | -                                                | -1.55           | V <sub>DC</sub> |  |  |  |  |

| Logic High Current                                                                                                     | I <sub>IH</sub>                                            | 0                | –                                                | 70              | μÃ              |  |  |  |  |

| $V_{IH} = -0.8V$                                                                                                       | ***                                                        |                  |                                                  |                 |                 |  |  |  |  |

| Logic Low Current                                                                                                      | l <sub>IL</sub>                                            | -50              | -                                                | 60              | μΑ              |  |  |  |  |

| V <sub>II</sub> = -1.6V                                                                                                | IL.                                                        |                  |                                                  |                 | '               |  |  |  |  |

| Input Capacitance                                                                                                      |                                                            | _                | 6                                                | _               | pF              |  |  |  |  |

| Clock Duty Cycle *2                                                                                                    |                                                            | 45               | 50                                               | 55              | %               |  |  |  |  |

| Digital Outputs (50 $\Omega$ Lo                                                                                        | oad to -2 V <sub>DC</sub> )                                | <u></u>          |                                                  |                 |                 |  |  |  |  |

| Logic High Level                                                                                                       | V <sub>OH</sub>                                            | -1.03            | _                                                | _               | V <sub>DC</sub> |  |  |  |  |

| Logic Low Level                                                                                                        | V <sub>OL</sub>                                            | _                |                                                  | -1.58           | V <sub>DC</sub> |  |  |  |  |

| Output Rise Time *3                                                                                                    | T,                                                         | 0.5              | 0.7                                              | 1.0             | ns              |  |  |  |  |

| Output Fall Time *4                                                                                                    | T <sub>f</sub>                                             | 0.5              | 0.7                                              | 1.0             | ns              |  |  |  |  |

| Output Delay                                                                                                           | T <sub>do</sub>                                            | 1.5              | 1.9                                              | 2.3             | ns              |  |  |  |  |

| Performance                                                                                                            | do                                                         |                  |                                                  |                 |                 |  |  |  |  |

| Resolution                                                                                                             |                                                            |                  | 8                                                |                 | bits            |  |  |  |  |

| Max. Conversion Rate                                                                                                   | _                                                          | 500              | 0                                                | _               | l               |  |  |  |  |

|                                                                                                                        | F <sub>c</sub>                                             |                  | -                                                | 4.5             | MHz             |  |  |  |  |

| Sampling Delay                                                                                                         | T <sub>ds</sub>                                            | 0.2              | 0.8                                              | 1.5             | ns              |  |  |  |  |

| Aperture Jitter                                                                                                        | T <sub>aj</sub>                                            | _                | 11                                               |                 | ps              |  |  |  |  |

| Integral Linearity Error                                                                                               | _                                                          | _                | ±0.7                                             | LBS             |                 |  |  |  |  |

| Differential Linearity Error                                                                                           | _                                                          | _                | ±0.5                                             | LBS             |                 |  |  |  |  |

| Differential Gain Error *)                                                                                             | _                                                          | 1.0              | _                                                | %               |                 |  |  |  |  |

| Differential Phase Error *                                                                                             | _                                                          | 0.5              |                                                  | deg.            |                 |  |  |  |  |

| *) NTSC 40IRE mod. ram                                                                                                 |                                                            |                  |                                                  |                 |                 |  |  |  |  |

| S/N ratio (Clock Rate 500                                                                                              |                                                            |                  |                                                  |                 |                 |  |  |  |  |

| f <sub>IN</sub> = 1 kHz                                                                                                | 44                                                         | 46               | -                                                | dB              |                 |  |  |  |  |

| f <sub>IN</sub> = 125 MHz                                                                                              | 30                                                         | 34               | -                                                | dΒ              |                 |  |  |  |  |

| Error Rate (Error > 16 LS                                                                                              |                                                            |                  |                                                  |                 |                 |  |  |  |  |

| f <sub>IN</sub> = 100 MHz (Clock R                                                                                     | -                                                          | 10-11            | 10-9                                             | TPS ⁻⁵          |                 |  |  |  |  |

| f <sub>IN</sub> = 125 MHz (Clock R                                                                                     | _                                                          | 10 <sup>-8</sup> | 10-6                                             | TPS *5          |                 |  |  |  |  |

- \*1) Between V<sub>RT</sub> and V<sub>RB</sub> pins \*2) (A/D CLK, A/D CLK)

- \*3) 20 % to 80 % \*4) 80 % to 20 %

- \*5) TPS: Times Per Sample

# **OPERATIONAL NOTES**

- The ADC-309 is an ultra-high speed AD converter with ECL level I/O. As the high-speed digital signal is next to analog signal, the following precautions must be taken in order to obtain optimum performance.

- 2. Properly match the impedance (using micro strip line) to prevent distortion of waveform by the digital signal circuit (clock/data output). The ADC-309 is designed to use line with characteristic impedance of  $50~\Omega$ .

- 3. The ADC-309 operates on single -5.2 V power supply. However, AGND and DGND, and AV<sub>s</sub> and DV<sub>s</sub> are separated to prevent the noise from the digital circuit from leaking to the analog circuit. The board also should be a multi-layer board separated analog region and digital region. Avoid overlapping signal lines and power supply GND in the two regions. Connect AGND and DGND at one location (using a ferrite-bead) to avoid DC offset. The same processing is also necessary for AV<sub>s</sub> and DV<sub>s</sub>.

- 4. Connect all power supply pins and GND pins, not leaving them open.

- 5. Bypass capacitors (approx. 0.1  $\mu$ F) with high frequency characteristics should be used to bypass between AV<sub>s</sub> AGND and DV<sub>s</sub> DGND.

- Make complimentary use of clock input and data output as much as possible in order to obtain stable high performance.

- 7. When mounting the ADC in a socket, use the one with shortest leads.

- The analog input pin V<sub>IN</sub>'s have relatively large input capacitance (approx. 20 pF) for high frequency circuit. The input bandwidth of the ADC-309 is determined mainly by how much the driver can drive this capacitance rather than the characteristics of the IC.

- All four V<sub>IN</sub> pins should be connected directly at shortest distance as possible. The difference in delay between pins causes the distortion at high frequency input signals.

# Description (cont'd)

| Power Supply Requi       | Min.                                      | Тур. | Max. | Units |                 |  |  |  |  |

|--------------------------|-------------------------------------------|------|------|-------|-----------------|--|--|--|--|

| Supply Voltage           | -AV <sub>s</sub> , -DV <sub>s</sub>       | -5.5 | -5.2 | -4.95 | V <sub>DC</sub> |  |  |  |  |

|                          | (-AV <sub>s</sub> ) - (-DV <sub>s</sub> ) | -50  | 0    | +50   | mŬ              |  |  |  |  |

|                          | AGNĎ - DGŇĎ                               | -50  | 0    | +50   | mV              |  |  |  |  |

| Supply Current           | l <sub>s</sub>                            | -680 | -520 | -     | mΑ              |  |  |  |  |

| Power Consumption        | 's<br>P <sub>d</sub>                      | -    | 2.8  | 3.6   | W               |  |  |  |  |

| Physical / Environmental |                                           |      |      |       |                 |  |  |  |  |

| Operating Temperature    | -20                                       | -    | +100 | °C    |                 |  |  |  |  |

| Storage Temperature      | -65                                       | _    | +150 | °C    |                 |  |  |  |  |

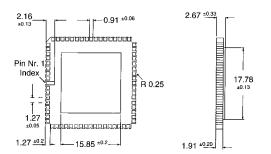

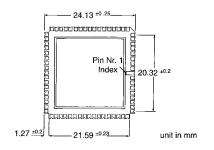

| Package                  | 68 Pin LCC (Ceramic)                      |      |      |       |                 |  |  |  |  |

# Absolute Maximum Ratings (Ta = 25°C)

| Analog                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                           |                                                                                |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|--------------------------------------------------------------------------------|

| $\begin{array}{ccc} \text{Supply Voltage} & -\text{AV}_{\text{S}}, -\text{DV}_{\text{S}} \\ \text{Analog Input Voltage} & \text{V}_{\text{IN}} \\ \text{Reference Input Voltage} & \text{V}_{\text{RT}}, \text{V}_{\text{RB}}, \text{V}_{\text{RM}} \\ & \text{IV}_{\text{RT}} - \text{V}_{\text{RB}} \text{I} \\ \text{V}_{\text{RM}} & \text{Pin Input Current} & \text{I}_{\text{VRM}} \end{array}$ | -7 to +0.5<br>-2.7 to +0.5<br>-AV <sub>s</sub> to +0.5<br>2.5<br>-3 to +3 | V <sub>DC</sub><br>V <sub>DC</sub><br>V <sub>DC</sub><br>V <sub>DC</sub><br>mA |

| Digital                                                                                                                                                                                                                                                                                                                                                                                                |                                                                           |                                                                                |

| Digital Input Voltage MINV, LINV A/D CLK, A/D CLK I A/D CLK - A/D CLK I Digital Output Current Bit 1-8, Bit 1-8, OR, OR                                                                                                                                                                                                                                                                                | -4 to +0.5<br>-DV <sub>s</sub> to +0.5<br>2.7<br>-30 to 0                 | V <sub>DC</sub><br>V <sub>DC</sub><br>V <sub>DC</sub><br>mA                    |

# **OPERATIONAL NOTES (cont'd)**

- 10. The voltages at  $V_{\rm RT}$  and  $V_{\rm RB}$  pins and the internal reference voltages are slightly different due to residual resistance. Therefore,  $V_{\rm RTS}$  and  $V_{\rm RBS}$  are provided to increase their precision. The reference voltage for over range is at 1/2 LSB below  $V_{\rm RTS}$  and

- the lowest input voltage at which the output code changes is at 1/2 LSB above  $\rm V_{\rm RBS}.$  .

- 11. VRM is originally provided to reduce integral linearity error, but there is no need for this. It should simply be kept open.

#### **OPERATIONAL NOTES (cont'd)**

- 12. OR and OR pins are outputs indicating that the input is over range. These pins do not invert at MINV nor LINV.

- 13. When there is noise in the MINV or LINV pins, it is difficult to find the cause from the resulting error. Therefore, provide sufficient margins for the High/Low voltage levels and connect as close to DGND as possible through bypass capacitor (approx. 0.1 μF) with high frequency characteristics. Stable low level can be obtained. The recommended high level input voltage is between -0.5 V and -1.0 V and the low level input voltage is between -1.6 V and -2.5 V.

- 14. Although the electrical characteristics of the ADC-309 depends on the clock duty cycle, this is not significant. Therefore, the electrical characteristics are defined at 50% duty cycle taking into consideration the ease of generating the clock signal.

- 15. Error rate changes with input frequency and input amplitude. The error rate, at the electrical characteristics specific condition which is full scale sine wave input at 1/4 the clock frequency, can be considered close to the upper limit during actual use (when the input signal is below Nyquist frequency).

- 16. When the chip temperature rises, current dissipation increases and the error rate also increases. Sufficient cooling is necessary in order to prolong product life.

### **Mechanical Dimension ADC-309**

# Table 4: Digital Output

This table and the chart below indicate the compatibility between the analog input and the digital output code.

| MINV<br>LINV  |       | 0    |      | 0      |      |      | 1 0    |      |      | 1 1        |      |      |

|---------------|-------|------|------|--------|------|------|--------|------|------|------------|------|------|

| Input Voltage | OR    | MSB  | LSB  | Output |      |      | Coding |      |      | OR         | MSB  | LSB  |

| 0.0000 V      | 1     | 1111 | 1111 | 1      | 1000 | 0000 | 1      | 0111 | 1111 | 1          | 0000 | 0000 |

|               | _ o _ | 1111 | 1111 | 0      | 1000 | 0000 | 0      | 0111 | 1111 | 0          | 0000 | 0000 |

| - 0.0078 V    | 0     | 1111 | 1110 | 0      | 1000 | 0001 | 0      | 0111 | 1110 | 0          | 0000 | 0001 |

| ;             |       |      |      |        |      |      |        |      |      |            |      |      |

| - 0.9922 V    | 0     | 1000 | 0000 | 0      | 1111 | 1111 | 0      | 0000 | 0000 | 0          | 0111 | 1111 |

| - 1.0000 V    | 0     | 0111 | 1111 | 0      | 0000 | 0000 | 0      | 1111 | 1111 | 0          | 1000 | 0000 |

| :             |       |      |      |        |      |      |        |      |      |            |      |      |

| - 1.5000 V    | 0     | 0011 | 1111 | 0      | 0100 | 0000 | 0      | 1011 | 1111 | 0          | 1100 | 0000 |

| :             |       |      |      |        |      |      |        |      |      |            |      |      |

| - 1.7500 V    | 0     | 0001 | 1111 | 0      | 0110 | 0000 | 0      | 1001 | 1111 | 0          | 1110 | 0000 |

| :             |       |      |      |        |      |      |        |      |      |            |      |      |

| - 1.9844 V    | 0     | 0000 | 0001 | 0      | 0111 | 1110 | 0      | 1000 | 0001 | 0          | 1111 | 1110 |

| - 1.9922 V    | 0     | 0000 | 0000 | 0      | 0111 | 1111 | 0      | 1000 | 0000 | 0          | 1111 | 1111 |

| - 2.0000 V    | 0     | 0000 | 0000 | 0      | 0111 | 1111 | 0      | 1000 | 0000 | <u>_</u> 0 | 1111 | 1111 |

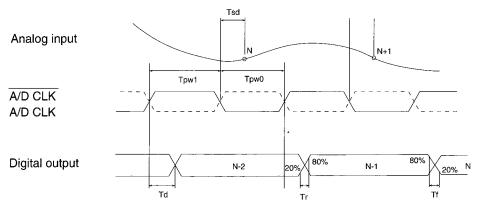

# **Timing Chart**

Tsd = 0.8 ns, Td = 1.9 ns, Tr = Tf = 0.7 ns