## 2X20W Stereo Digital Audio Amplifier with DRC

#### **Features**

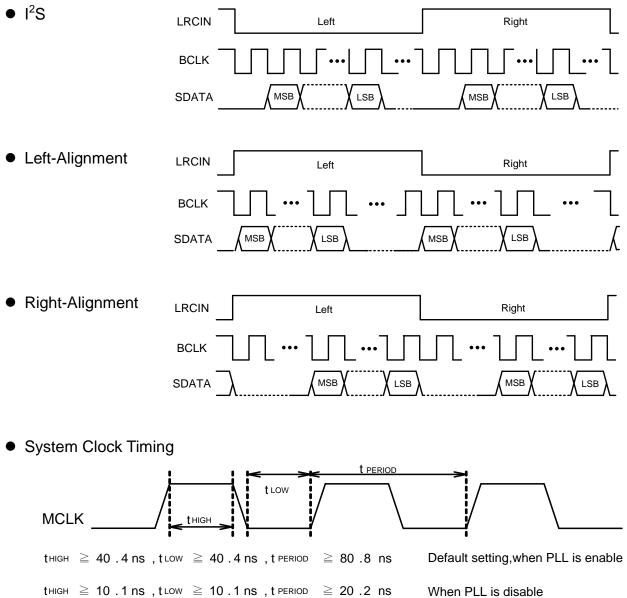

- 16/18/20/24-bit input with I<sup>2</sup>S, Left-alignment and Right-alignment data format

- PSNR & DR(A-weighting)

Loudspeaker: 94dB (PSNR), 106dB (DR) @24V

- Multiple sampling frequencies (Fs) 32kHz / 44.1kHz / 48kHz and 64kHz / 88.2kHz / 96kHz and 128kHz/176.4kHz/192kHz

- System clock = 64x, 128x, 256x, 384x, 512x, 768x, 1024x Fs

256x~1024x Fs for 32kHz / 44.1kHz / 48kHz

128x~512x Fs for 64kHz / 88.2kHz / 96kHz

- 64x~256x Fs for 128kHz/176.4kHz/192kHz

- Supply voltage

3.3V for digital circuit

10V~26V for loudspeaker driver

- Loudspeaker output power for 24V

10W x 2CH into 8Ω @0.16% THD+N for stereo

15W x 2CH into 8Ω @0.18% THD+N for stereo

20W x 2CH into 8Ω @0.24% THD+N for stereo

- Sounds processing including: Volume control (+24dB~-103dB, 0.125dB/step) Dynamic range control Power clipping Channel mixing User programmed noise gate with hysteresis

- window

DC-blocking high-pass filter

- Anti-pop design

- Short circuit and over-temperature protection

- I<sup>2</sup>C control interface

- Internal PLL

- LV Under-voltage shutdown and HV Under-voltage detection

- Power saving mode

- Dynamic temperature control

## **Applications**

- TV audio

- Boom-box, CD and DVD receiver, docking system

- Powered speaker

- Wireless audio

## **Description**

AD82585 is a digital audio amplifier capable of driving a pair of  $8\Omega$ , 20W speaker which operate with play music at a 24V supply without external heat-sink or fan requirement.

Using I<sup>2</sup>C digital control interface, the user can control AD82585's input format selection, mute and volume control functions. AD82585 has many built-in protection circuits to safeguard AD82585 from connection errors.

#### **Ordering Information**

| Product ID      | Package    | Packing / MPQ                                | Comments |  |

|-----------------|------------|----------------------------------------------|----------|--|

| AD82585-LG48NAY | E-LQFP-48L | 250Units / Tray<br>2.5K Units / Box(10 Tray) | 0        |  |

| AD82585-LG48NAR | (7x7 mm)   | 2K Units Tape & Reel                         | - Green  |  |

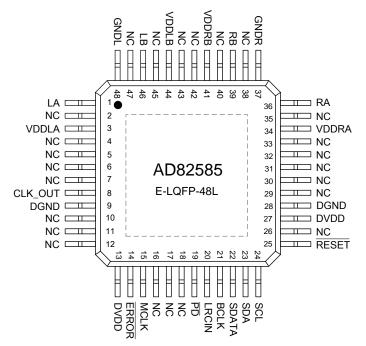

## Pin Assignment (Top View)

#### **Pin Description**

| PIN | NAME    | TYPE | DESCRIPTION               | CHARACTERISTICS                  |

|-----|---------|------|---------------------------|----------------------------------|

| 1   | LA      | 0    | Left channel output A.    |                                  |

| 2   | NC      |      | Not connected.            |                                  |

| 3   | VDDLA   | Р    | Left channel supply A.    |                                  |

| 4   | NC      |      | Not connected.            |                                  |

| 5   | NC      |      | Not connected.            |                                  |

| 6   | NC      |      | Not connected.            |                                  |

| 7   | NC      |      | Not connected.            |                                  |

| 8   | CLK_OUT | 0    | Clock output from PLL.    | TTL output buffer                |

| 9   | DGND    | Р    | Digital ground.           |                                  |

| 10  | NC      |      | Not connected.            |                                  |

| 11  | NC      |      | Not connected.            |                                  |

| 12  | NC      |      | Not connected.            |                                  |

| 13  | DVDD    | Р    | Digital Power.            |                                  |

| 14  | ERROR   | 0    | Error status, low active. | Open-drain output                |

| 15  | MCLK    | I    | Master clock input.       | Schmitt trigger TTL input buffer |

| 16  | NC      |      | Not connected.            |                                  |

| 17  | NC      |      | Not connected.            |                                  |

| 18  | NC      |      | Not connected.            |                                  |

| 19  | PD      | Ι    | Power down, low active    | Schmitt trigger TTL input buffer |

| 20 | LRCIN |     | Left/Right clock input (Fs).                 | Schmitt trigger TTL input buffer |

|----|-------|-----|----------------------------------------------|----------------------------------|

| 21 | BCLK  | I   | Bit clock input (64Fs).                      | Schmitt trigger TTL input buffer |

| 22 | SDATA | I   | Serial audio data input.                     | Schmitt trigger TTL input buffer |

| 23 | SDA   | I/O | I <sup>2</sup> C bi-directional serial data. | Schmitt trigger TTL input buffer |

| 24 | SCL   | Ι   | I <sup>2</sup> C serial clock input.         | Schmitt trigger TTL input buffer |

| 25 | RESET | Ι   | Reset, low active.                           | Schmitt trigger TTL input buffer |

| 26 | NC    |     | Not connected.                               |                                  |

| 27 | DVDD  | Ρ   | Digital power.                               |                                  |

| 28 | DGND  | Ρ   | Digital Ground.                              |                                  |

| 29 | NC    |     | Not connected.                               |                                  |

| 30 | NC    |     | Not connected.                               |                                  |

| 31 | NC    |     | Not connected.                               |                                  |

| 32 | NC    |     | Not connected.                               |                                  |

| 33 | NC    |     | Not connected.                               |                                  |

| 34 | VDDRA | Ρ   | Right channel supply A.                      |                                  |

| 35 | NC    |     | Not connected.                               |                                  |

| 36 | RA    | 0   | Right channel output A.                      |                                  |

| 37 | GNDR  | Р   | Right channel ground.                        |                                  |

| 38 | NC    |     | Not connected.                               |                                  |

| 39 | RB    | 0   | Right channel output B.                      |                                  |

| 40 | NC    |     | Not connected.                               |                                  |

| 41 | VDDRB | Р   | Right channel supply B.                      |                                  |

| 42 | NC    |     | Not connected.                               |                                  |

| 43 | NC    |     | Not connected.                               |                                  |

| 44 | VDDLB | Р   | Left channel supply B.                       |                                  |

| 45 | NC    |     | Not connected.                               |                                  |

| 46 | LB    | 0   | Left channel output B.                       |                                  |

| 47 | NC    |     | Not connected.                               |                                  |

| 48 | GNDL  | Р   | Left channel ground.                         |                                  |

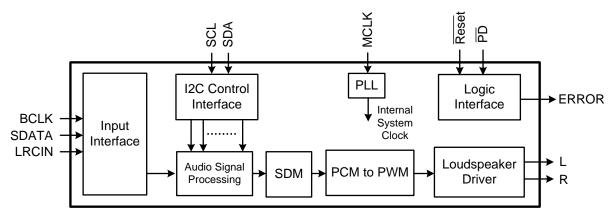

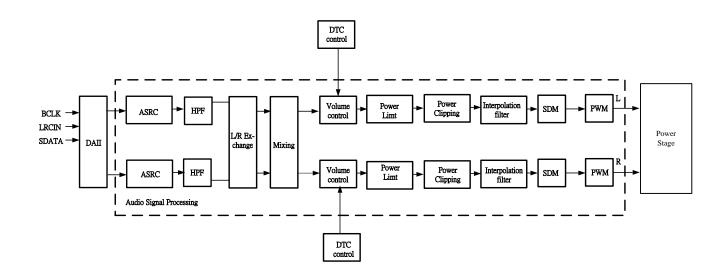

## **Functional Block Diagram**

## Available Package

| Package Type | Device No. | θ <sub>ja</sub> (℃/W) | Ψ <sub>jt</sub> (℃/₩) | θ <sub>jt</sub> (°C/W) | Exposed Thermal Pad |

|--------------|------------|-----------------------|-----------------------|------------------------|---------------------|

| E-LQFP-48L   | AD82585    | 22.9                  | 1.05                  | 34.9                   | Yes (Note1)         |

Note 1.1: The thermal pad is located at the bottom of the package. To optimize thermal performance, soldering the thermal pad to the PCB's ground plane is suggested.

Note 1.2:  $\theta_{ja}$  is measured on a room temperature ( $T_A=25$  °C), natural convection environment test board, which is constructed with a thermally efficient, 4-layers PCB (2S2P). The measurement is tested using the JEDEC51-5 thermal measurement standard.

Note 1.3:  $\theta_{jt}$  represents the heat resistance for the heat flow between the chip and the package's top surface.

Note 1.4:  $\Psi_{jt}$  represents the heat resistance for the heat flow between the chip and the exposed pad's center.

## Absolute Maximum Ratings

Stresses beyond those listed under *absolute maximum ratings* may cause permanent damage to the device.

| Symbol           | Parameter                      | Min  | Max | Units |

|------------------|--------------------------------|------|-----|-------|

| DVDD             | Supply for Digital Circuit     | -0.3 | 3.6 | V     |

| VDDL/R           | Supply for Driver Stage        | -0.3 | 30  | V     |

| V <sub>i</sub>   | Input Voltage                  | -0.3 | 3.6 | V     |

| T <sub>stg</sub> | Storage Temperature            | -65  | 150 | °C    |

| Tj               | Junction Operating Temperature | 0    | 150 | °C    |

## **Recommended Operating Conditions**

| Symbol         | Parameter                      | Тур       | Units |

|----------------|--------------------------------|-----------|-------|

| DVDD           | Supply for Digital Circuit     | 3.15~3.45 | V     |

| VDDL/R         | Supply for Driver Stage        | 10~26     | V     |

| Tj             | Junction Operating Temperature | 0~125     | °C    |

| T <sub>a</sub> | Ambient Operating Temperature  | 0~70      | °C    |

#### **Digital Characteristics**

| Symbol          | Parameter                 | Min | Тур | Max | Units |

|-----------------|---------------------------|-----|-----|-----|-------|

| V <sub>IH</sub> | High-Level Input Voltage  | 2.0 |     |     | V     |

| V <sub>IL</sub> | Low-Level Input Voltage   |     |     | 0.8 | V     |

| V <sub>OH</sub> | High-Level Output Voltage | 2.4 |     |     | V     |

| V <sub>OL</sub> | Low-Level Output Voltage  |     |     | 0.4 | V     |

| Cı              | Input Capacitance         |     | 6.4 |     | pF    |

## **General Electrical Characteristics**

Condition:  $T_a=25$  °C, unless otherwise specified.

| Symbol                                   | Parameter                                              | Condition | Min | Тур | Max | Units |

|------------------------------------------|--------------------------------------------------------|-----------|-----|-----|-----|-------|

| I <sub>PD</sub> (HV)                     | PVDD Supply Current during Power Down                  | PVDD=24V  |     | 40  | 200 | uA    |

| I <sub>PD</sub> (LV)                     | DVDD Supply Current during Power Down                  | DVDD=3.3V |     | 4   | 20  | uA    |

| Junction Temperature for Driver Shutdown |                                                        |           |     | 160 |     | °C    |

| T <sub>SENSOR</sub>                      | Temperature Hysteresis for Recovery from Shutdown      |           |     | 35  |     | °C    |

| UV <sub>H</sub>                          | Under Voltage Disabled (For DVDD)                      |           |     | 2.8 |     | V     |

| UVL                                      | Under Voltage Enabled (For DVDD)                       |           |     | 2.7 |     | V     |

| D da an                                  | Static Drain-to-Source On-state Resistor, PMOS         | PVDD=24V, |     | 260 |     | mΩ    |

| Rds-on                                   | Static Drain-to-Source On-state Resistor, NMOS         | Id=500mA  |     | 175 |     | mΩ    |

| I <sub>SC</sub>                          | L(R) Channel Over-Current Protection (Note 2) PVDD=18V |           |     | 5   |     | А     |

Note 2: Loudspeaker over-current protection is only effective when loudspeaker drivers are properly connected with external LC filters. Please refer to the application circuit example for recommended LC filter configuration.

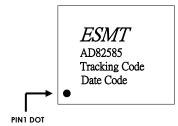

#### **Marking Information**

AD82585

Line 1 : LOGO

Line 2 : Product no.

Line 3 : Tracking Code

Line 4 : Date Code

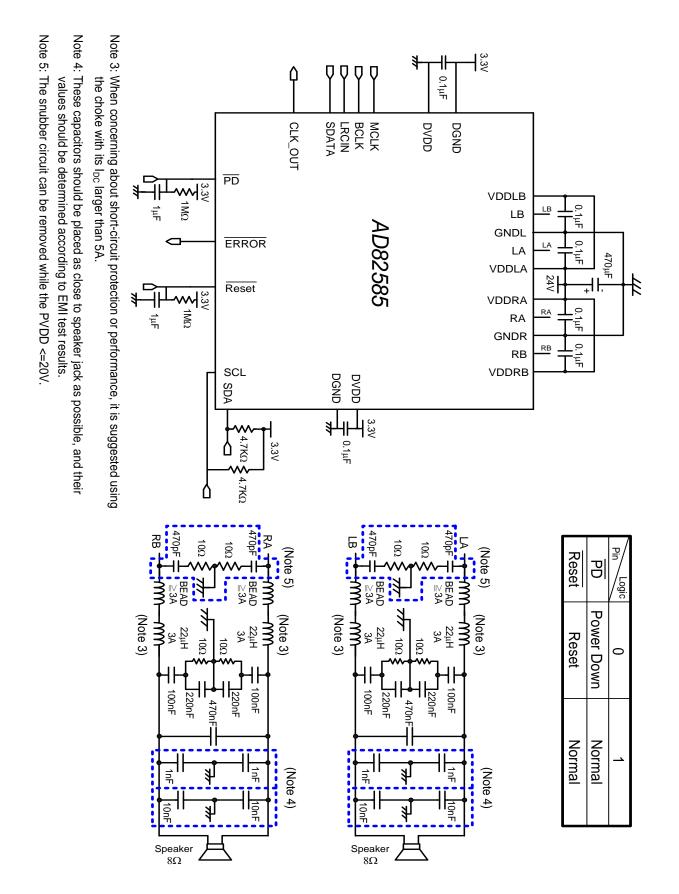

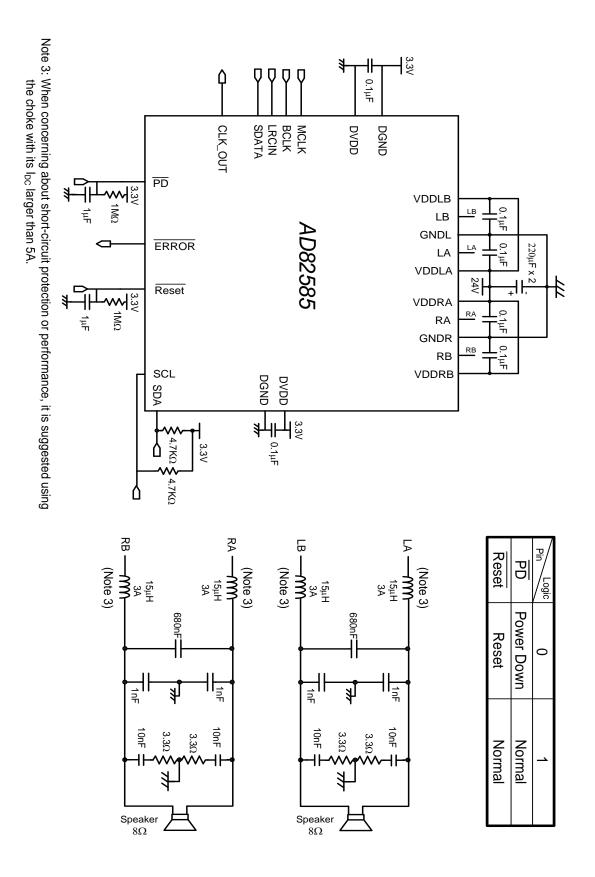

## **Application Circuit Example for Stereo**

## **Application Circuit Example 2 for Stereo**

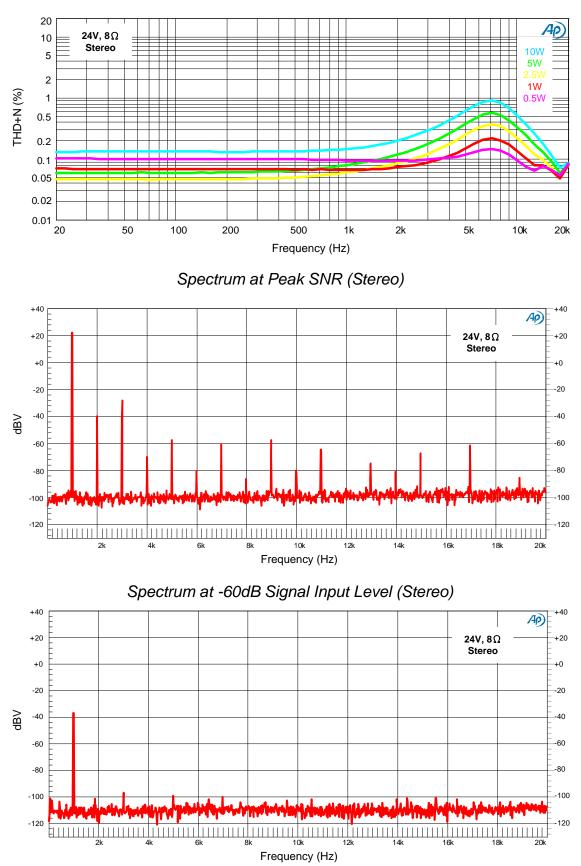

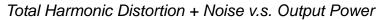

#### **Electrical Characteristics and Specifications for Loudspeaker**

#### Stereo output with 24V supply voltage

Condition:  $T_a=25$  °C, DVDD=3.3V, VDDL=VDDR=24V,  $F_S=48$ kHz, Load=8 $\Omega$  with passive LC lowpass filter (L=15 $\mu$  H with  $R_{DC}=63m\Omega$ , C=680nF); Input is 1kHz sinewave. Volume is 0dB unless otherwise specified.

| Symbol                     | Parameter                         | Condition                  | Input Level | Min | Тур  | Max | Units |

|----------------------------|-----------------------------------|----------------------------|-------------|-----|------|-----|-------|

| _                          | RMS Output Power (THD+N=0.24%)    |                            |             |     | 20   |     | W     |

| P <sub>O</sub><br>(Note 7) | RMS Output Power (THD+N=0.18%)    | +8dB volume                |             |     | 15   |     | W     |

| (                          | RMS Output Power (THD+N=0.16%)    |                            |             |     | 10   |     |       |

| THD+N                      | Total Harmonic Distortion + Noise | P <sub>0</sub> =7.5W       |             |     | 0.14 |     | %     |

| SNR                        | Signal to Noise Ratio (Note 6)    | +8dB volume                | -9dB        |     | 94   |     | dB    |

| DR                         | Dynamic Range (Note 6)            | +8dB volume                | -68dB       |     | 106  |     | dB    |

| PSRR                       | Power Supply Rejection Ratio      | $V_{RIPPLE}=1V_{RMS}$      |             |     | 77   |     | dB    |

|                            |                                   | at 1kHz                    |             |     |      |     |       |

|                            | Channel Separation                | P <sub>O</sub> =1W at 1kHz |             |     | 80   |     | dB    |

Note 6: Measured with A-weighting filter.

Note 7: Thermal dissipation is limited by package type and PCB design, the external heat-sink or system cooling method should be adopted for RMS power output.

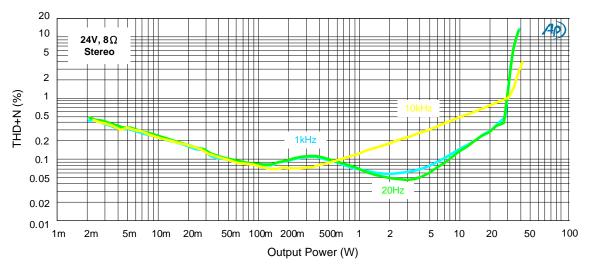

## Total Harmonic Distortion + Noise vs. Output Power (Stereo)

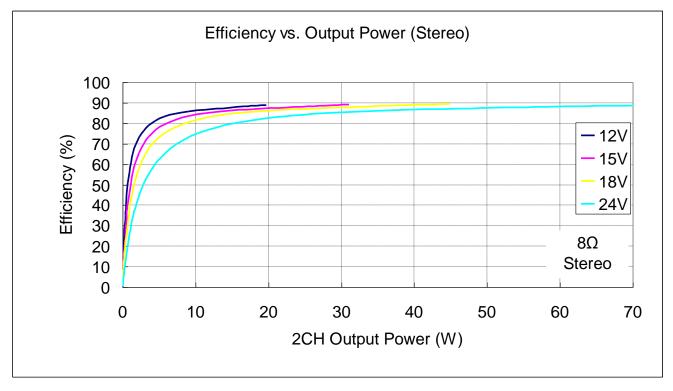

Efficiency (Stereo)

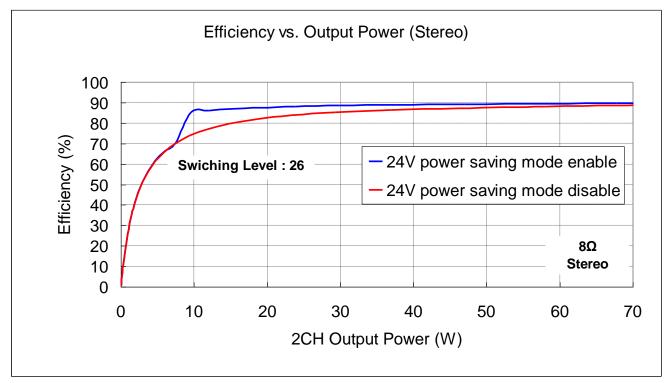

Efficiency (Stereo) for PWM of Power Saving Mode

#### **Interface Configuration**

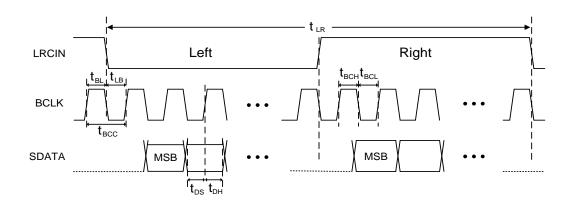

• Timing Relationship (Using I<sup>2</sup>S format as an example)

| Symbol           | Parameter                         | Min    | Тур | Max   | Units |

|------------------|-----------------------------------|--------|-----|-------|-------|

| t <sub>LR</sub>  | LRCIN Period (1/F <sub>s</sub> )  | 10.41  |     | 31.25 | μS    |

| t <sub>BL</sub>  | BCLK Rising Edge to LRCIN Edge    | 50     |     |       | ns    |

| t <sub>LB</sub>  | LRCIN Edge to BCLK Rising Edge    | 50     |     |       | ns    |

| t <sub>BCC</sub> | BCLK Period (1/64F <sub>s</sub> ) | 162.76 |     | 488.3 | ns    |

| t <sub>BCH</sub> | BCLK Pulse Width High             | 81.38  |     | 244   | ns    |

| t <sub>BCL</sub> | BCLK Pulse Width Low              | 81.38  |     | 244   | ns    |

| t <sub>DS</sub>  | SDATA Set-Up Time                 | 50     |     |       | ns    |

| t <sub>DH</sub>  | SDATA Hold Time                   | 50     |     |       | ns    |

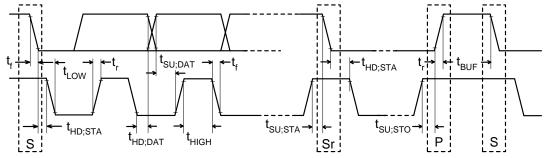

• I<sup>2</sup>C Timing

| Durali                                  |                     | Standard Mode      |      | Fast Mode          |      | L los it |

|-----------------------------------------|---------------------|--------------------|------|--------------------|------|----------|

| Parameter                               | Symbol              | MIN.               | MAX. | MIN.               | MAX. | Unit     |

| SCL clock frequency                     | f <sub>SCL</sub>    | 0                  | 100  | 0                  | 400  | kHz      |

| Hold time for repeated START condition  | t <sub>HD,STA</sub> | 4.0                |      | 0.6                |      | μS       |

| LOW period of the SCL clock             | t <sub>LOW</sub>    | 4.7                |      | 1.3                |      | μS       |

| HIGH period of the SCL clock            | t <sub>HIGH</sub>   | 4.0                |      | 0.6                |      | μS       |

| Setup time for repeated START condition | t <sub>SU;STA</sub> | 4.7                |      | 0.6                |      | μS       |

| Hold time for I <sup>2</sup> C bus data | t <sub>HD;DAT</sub> | 0                  | 3.45 | 0                  | 0.9  | μS       |

| Setup time for $I_2C$ bus data          | t <sub>SU;DAT</sub> | 250                |      | 100                |      | ns       |

| Rise time of both SDA and SDL signals   | t <sub>r</sub>      |                    | 1000 | 20+0.1Cb           | 300  | ns       |

| Fall time of both SDA and SDL signals   | t <sub>f</sub>      |                    | 300  | 20+0.1Cb           | 300  | ns       |

| Setup time for STOP condition           | t <sub>SU;STO</sub> | 4.0                |      | 0.6                |      | μS       |

| Bus free time between STOP and the next | +                   | 4.7                |      | 1.0                |      |          |

| START condition                         | t <sub>BUF</sub>    | 4.7                |      | 1.3                |      | μS       |

| Capacitive load for each bus line       | Cb                  |                    | 400  |                    | 400  | pF       |

| Noise margin at the LOW level for each  | V                   | 0.11/              |      | 0.11/              |      | V        |

| connected device (including hysteresis) | V <sub>nL</sub>     | $0.1V_{DD}$        |      | 0.1V <sub>DD</sub> |      | v        |

| Noise margin at the HIGH level for each | V                   | 0.2V <sub>DD</sub> |      | 0.21/              |      | V        |

| connected device (including hysteresis) | V <sub>nH</sub>     | U.ZVDD             |      | $0.2V_{DD}$        |      | v        |

Elite Semiconductor Memory Technology Inc.

#### **Operation Description**

AD82585 has a built-in PLL with multiple MCLK/FS ratio, which is selected by  $I^2C$  control interface. The volume level default is muted, AD82585 will activate while the de-mute command via  $I^2C$  is programmed.

#### Reset

When the RESET pin is lowered, AD82585 will clear the stored data and reset the register table to default values. AD82585 will exit reset state at the 256<sup>th</sup> MCLK cycle after the  $\overrightarrow{RESET}$  pin is raised to high.

#### • Power down control

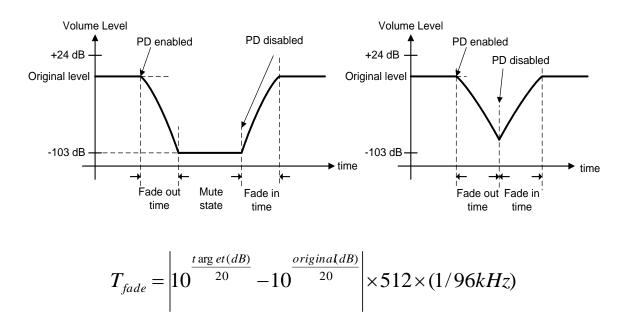

AD82585 has a built-in volume fade-in/fade-out design for PD/Mute function. The relative PD timing diagrams for loudspeakers are shown below.

The volume level will be decreased to  $-\infty$ dB in several LRCIN cycles. Once the fade-out procedure is finished, AD82585 will turn off the power stages, clock signals (for digital circuits) and current (for analog circuits). After PD pin is pulled low, AD82585 requires T<sub>fade</sub> to finish the forementioned work before entering power down state. Users can not program AD82585 during power down state. Also, all settings in the registers will remain intact unless DVDD is removed.

If the PD signal is removed during the fade-out procedure (above, right figure), AD82585 will still execute the fade-in procedure. In addition, AD82585 will establish the analog circuits' bias current and send the clock signals to digital circuits. Afterwards, AD82585 will return to its normal status..

#### • Anti-pop design

AD82585 will generate appropriate control signals to suppress pop sounds during initial power on/off, power down/up, mute, and volume level changes.

#### • Self-protection circuits

AD82585 has built-in protection circuits including thermal, short-circuit and under-voltage detection circuits.

- (i) When the internal junction temperature is higher than 160°C, power stages will be turned off and AD82585 will return to normal operation once the temperature drops to 125°C. The temperature values may vary around 10%.

- (ii) The short-circuit protection circuit protects the output stage when the wires connected to loudspeakers are shorted to each other or GND/VDD. For normal 24V operations, the current flowing through the power stage will be less than 5A for stereo configuration or less than 10A for mono configuration. Otherwise, the short-circuit detectors may pull the ERROR pin to DGND, disabling the output stages. When the over-temperature or short-circuit condition occurs, the open-drain ERROR pin will be pulled low and latched into ERROR state. Once the over-temperature or short-circuit condition is removed, AD82585 will exit ERROR state when one of the following conditions is met: (1) RESET pin is pulled low, (2) PD pin is pulled low, (3) Master mute is enabled through the I<sup>2</sup>C interface.

- (iii) Once the DVDD voltage is lower than 2.7V, AD82585 will turn off its loudspeaker power stages and cease the operation of digital processing circuits. When DVDD becomes larger than 2.8V, AD82585 will return to normal operation.

- (iv) If the master clock inputted into MCLK pin stops during the period for 500 ns or more, AD82585 detect the stop of MCK. In this state, amplifier outputs are forced to Weak Low. If master clock is inputted normally again, ERROR pin is set to low. AD82585 won't leave ERROR state until one of the following conditions: (1) Reset pin is pulled low, (2) PD pin is pulled low, (3) Programming master mute via I<sup>2</sup>C interface.

- PD pin is set to low, when stop the clock inputted into MCLK, BCLK, and LRCIN during operation.

- (v) If it will be in the state where PVDD power supply is OFF and DVDD power supply is ON, ERROR pin is set to Low.

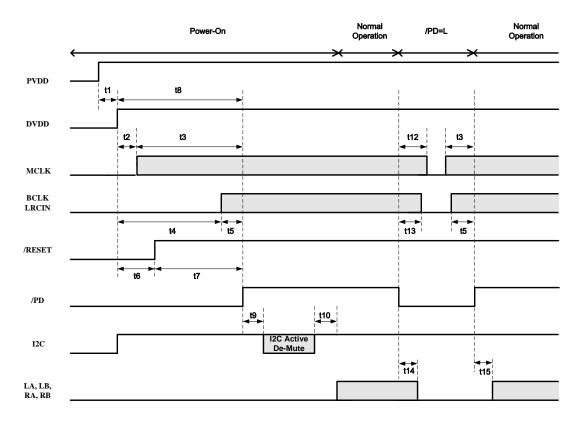

#### • Power on sequence

Hereunder is AD82585's power on sequence. AD82585 the default volume level is muted, give a de-mute command via  $I^2C$  when the whole system is stable to activate it.

| Symbol | Condition | Min | Max | Units |

|--------|-----------|-----|-----|-------|

| t1     |           | 0   | -   | msec  |

| t2     |           | 0   | -   | msec  |

| t3     |           | 10  | -   | msec  |

| t4     |           | 0   | -   | msec  |

| t5     |           | 10  | -   | msec  |

| t6     |           | 10  | -   | msec  |

| t7     |           | 0   | -   | msec  |

| t8     |           | 200 | -   | msec  |

| t9     |           | 20  | -   | msec  |

| t10    |           | -   | 0.1 | msec  |

| t12    |           | 25  | -   | msec  |

| t13    |           | 25  | -   | msec  |

| t14    |           | -   | 22  | msec  |

| t15    |           | -   | 0.1 | msec  |

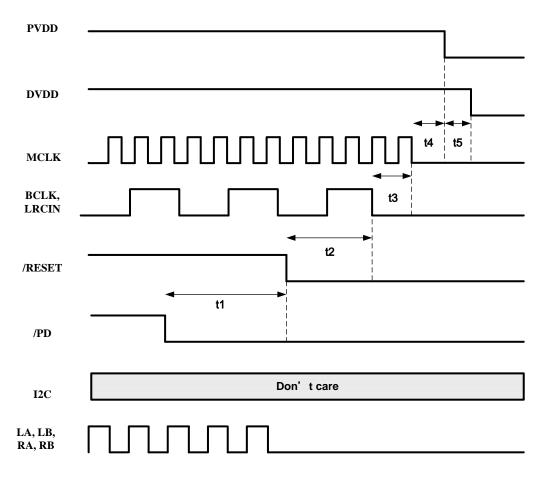

#### • Power off sequence

Hereunder is AD82585's power off sequence.

| Symbol | Condition | Min | Max | Units |

|--------|-----------|-----|-----|-------|

| t1     |           | 35  | -   | msec  |

| t2     |           | 0.1 | -   | msec  |

| t3     |           | 0   | -   | msec  |

| t4     |           | 1   | -   | msec  |

| t5     |           | 1   | -   | msec  |

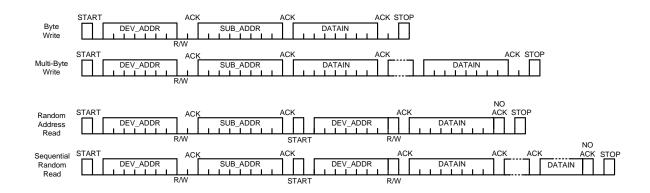

## I<sup>2</sup>C-Bus Transfer Protocol

#### Introduction

AD82585 employs I<sup>2</sup>C-bus transfer protocol. Two wires, serial data and serial clock carry information between the devices connected to the bus. Each device is recognized by a unique 7-bit address and can operate as either a transmitter or a receiver. The master device initiates a data transfer and provides the serial clock on the bus. AD82585 is always an I<sup>2</sup>C slave device.

#### Protocol

#### START and STOP condition

START is identified by a high to low transition of the SDA signal. A START condition must precede any command for data transfer. A STOP is identified by a low to high transition of the SDA signal. A STOP condition terminates communication between AD82585 and the master device on the bus. In both START and STOP, the SCL is stable in the high state.

#### Data validity

The SDA signal must be stable during the high period of the clock. The high or low change of SDA only occurs when SCL signal is low. AD82585 samples the SDA signal at the rising edge of SCL signal.

#### Device addressing

The master generates 7-bit address to recognize slave devices. When AD82585 receives 7-bit address matched with 0110000, AD82585 will acknowledge at the 9<sup>th</sup> bit (the 8<sup>th</sup> bit is for R/W bit). The bytes following the device identification address are for AD82585 internal sub-addresses.

#### Data transferring

Each byte of SDA signaling must consist of 8 consecutive bits, and the byte is followed by an acknowledge bit. Data is transferred with MSB first, as shown in the figure below. In both write and read operations, AD82585 supports both single-byte and multi-byte transfers. Refer to the figure below for detailed data-transferring protocol.

#### **Register Table**

The audio signal processing data flow is shown as the following figure. Users can control these function by programming appropriate setting to register table. In this section, the register table is summarized first. The definition of each register follows in the next section.

| Address | Register    | B[7]            | B[6]     | B[5]     | B[4]    | B[3]       | B[2]       | B[1]       | B[0]       |

|---------|-------------|-----------------|----------|----------|---------|------------|------------|------------|------------|

| 0X00    | SCTL1       | IF[2]           | IF[1]    | IF[0]    | LREXC   | PWML_X     | PWMRX      | PwmMode    | NGE        |

| 0X01    | SCTL 2      | Rese            | erved    | FS[1]    | FS[0]   | PMF[3]     | PMF[2]     | PMF[1]     | PMF[0]     |

| 0X02    | SCTL 3      | EN_CLKO         | HPB      | LV_UVSEL | SW_RSTB | MUTE       | CM1        | CM2        | CompSDMEn  |

| 0X03    | MVOL        | MV[7]           | MV[6]    | MV[5]    | MV[4]   | MV[3]      | MV[2]      | MV[1]      | MV[0]      |

| 0X04    | C1VOL       | C1V[7]          | C1V[6]   | C1V[5]   | C1V[4]  | C1V[3]     | C1V[2]     | C1V[1]     | C1V[0]     |

| 0X05    | C2VOL       | C2V[7]          | C2V[6]   | C2V[5]   | C2V[4]  | C2V[3]     | C2V[2]     | C2V[1]     | C2V[0]     |

| 0X06    | HVUV        | DIS_HVUV        |          | Reserved |         | HVUVSEL[3] | HVUVSEL[2] | HVUVSEL[1] | HVUVSEL[0] |

| 0X07    | SCTL 4      | C1MX_EN         | C2MX_EN  | PC_EN    | DRC_EN  | Reserved   |            |            |            |

| 0X08    | LAR         | LA[3]           | LA[2]    | LA[1]    | LA[0]   | LR[3]      | LR[2]      | LR[1]      | LR[0]      |

| 0X09    | QT_SW_LEVEL |                 | Reserved |          | QTS[4]  | QTS[3]     | QTS[2]     | QTS[1]     | QTS[0]     |

| 0X0A    |             |                 |          |          | R       | eserved    |            |            |            |

| 0X0B    | OC SET      |                 |          |          | R       | eserved    |            |            |            |

| 0X0C    | STATUS      |                 |          |          | R       | eserved    |            |            |            |

| 0X0D    | ACFG        |                 |          |          | R       | eserved    |            |            |            |

| 0X0E    | TM_CTRL     |                 |          |          | R       | eserved    |            |            |            |

| 0X0F    | PWM_CTRL    |                 | Reserved |          |         |            |            |            |            |

| 0X10    | ATT         | Reserved ATT[4] |          |          | ATT[4]  | ATT[3]     | ATT[2]     | ATT[1]     | ATT[0]     |

| 0X11    | ATM         | ATM[7]          | ATM[6]   | ATM[5]   | ATM[4]  | ATM[3]     | ATM[2]     | ATM[1]     | ATM[0]     |

| 0X12    | ATB         | ATB[7]          | ATB[6]   | ATB[5]   | ATB [4] | ATB [3]    | ATB [2]    | ATB [1]    | ATB [0]    |

Elite Semiconductor Memory Technology Inc.

# AD82585

| 0X13 | PCT     | Reserved   |            |            | PCT[4]          | PCT[3]      | PCT[2]     | PCT[1]     | PCT[0]     |

|------|---------|------------|------------|------------|-----------------|-------------|------------|------------|------------|

| 0X14 | PCM     | PCM[7]     | PCM[6]     | PCM[5]     | PCM[4]          | PCM[3]      | PCM[2]     | PCM[1]     | PCM[0]     |

| 0X15 | PCB     | PCB[7]     | PCB[6]     | PCB[5]     | PCB [4]         | PCB [3]     | PCB [2]    | PCB [1]    | PCB [0]    |

| 0X16 | NGG     |            | Reserved   |            | DIS_ZD<br>_FADE | Rese        | erved      | NG_GAIN[1] | NG_GAIN[0] |

| 0X17 | VFT     | MV_FT[1]   | MV_FT[0]   | C1V_FT[1]  | C1V_FT[0]       | C2V_FT[1]   | C2V_FT[0]  | Res        | erved      |

| 0X18 | DTC     | DTC_EN     | DTC_TH[1]  | DTC_TH[0]  | DTC_RATE[1]     | DTC_RATE[0] |            | Reserved   |            |

| 0X19 |         |            | Reserved   |            |                 |             |            |            |            |

| 0X1A | NGALT   | NGALT[7]   | NGALT[6]   | NGALT[5]   | NGALT[4]        | NGALT[3]    | NGALT[2]   | NGALT[1]   | NGALT[0]   |

| 0X1B | NGALM   | NGALM[7]   | NGALM[6]   | NGALM[5]   | NGALM[4]        | NGALM[3]    | NGALM[2]   | NGALM[1]   | NGALM[0]   |

| 0X1C | NGALB   | NGALB[7]   | NGALB [6]  | NGALB [5]  | NGALB [4]       | NGALB [3]   | NGALB [2]  | NGALB [1]  | NGALB [0]  |

| 0X1D | NGRLT   | NGRLT[7]   | NGRLT[6]   | NGRLT[5]   | NGRLT[4]        | NGRLT[3]    | NGRLT[2]   | NGRLT[1]   | NGRLT[0]   |

| 0X1E | NGRLM   | NGRLM[7]   | NGRLM[6]   | NGRLM[5]   | NGRLM[4]        | NGRLM[3]    | NGRLM[2]   | NGRLM[1]   | NGRLM[0]   |

| 0X1F | NGRLB   | NGRLB[7]   | NGRLB [6]  | NGRLB[5]   | NGRLB[4]        | NGRLB [3]   | NGRLB [2]  | NGRLB [1]  | NGRLB [0]  |

| 0X20 | DRC_ECT | DRC_ECT[7] | DRC_ECT[6] | DRC_ECT[5] | DRC_ECT[4]      | DRC_ECT[3]  | DRC_ECT[2] | DRC_ECT[1] | DRC_ECT[0] |

| 0X21 | DRC_ECB | DRC_ECB[7] | DRC_ECB[6] | DRC_ECB[5] | DRC_ECB[4]      | DRC_ECB[3]  | DRC_ECB[2] | DRC_ECB[1] | DRC_ECB[0] |

| 0X22 | RTT     | Reserved   |            |            | RTT[4]          | RTT[3]      | RTT[2]     | RTT[1]     | RTT[0]     |

| 0X23 | RTM     | RTM[7]     | RTM[6]     | RTM[5]     | RTM[4]          | RTM[3]      | RTM[2]     | RTM[1]     | RTM[0]     |

| 0X24 | RTB     | RTB[7]     | RTB[6]     | RTB[5]     | RTB [4]         | RTB [3]     | RTB [2]    | RTB [1]    | RTB [0]    |

#### **Detail Description for Register**

In this section, please note that the highlighted columns are the default value of these tables. If no highlighted, it is because the default setting of this bit is determined by external pin.

## • Address 0X00 : State Control 1

AD82585 support multiple serial data input formats including I<sup>2</sup>S, Left-alignment and Right-alignment. These formats is chosen by user via bit7~bit5 of address 0.

| BIT    | NAME         | DESCRIPTION           | VALUE | FUNCTION                    |

|--------|--------------|-----------------------|-------|-----------------------------|

|        |              |                       |       | I <sup>2</sup> S 16-24 bits |

|        |              |                       | 001   | Left-alignment 16-24 bits   |

|        |              |                       | 010   | Right-alignment 16 bits     |

| B[7:5] | IF[2:0]      | Input Format          | 011   | Right-alignment 18 bits     |

|        |              |                       | 100   | Right-alignment 20 bits     |

|        |              |                       | 101   | Right-alignment 24 bits     |

|        |              |                       | other | Reversed                    |

| B[4]   | LREXC        | Left/Right (L/R)      | 0     | No exchanged                |

| D[4]   | LINEXC       | Channel Exchanged     | 1     | L/R exchanged               |

| B[3]   | PWML X       |                       | 0     | No exchange                 |

| D[3]   |              | LA/LB Exchange        | 1     | Exchange                    |

| DIOI   |              |                       | 0     | No exchange                 |

| B[2]   | PWMR_X       | RA/RB Exchange        | 1     | Exchange                    |

| B[1]   | PwmMode      | Dowor Soving Mode     | 0     | Quarternary+Ternary         |

| БП     | r williviode | Power Saving Mode     | 1     | Quarternary                 |

| B[0]   | NGE          | Noice Cate Enable     | 0     | Disable                     |

| БГОЈ   | NGE          | NGE Noise Gate Enable |       | Enable                      |

## • Address 0X01 : State Control 2

AD82585 has built-in PLL internally. It can support the multiple MCLK/FS ratio as the below this table.

| BIT    | NAME | DESCRIPTION        | VALUE | FUNCTION        |

|--------|------|--------------------|-------|-----------------|

| B[7:6] | Х    | Reserved           |       |                 |

|        |      |                    | 00    | 32/44.1/48kHz   |

| D[5·4] | FS   | Sompling Frequency | 01    | 32/44.1/48kHz   |

| B[5:4] | го   | Sampling Frequency | 10    | 64/88.2/96kHz   |

|        |      |                    | 11    | 96/176.4/192kHz |

Multiple MCLK/FS Ratio Setting table

| BIT    | NAME          | DESCRIPTION | VALUE   | B[5:4]=00/01 | B[5:4]=10 | B[5:4]=11 |

|--------|---------------|-------------|---------|--------------|-----------|-----------|

|        |               |             |         | Reset        | Reset     | Reset     |

|        | NA 141-1-     | 0001        | Default | Default      | Default   |           |

| D[2:0] |               | -           |         | (256x)       | (128x)    | (64x)     |

| B[3:0] | PMF[3:0]      |             | 0010    | 512x         | 256x      | 128x      |

|        | Ratio Setting | 0011        | 768x    | 384x         | 192x      |           |

|        |               | 0100        | 1024x   | 512x         | 256x      |           |

#### • Address 0X02 : State Control 3

To prevent the DC current from damaging the speaker, a high pass filter (3dB frequency = 5Hz) is built into the AD82585. It can be enabled or disabled by bit 6 of address 2.

AD82585 has a mute function which includes master mute and individual channel mute modes. When the master mute mode is enabled, both left and right processing channels are muted. On the other hand, either channel can be muted by using the channel mute mode. When the mute function is enabled or disabled, the fade-out or fade-in process will be initiated.

| BIT  | NAME        | DESCRIPTION        | VALUE | FUNCTION         |

|------|-------------|--------------------|-------|------------------|

| ודום | EN_CLK_     |                    | 0     | Disabled         |

| B[7] | OUT         | PLL Clock Output   | 1     | Enabled          |

| DIC1 | HPB         | DC Blocking HPF    | 0     | Enable           |

| B[6] | пгр         | Bypass             | 1     | Disabled         |

| DIEI |             | LV Under Voltage   | 0     | 2.7V             |

| B[5] | LV_UVSEL    | Selection          | 1     | 3.0V             |

| D[4] |             |                    | 0     | Reset            |

| B[4] | SW_RSTB     | Software reset     | 1     | Normal operating |

| DIOI | MUTE        |                    | 0     | Un-Mute          |

| B[3] | NUTE        | Master Mute        | 1     | Mute             |

| D[0] | CM1         | Channel 1 Mute     | 0     | Un-Mute          |

| B[2] | CIVIT       | Channel T Mule     | 1     | Mute             |

| D[4] | CM2         | Channel 2 Mute     | 0     | Un-Mute          |

| B[1] | CIVIZ       |                    | 1     | Mute             |

| B[0] | CompSDMEn   | Compensate SDM     | 0     | Disable          |

| 5[0] | CompoDivien | Frequency Response | 1     | Enable           |

#### • Address 0X03 : Master volume

AD82585 supports both master-volume and channel-volume control for the stereo processing channels. Both master volume control (Address 0X03) and channel volume (Address 0X04 and 0X05) settings range from +12dB ~ -102dB. Given master volume level, say, Level A (in dB unit) and channel volume level, say Level B (in dB unit), the total volume equals to Level A plus with Level B and its range is from +24dB ~ -102dB, i.e., -103dB  $\leq$  Total Volume (Level A + Level B)  $\leq$  +24dB.

| BIT    | NAME        | DESCRIPTION   | VALUE    | FUNCTION |

|--------|-------------|---------------|----------|----------|

|        |             |               | 00000000 | +12dB    |

|        |             |               | 00000001 | +11.5dB  |

|        |             |               | 00000010 | +11dB    |

|        |             |               | :        | :        |

|        |             |               | 00010111 | 0.5dB    |

| D[7:0] | MV[7:0]     |               | 00011000 | 0dB      |

| B[7:0] | 101 V [7.0] | Master Volume | 00011001 | -0.5dB   |

|        |             |               | :        | :        |

|        |             |               | 11100110 | -103dB   |

|        |             |               | 11100101 | -∞dB     |

|        |             |               | :        | :        |

|        |             |               | 1111111  | -∞dB     |

#### • Address 0X04 : Channel 1 volume

| BIT    | NAME     | DESCRIPTION      | VALUE    | FUNCTION |

|--------|----------|------------------|----------|----------|

|        |          |                  | 00000000 | +12dB    |

|        |          |                  | 00000001 | +11.5dB  |

|        |          |                  | ••       | :        |

|        |          |                  | 00010100 | 2dB      |

|        |          |                  | ••       | :        |

| D[7:0] | C1V[7:0] |                  | 00011000 | 0dB      |

| B[7:0] |          | Channel 1 Volume | 00011001 | -0.5dB   |

|        |          |                  | ••       | :        |

|        |          |                  | 11100110 | -103dB   |

|        |          |                  | 11100101 | -∞dB     |

|        |          |                  | •        | :        |

|        |          |                  | 1111111  | -∞dB     |

#### • Address 0X05 : Channel 2 volume

| BIT    | NAME     | DESCRIPTION        | VALUE    | FUNCTION |

|--------|----------|--------------------|----------|----------|

|        |          |                    | 00000000 | +12dB    |

|        |          |                    | 00000001 | +11.5dB  |

|        |          |                    | :        | :        |

|        |          |                    | 00010100 | 2dB      |

|        |          | ) Channel 2 Volume | :        | :        |

| B[7:0] | C2V[7:0] |                    | 00011000 | 0dB      |

| Ы(7.0) | 020[7.0] |                    | 00011001 | -0.5dB   |

|        |          |                    | :        | :        |

|        |          |                    | 11100110 | -103dB   |

|        |          |                    | 11100101 | -∞dB     |

|        |          |                    | :        | :        |

|        |          |                    | 1111111  | -∞dB     |

## • Address 0X06 : Under Voltage Selection for High Voltage Supply

AD82585 provides HV under voltage detection which can be enable or disable via bit 7. The under-voltage detection level is programmable via bit3~ bit0. Once the output stage voltage drops below the preset value (see table), AD82585 will fade out audio signals to turn off the speaker.

| BIT    | NAME         | DESCRIPTION        | VALUE | FUNCTION |

|--------|--------------|--------------------|-------|----------|

| ודום   |              | Disable HV Under   | 0     | Enable   |

| B[7]   | Dis_HVUV     | Voltage Circuit    | 1     | Disable  |

| B[6:4] | Х            | Reserved           |       |          |

|        |              |                    | Other | 9.7V     |

|        |              |                    | 1100  | 19.5V    |

| D[2:0] | HVUVSEL[3:0] | HV Under Voltage   | 0100  | 15.5V    |

| B[3:0] |              | Selection (Active) | 0011  | 13.2V    |

|        |              |                    | 0001  | 9.7V     |

|        |              |                    | 0000  | 8.2V     |

## • Address 0X07 : State Control 4

AD82585 provides channel mix, power clipping, and dynamic range control (DRC) function. These functions can be enable or not as the following table.

| BIT    | NAME       | DESCRIPTION     | VALUE | FUNCTION        |

|--------|------------|-----------------|-------|-----------------|

| ודום   | C1MX EN    | Channel1 Mixing | 0     | Disable(MONO=0) |

| B[7]   |            | Enable          | 1     | Enable (MONO=1) |

| DIGI   | C2MX EN    | Channel2 Mixing | 0     | Disable(MONO=0) |

| B[6]   | CZIVIA_EIN | Enable          | 1     | Enable(MONO=1)  |

| DIEI   | PC EN      | Power Clipping  | 0     | Disable         |

| B[5]   | PC_EN      | Enable          | 1     | Enable          |

| D[4]   |            | DBC Enchlo      | 0     | Disable         |

| B[4]   | DRC_EN     | DRC Enable      | 1     | Enable          |

| B[3:0] | Х          | Reserved        |       |                 |

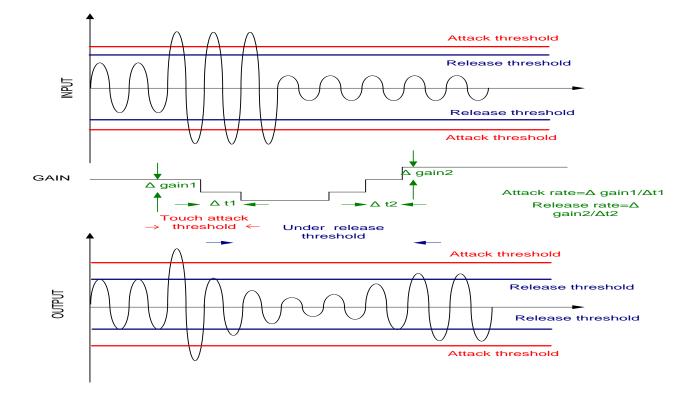

• Address 0X08 : Attack Rate and Release Rate for Dynamic Range Control (DRC) The attack/release rates of AD82585 are defined as following table,

| BIT            | NAME    | DESCRIPTION      | VALUE | FUNCTION     |

|----------------|---------|------------------|-------|--------------|

|                |         |                  | 0000  | 3 dB/ms      |

|                |         |                  | 0001  | 2.667 dB/ms  |

|                |         |                  | 0010  | 2.182 dB/ms  |

|                |         |                  | 0011  | 1.846 dB/ms  |

|                |         |                  | 0100  | 1.333 dB/ms  |

|                |         |                  | 0101  | 0.889 dB/ms  |

|                |         |                  | 0110  | 0.4528 dB/ms |

| B[7:5]         | LA[3:0] | DRC Attack Rate  | 0111  | 0.2264 dB/ms |

| ы, тр          | LA[3.0] |                  | 1000  | 0.15 dB/ms   |

|                |         |                  | 1001  | 0.1121 dB/ms |

|                |         |                  | 1010  | 0.0902 dB/ms |

|                |         |                  | 1011  | 0.0752 dB/ms |

|                |         |                  | 1100  | 0.0645 dB/ms |

|                |         |                  | 1101  | 0.0563 dB/ms |

|                |         |                  | 1110  | 0.0501 dB/ms |

|                |         |                  | 1111  | 0.0451 dB/ms |

|                |         |                  | 0000  | 0.5106 dB/ms |

|                |         |                  | 0001  | 0.1371 dB/ms |

|                |         |                  | 0010  | 0.0743 dB/ms |

|                |         |                  | 0011  | 0.0499 dB/ms |

|                |         |                  | 0100  | 0.0360 dB/ms |

|                |         |                  | 0101  | 0.0299 dB/ms |

|                |         |                  | 0110  | 0.0264 dB/ms |

| <b>D</b> [2:0] |         | DRC Release Rate | 0111  | 0.0208 dB/ms |

| B[3:0]         | LR[3:0] | DRC Release Rale | 1000  | 0.0198 dB/ms |

|                |         |                  | 1001  | 0.0172 dB/ms |

|                |         |                  | 1010  | 0.0147 dB/ms |

|                |         |                  | 1011  | 0.0137 dB/ms |

|                |         |                  | 1100  | 0.0134 dB/ms |

|                |         |                  | 1101  | 0.0117 dB/ms |

|                |         |                  | 1110  | 0.0112 dB/ms |

|                |         |                  | 1111  | 0.0104 dB/ms |

#### • Address 0X09 : Quaternary and Ternary Switching Level

If the PWM exceeds the programmed switching power level (default 30\*40ns), the modulation algorithm will change from quaternary to ternary modulation. Ternary modulation has less switching loss, resulting in higher power efficiency during larger power output operations. If the PWM drops below the programmed switching power level, the modulation algorithm will change back to quaternary modulation.

| BIT    | NAME     | DESCRIPTION     | VALUE | FUNCTION |

|--------|----------|-----------------|-------|----------|

| B[7:5] | Х        | Reserved        |       |          |

|        |          |                 | 11111 | 62       |

|        |          |                 | 11110 | 60       |

|        |          |                 | :     | :        |

|        |          |                 | :     | :        |

|        |          | Quaternary and  | 10000 | 32       |

| B[4:0] | QTS[4:0] | Ternary         | 01111 | 30       |

|        |          | Switching Level | 01110 | 28       |

|        |          |                 | 01101 | 26       |

|        |          |                 | :     | :        |

|        |          |                 | 00001 | 4        |

|        |          |                 | 00000 | 4        |

• Address 0X10 : Top 5 Bits of Attack Threshold for Dynamic Range Control (DRC)

The AD82585 provides dynamic range control function. When the input RMS exceeds the programmable attack threshold value, the output power will be limited by this threshold power level via gradual gain reduction. Attack threshold is defined by 21-bit representation composed of registers controlled by I2C. The device addresses of DRC attack threshold are 0X10, 0X11, and 0X12.

| BIT    | NAME     | DESCRIPTION          | VALUE | FUNCTION        |

|--------|----------|----------------------|-------|-----------------|

| B[7:5] | Х        | Reserved             |       |                 |

| P[4:0] |          | Top 5 Bits of Attack | Х     | User programmed |

| B[4:0] | ATT[4:0] | Threshold            | 01000 | 0dB             |

#### • Address 0X11 : Middle 8 Bits of Attack Threshold

| BIT    | NAME     | DESCRIPTION             | VALUE    | FUNCTION        |

|--------|----------|-------------------------|----------|-----------------|

|        |          | Middle 8 Bits of Attack | Х        | User programmed |

| B[7:0] | ATM[7:0] | Threshold               | 00000000 | 0dB             |

• Address 0X12 : Bottom 8 Bits of Attack Threshold

| BIT    | NAME     | DESCRIPTION             | VALUE    | FUNCTION        |

|--------|----------|-------------------------|----------|-----------------|

|        |          | Bottom 8 Bits of Attack | Х        | User programmed |

| B[7:0] | ATB[7:0] | Threshold               | 00000000 | 0dB             |

#### • Address 0X13 : Top 8 Bits of Power Clipping

The AD82585 provides power clipping function to avoid excessive signal that may destroy loud speaker. The power clipping level is defined by 21-bit representation composed of registers controlled by I2C. The device addresses of power clipping threshold are 0X13, 0X14, and 0X15.

| BIT    | NAME     | DESCRIPTION         | VALUE | FUNCTION        |

|--------|----------|---------------------|-------|-----------------|

| B[7:5] | Х        | Reserved            |       |                 |

| P[4:0] |          | Top 5 Bits of Power | Х     | User programmed |

| B[4:0] | PCT[4:0] | Clipping            | 01000 | 0dB             |

#### • Address 0X14 : Middle 8 Bits of Power Clipping

| BIT    | NAME     | DESCRIPTION            | VALUE    | FUNCTION        |

|--------|----------|------------------------|----------|-----------------|

|        |          | Middle 8 Bits of Power | Х        | User programmed |

| B[7:0] | PCM[7:0] | Clipping Level         | 00000000 | 0dB             |

#### • Address 0X15 : Bottom 8 Bits of Power Clipping Level

| BIT    | NAME                   | DESCRIPTION    | VALUE           | FUNCTION |

|--------|------------------------|----------------|-----------------|----------|

|        | Bottom 8 Bits of Power | Х              | User programmed |          |

| B[7:0] | PCB[7:0]               | Clipping Level | 00000000        | 0dB      |

The following table shows the power clipping level's numerical representation.

| Sample Calculation for Power C | Clipping |

|--------------------------------|----------|

|--------------------------------|----------|

| Max        | ٩D | Lincor                 | Desimal    | Hex           |

|------------|----|------------------------|------------|---------------|

| amplitude  | dB | Linear                 | Decimal    | (2.19 format) |

| PVDD       | 0  | 1                      | 524288     | 80000         |

| PVDD*0.707 | -3 | 0.707                  | 370727     | 5A827         |

| PVDD*0.5   | -6 | 0.5                    | 262144     | 40000         |

| PVDD*L     | х  | L=10 <sup>(x/20)</sup> | D=524288xL | H=dec2hex(D)  |

#### • Address 0X16 : Noise Gate Gain Control

AD82585 provide noise gate function if receiving 2048 signal sample points less than noise gate attack level. User can change noise gate gain via bit1~ bit0. When noise gate function occurs, input signal will multiply noise gate gain (x1/8, x1/4 x1/2, x0). User can select fade out or not via bit 4.

| BIT    | NAME        | DESCRIPTION        | VALUE | FUNCTION |

|--------|-------------|--------------------|-------|----------|

| B[7:5] | х           | Reserved           |       |          |

| D[4]   |             | Disable Noise Gate | 0     | Fade     |

| B[4]   | DIS_NG_FADE | Fade               | 1     | No fade  |

| B[3:2] | Х           | Reserved           |       |          |

|        |             |                    | 00    | x1/8     |

| D[1:0] |             | Noise Gate         | 01    | x1/4     |

| B[1:0] | NG_GAIN     | Detection Gain     | 10    | x1/2     |

|        |             |                    | 11    | Mute     |

#### • Address 0X17 : Volume Fine Tune

AD82585 supports both master-volume fine tune and channel-volume control fine tune modes. Both volume control settings range from 0dB  $\sim$  -0.375dB and 0.125dB per step. Note that the master volume fine tune is added to the individual channel volume fine tune as the total volume fine tune.

| BIT    | NAME   | DESCRIPTION           | VALUE | FUNCTION |

|--------|--------|-----------------------|-------|----------|

|        |        |                       | 00    | 0dB      |

| D[7:6] |        | Master Volume Fine    | 01    | -0.125dB |

| B[7:6] | MV_FT  | Tune                  | 10    | -0.25dB  |

|        |        |                       | 11    | -0.375dB |

|        |        |                       | 00    | 0dB      |

|        |        | Channel 1 Volume Fine | 01    | -0.125dB |

| B[5:4] | C1V_FT | Tune                  | 10    | -0.25dB  |

|        |        |                       | 11    | -0.375dB |

|        |        |                       | 00    | 0dB      |

| 0.01   | C2V_FT | Channel 2 Volume Fine | 01    | -0.125dB |

| B[3:2] | C2V_F1 | Tune                  | 10    | -0.25dB  |

|        |        |                       | 11    | -0.375dB |

| B[1:0] | Х      | Reserved              |       |          |

## • Address 0X18 : Dynamic Temperature Control (DTC)

AD82585 supports dynamic temperature control. The table describes the setting of DTC.

| BIT    | NAME              | DESCRIPTION    | VALUE | FUNCTION   |

|--------|-------------------|----------------|-------|------------|

| וקום   | DTC_EN DTC Enable |                | 0     | Disable    |

| B[7]   | DIC_EN            | DTC Enable     | 1     | Enable     |

|        |                   |                | 00    | 110 °C     |

| DICICI |                   | DTC Threshold  | 01    | 120 °C     |

| B[6:5] | DTC_TH            | DTC Threshold  | 10    | 130 °C     |

|        |                   |                | 11    | 140 °C     |

|        |                   |                | 00    | 1dB/sec    |

| D[4:2] | DTC Attack and    | DTC Attack and | 01    | 0.5dB/sec  |

| B[4:3] | DTC_RATE          | Release Rate   | 10    | 0.33dB/sec |

|        |                   |                | 11    | 0.25dB/sec |

| B[2:0] | Х                 | Reserved       |       |            |

Release threshold is always 10  $^{\circ}\text{C}$  smaller than attack threshold.

For example:

DTC threshold (attack threshold) =130  $^{\circ}$ C, the release threshold = 120  $^{\circ}$ C.

DTC threshold (attack threshold) =120  $^{\circ}$ C, the release threshold = 110  $^{\circ}$ C.

If junction temperature (Tj) exceeds 130 °C, amplifier gain will be lowered to timing of 1dB/sec. If amplifier gain falls and junction temperature (Tj) turns into less than 130 °C and larger than 120 °C, the gain will not increase or decrease. If amplifier gain falls and junction temperature (Tj) turns into less than 120 °C, amplifier gain will be raised to timing of 1dB/sec.

#### • Address 0X1A : Top 8 Bits of Noise Gate Attack Level

When both left and right signals have 2048 consecutive sample points less than the programmable noise gate attack level, the audio signal will multiply noise gate gain, which can be set at x1/8, x1/4, x1/2, or zero if the noise gate function is enabled. Noise gate attack level is defined by 24-bit representation composed of registers controlled by I2C. The device addresses of noise gate attack level are 0X1A, 0X1B, and 0X1C

| BIT    | NAME       | DESCRIPTION         | VALUE    | FUNCTION        |

|--------|------------|---------------------|----------|-----------------|

|        |            | Top 8 Bits of Noise | Х        | User programmed |

| B[7:0] | NGALT[7:0] | Gate                | 00000000 | 110dD           |

|        |            | Attack Level        | 00000000 | -110dB          |

• Address 0X1B : Middle 8 Bits of Noise Gate Attack Level

| BIT    | NAME       | DESCRIPTION            | VALUE    | FUNCTION        |

|--------|------------|------------------------|----------|-----------------|

| B[7:0] | NGALM[7:0] | Middle 8 Bits of Noise | Х        | User programmed |

|        |            | Gate Attack Level      | 00000000 | -110dB          |

• Address 0X1C : Bottom 8 Bits of Noise Gate Attack Level

| BIT      | NAME       | DESCRIPTION            | VALUE    | FUNCTION        |

|----------|------------|------------------------|----------|-----------------|

| B[7:0] N | NGALB[7:0] | Bottom 8 Bits of Noise | Х        | User programmed |

|          |            | Gate Attack Level      | 00011010 | -110dB          |

#### • Address 0X1D : Top 8 Bits of noise Gate Release Level

After entering the noise gating status, the noise gain will be removed whenever AD82585 receives any input signal that is more than the noise gate release level. Noise gate release level is defined by 24-bit representation composed of registers controlled by I2C. The device addresses of noise gate release level are 0X1D, 0X1E, and 0X1F.

| BIT    | NAME       | DESCRIPTION         | VALUE   | FUNCTION        |

|--------|------------|---------------------|---------|-----------------|

|        |            | Top 8 Bits of Noise | Х       | User programmed |

| B[7:0] | NGRLT[7:0] | Gate                | 0000000 |                 |

|        |            | Release Level       | 0000000 | -100dB          |

• Address 0X1E : Middle 8 Bits of Noise Fate Release Level

| BIT    | NAME       | DESCRIPTION            | VALUE    | FUNCTION        |

|--------|------------|------------------------|----------|-----------------|

| B[7:0] | NGRLM[7:0] | Middle 8 Bits of Noise | Х        | User programmed |

|        |            | Gate Release Level     | 00000000 | -100dB          |

• Address 0X1F : Bottom 8 Bits of Noise Gate Release Level

| BIT    | NAME       | DESCRIPTION            | VALUE    | FUNCTION        |

|--------|------------|------------------------|----------|-----------------|

| B[7:0] | NGRLB[7:0] | Bottom 8 Bits of Noise | Х        | User programmed |

|        |            | Gate Release Level     | 01010011 | -100dB          |

The following table shows the noise gate attack and release threshold level's numerical representation.

| Sami | ole Calculation | for Noise  | Eate Attack | and Release Level |  |

|------|-----------------|------------|-------------|-------------------|--|

| Jani |                 | 101 110130 |             |                   |  |

| Input amplitude | Lincor                 | Desimal     | Hex           |

|-----------------|------------------------|-------------|---------------|

| (dB)            | Linear                 | Decimal     | (1.23 format) |

| 0               | 1                      | 8388607     | 7FFFF         |

| -100            | 10 <sup>-5</sup>       | 83          | 53            |

| -110            | 10 <sup>-5.5</sup>     | 26          | 1A            |

| X               | L=10 <sup>(x/20)</sup> | D=8388607xL | H=dec2hex(D)  |

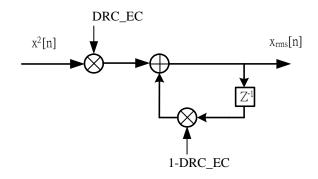

## • Address 0X20 : Top 8 Bits of DRC Energy Coefficient

| BIT    | NAME          | DESCRIPTION        | VALUE    | FUNCTION        |

|--------|---------------|--------------------|----------|-----------------|

| B[7:0] | DRC_ECT [7:0] | Top 8 Bits of DRC  | Х        | User programmed |

|        |               | Energy Coefficient | 00000000 | 1/256           |

#### • Address 0X21 : Bottom 8 Bits of DRC Energy Coefficient

| BIT    | NAME    | DESCRIPTION          | VALUE    | FUNCTION        |

|--------|---------|----------------------|----------|-----------------|

| B[7:0] | DRC_ECB | Bottom 8 Bits of DRC | Х        | User programmed |

|        | [7:0]   | Energy Coefficient   | 00010000 | 1/256           |

The above figure illustrates the digital processing of calculating RMS signal power. In this processing, a DRC energy coefficient is required, which can be programmed for different frequency range. Energy coefficient is defined by 16-bit representation composed of registers controlled by I2C. The device addresses of DRC energy coefficient are 0X20, and 0X21. The following table shows the DRC energy coefficient numerical representation.

| Cample Calculation for Dive Energy Coefficient |       |                        |          |               |  |  |

|------------------------------------------------|-------|------------------------|----------|---------------|--|--|

| DRC energy                                     | dB    | Linear                 | Decimal  | Hex           |  |  |

| coefficient                                    |       |                        |          | (1.15 format) |  |  |

| 1                                              | 0     | 1                      | 4095     | FFF           |  |  |

| 1/256                                          | -48.2 | 1/256                  | 16       | 10            |  |  |

| 1/1024                                         | -60.2 | 1/1024                 | 4        | 4             |  |  |

| L                                              | x     | L=10 <sup>(x/20)</sup> | D=4095xL | H=dec2hex(D)  |  |  |

Address 0X22 : Top 8 Bits of Release Threshold for Dynamic Range Control (DRC) After AD82585 has reached the attack threshold, its output power will be limited to that level. The output power level will be gradually adjusted to the programmable release threshold level. Release threshold is defined by 21-bit representation composed of registers controlled by I2C. The device addresses of release threshold are 0X22, 0X23, and 0X24.

| BIT            | NAME     | DESCRIPTION           | VALUE    | FUNCTION        |

|----------------|----------|-----------------------|----------|-----------------|

| B[7:5]         | Х        | Reserved              |          |                 |

| B[4:0] RTT[4:0 |          | Top 5 Bits of Release | Х        | User programmed |

|                | KTT[4.0] | Threshold             | 00000010 | -6dB            |

• Address 0X23 : Middle 8 Bits of Release Threshold

| BIT           | NAME     | DESCRIPTION       | VALUE    | FUNCTION        |

|---------------|----------|-------------------|----------|-----------------|

| B[7:0] RTM[7: |          | Middle 8 Bits of  | Х        | User programmed |

|               | KTM[7.0] | Release Threshold | 00000000 | -6dB            |

• Address 0X24 : Bottom 8 Tits of Release Threshold

| BIT    | NAME     | DESCRIPTION       | VALUE    | FUNCTION        |

|--------|----------|-------------------|----------|-----------------|

| B[7:0] |          | Bottom 8 Bits of  | Х        | User programmed |

|        | RTB[7:0] | Release Threshold | 00000000 | -6dB            |

The following table shows the attack and release threshold's numerical representation.

| Dowor          | ٩D | Linear                 | Desimal    | Hex           |

|----------------|----|------------------------|------------|---------------|

| Power          | dB |                        | Decimal    | (2.19 format) |

| (PVDD^2)/R     | 0  | 1                      | 524288     | 80000         |

| (PVDD^2)/2R    | -3 | 0.5                    | 262144     | 40000         |

| (PVDD^2)/4R    | -6 | 0.25                   | 131072     | 20000         |

| ((PVDD^2)/R)*L | х  | L=10 <sup>(x/10)</sup> | D=524288xL | H=dec2hex(D)  |

Sample Calculation for Attack and Release Threshold

To best illustrate the dynamic range control function, please refer to the following figure.

## Package Dimensions

## • E-LQFP 48L (7x7mm)

| Crumb al | Dimension in mm |      |  |

|----------|-----------------|------|--|

| Symbol   | Min             | Max  |  |

| А        |                 | 1.60 |  |

| A1       | 0.05            | 0.15 |  |

| b        | 0.17            | 0.27 |  |

| С        | 0.09            | 0.20 |  |

| D        | 6.90            | 7.10 |  |

| D1       | 8.90            | 9.10 |  |

| E        | 6.90            | 7.10 |  |

| E1       | 8.90            | 9.10 |  |

| е        | 0.50 BSC        |      |  |

| L        | 0.45            | 0.75 |  |

Exposed pad

|    | Dimension in mm |      |  |

|----|-----------------|------|--|

|    | Min             | Max  |  |

| D2 | 4.31            | 5.21 |  |

| E2 | 4.31            | 5.21 |  |

## **Revision History**

| Revision | Date       | Description                                                                                                                                                              |

|----------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0.1      | 2012.08    | Original                                                                                                                                                                 |

| 0.2      | 2013.01    | <ol> <li>Fade-out and fade-in time formula revised.</li> <li>Adding DTC explanation at address 0X18.</li> <li>Modifying the description of Available Package.</li> </ol> |

| 1.0      | 2015.03.10 | Revise version to 1.0                                                                                                                                                    |

| 1.1      | 2016.06.29 | Add packing code in ordering information table                                                                                                                           |

| 1.2      | 2016.08.12 | <ol> <li>Modify ordering information</li> <li>Add product ID : AD82585-LG48NAR</li> </ol>                                                                                |

| 1.3      | 2016.08.25 | <ol> <li>Update address 0X02, register table B[4] content.</li> <li>Modify the description of Address 0X02.</li> </ol>                                                   |

| 1.4      | 2017.07.31 | Update power off sequence.                                                                                                                                               |

| 1.5      | 2018.05.18 | <ol> <li>Modify the description of Address 0x02</li> <li>Update the table of Address 0x02</li> </ol>                                                                     |

# **Important Notice**

All rights reserved.

No part of this document may be reproduced or duplicated in any form or by any means without the prior permission of ESMT.

The contents contained in this document are believed to be accurate at the time of publication. ESMT assumes no responsibility for any error in this document, and reserves the right to change the products or specification in this document without notice.

The information contained herein is presented only as a guide or examples for the application of our products. No responsibility is assumed by ESMT for any infringement of patents, copyrights, or other intellectual property rights of third parties which may result from its use. No license, either express, implied or otherwise, is granted under any patents, copyrights or other intellectual property rights of ESMT or others.

Any semiconductor devices may have inherently a certain rate of failure. To minimize risks associated with customer's application, adequate design and operating safeguards against injury, damage, or loss from such failure, should be provided by the customer when making application designs.

ESMT's products are not authorized for use in critical applications such as, but not limited to, life support devices or system, where failure or abnormal operation may directly affect human lives or cause physical injury or property damage. If products described here are to be used for such kinds of application, purchaser must do its own quality assurance testing appropriate to such applications.