OBSOLETE

## ANALOG DEVICES

# CMOS 16-Bit Voltage Out DAC\*

## AD7546

### FEATURES

Monotonic to 16 Bits Over Temperature On-Chip Deglitch Switch Unipolar and Bipolar Operation Microprocessor Compatible TTL/CMOS Compatible Latched Inputs Voltage Output (Constant Output Impedance) Low Cost

Low Power Consumption: 50mW typ

### **GENERAL DESCRIPTION**

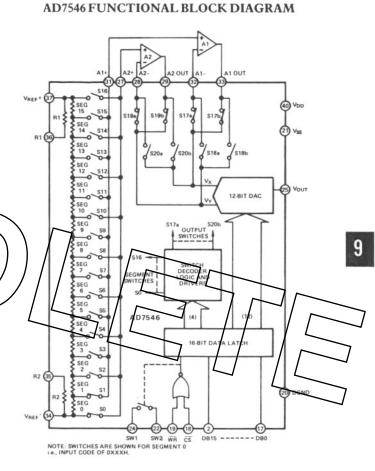

The AD7546 is a 16-bit voltage-output DAC with input data latches for interfacing to 16-bit microprocessors. It uses a novel design consisting of a 12-bit R-2R DAC, operated in the voltage switching mode, which is supplied with a reference voltage from a 4-bit segment DAC under the control of the four most significant bits. A monolithic CMOS device, the AD7546 offers outstanding differential nonlinearity specifications and monotonicity from 14 to 16 bits.

An on-chip deglitch switch which is synchronized with the latch loading signal is provided for use with track/hold circuits.

### ORDERING INFORMATION

|                      |                              | Temperature           | Range - Package           |                    |

|----------------------|------------------------------|-----------------------|---------------------------|--------------------|

| Relative<br>Accuracy | Differential<br>Nonlinearity | Plastic<br>0 to +70°C | Ceramic<br>-25°C to +85°C | Monotonic<br>Range |

| ±0.05%               | ±0.006%                      | AD7546JN              | AD7546AD Q                | 14 Bits            |

| ±0.012%              | ±0.0015%                     | AD7546KN              | AD7546BØ Q                | 16 Bits            |

### PACKAGE IDENTIFICATION<sup>1</sup>

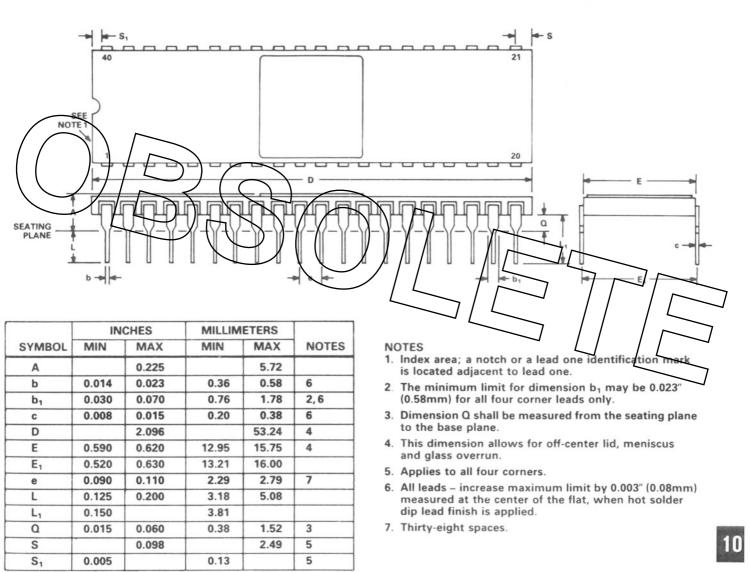

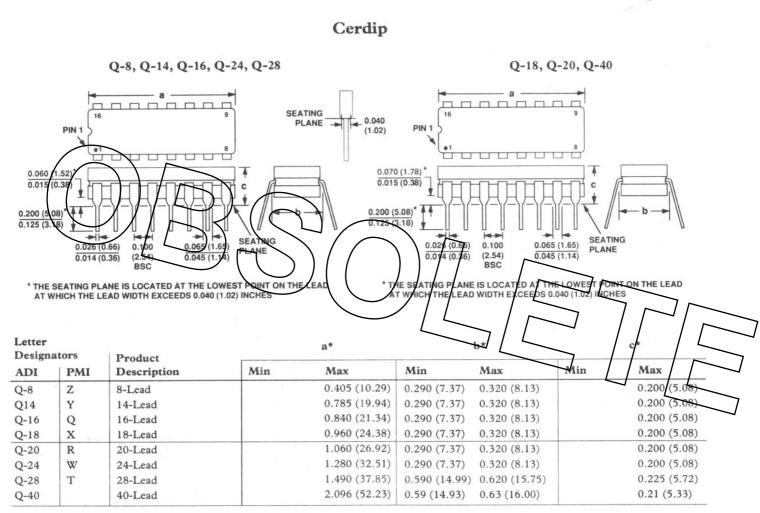

Suffix "D": - Ceramic DIP (D40A) Suffix "N": - Plastic DIP - (N40A)

<sup>1</sup>See Section 19 for package outline information.

### PIN CONFIGURATION

**SPECIFICATIONS** (VDD = +15V, VSS = -5V, (VREF+ = +4V, VREF- = -4V, A1, A2 = AD544K, unless otherwise noted)

| Parameter                                                  | Limit at<br>$T_A = +25^{\circ}C$ | Limit at<br>T <sub>A</sub> = T <sub>min</sub> , T <sub>max</sub> <sup>1</sup> | Units                              | Conditions/Comments                                                  |

|------------------------------------------------------------|----------------------------------|-------------------------------------------------------------------------------|------------------------------------|----------------------------------------------------------------------|

| ACCURACY                                                   |                                  |                                                                               |                                    |                                                                      |

| Resolution                                                 |                                  |                                                                               |                                    |                                                                      |

| All Grades                                                 | 16                               | 16                                                                            | Bits                               |                                                                      |

|                                                            | 10                               | 10                                                                            | 5105                               |                                                                      |

| Relative Accuracy                                          | ±0.05                            | ±0.05                                                                         | % FSR max <sup>2</sup>             | This is an end-point linearity specification                         |

| AD7546JN, AD                                               | ±0.012                           | ±0.012                                                                        | % FSR max                          | assuming zero offset voltage for A1, A2.                             |

| AD7546KN, BD                                               | 10.012                           | 10.012                                                                        | 76 FSR max                         | assuming zero oriser vortage for mit, ma                             |

| Differential Nonlinearity                                  | 10.007                           | +0.006                                                                        | % FSR max                          | Guaranteed monotonic to 14 bits (DB0 and DB1 = 0                     |

| AD7546JN, AD                                               | ±0.006                           | ±0.006                                                                        |                                    | Guaranteed monotonic to 16 bits over temperature.                    |

| AD7546KN, BD                                               | ±0.0015                          | ±0.0015                                                                       | % FSR max                          | Guaranteeu monotonie to 10 bits over temperature.                    |

| Gain Error <sup>3</sup>                                    |                                  |                                                                               |                                    | DAGLAR I I I I I DEPER                                               |

| Positive Full Scale                                        | -0.02                            | -0.02                                                                         | % FSR max                          | DAC latches loaded with FFFF <sub>H</sub>                            |

| Negative Full Scale                                        | -0.02                            | -0.02                                                                         | % FSR max                          | DAC latches loaded with 0000 <sub>H</sub>                            |

| Gain T.C. <sup>4,5</sup>                                   | ±2                               | ±2                                                                            | ppm of FS/°C max                   |                                                                      |

| dc Supply Rejection <sup>5</sup>                           |                                  |                                                                               |                                    |                                                                      |

| $\Delta Gain / \Delta V_{DD}$                              | 100                              | 100                                                                           | μV per V typ                       | $V_{DD} = +14.5V$ to $+15.5V$                                        |

| DYNAMIC PERFORMANCE                                        |                                  |                                                                               |                                    |                                                                      |

| Voltage Settling Time <sup>5</sup> , <sup>6</sup>          | 4                                | 4                                                                             | μs typ                             | To 0.01% of final value.                                             |

| voltage setting time ,                                     | 5                                | 5                                                                             | μs typ                             | To 0.003% of final value.                                            |

| $\frown$                                                   | 10                               | 10                                                                            |                                    | To 0.00076% of final value. Measured using the                       |

| $\langle \frown \rangle \land$                             | 10                               | 10                                                                            | μs typ                             | circuit of Figure 6.                                                 |

| ( ) ) ( )                                                  |                                  |                                                                               |                                    |                                                                      |

| SWITCHING CHARACTERISTICS                                  | *                                |                                                                               |                                    | With +5V input logic levels.                                         |

| tows                                                       |                                  | 0                                                                             | ns min                             | Chip select to WRITE setup time                                      |

| tcwn                                                       |                                  | 8                                                                             | ns min                             | Chip select to WRITE hold time                                       |

| twR                                                        | 400                              | 600                                                                           | ns min                             | WRITE pulse width                                                    |

|                                                            | 200                              | 300                                                                           | ns min                             | Data setup time                                                      |

| t <sub>DH</sub>                                            | 100                              | 150                                                                           | ns min                             | Data hold time                                                       |

| REFERENCE INPUTS                                           | $/ 1 \rightarrow$                | $\rightarrow$ / / $\rightarrow$                                               |                                    | N                                                                    |

| $\sim$                                                     |                                  |                                                                               |                                    |                                                                      |

| Resistance                                                 | 20/22/50                         | 2012210                                                                       | 11 min/min/max                     | Typical Resistance TC is =300ppm/°C                                  |

| $V_{REF}^+$ to $V_{REF}^-$                                 | 20/32/50                         | 20/32/50                                                                      | kΩ, min/typ/max<br>kΩ, min/typ/max | Typical Resistance IC is Stoppin/ C                                  |

| R1, R2                                                     | 20/30/50                         | 20/30/50                                                                      | ksz, min/typ/max                   |                                                                      |

| R1, R2 Match                                               | 2012                             | $\sim$                                                                        |                                    |                                                                      |

| AD7546JN, AD                                               | 0.5                              | 0.5                                                                           | % max                              | Typical TC of R1, R7 match is ±1ppm/°C                               |

| AD7546 KN, BD                                              | 0.1                              | 0.1                                                                           | % max                              |                                                                      |

| Voltage Range                                              |                                  |                                                                               |                                    |                                                                      |

| V <sub>REF</sub> <sup>+</sup>                              | +5                               | +5                                                                            | V max                              | The AD7546 is tested with $V_{REF}^+$ =                              |

| V <sub>REF</sub> <sup>-</sup>                              | -5                               | -5                                                                            | V max                              | $+4V, V_{REF}^{-} = -4V$                                             |

| ANALOG OUTPUT                                              |                                  |                                                                               |                                    |                                                                      |

| ROUT (Output Resistance)                                   | 10/15/25                         | 10/15/25                                                                      | kΩ, min/typ/max                    |                                                                      |

| C <sub>OUT</sub> (Output Resistance) <sup>5</sup>          | 8                                | 8                                                                             | pF max                             |                                                                      |

|                                                            | 0                                | 0                                                                             | pr max                             |                                                                      |

| DEGLITCH SWITCH                                            |                                  |                                                                               |                                    |                                                                      |

| RON                                                        | 300/600                          | 450/900                                                                       | Ω typ/max                          | $V_{SW} = \pm 4V, I_{SW} = 100 \mu A$                                |

| ILEAKAGE, SW2 (pin 22)                                     | 1                                | 10                                                                            | nA max                             | Off switch leakage. $V_{SW1} = \pm 4V$ , $V_{SW2} = \mp 4V$ .        |

| LOGIC INPUTS                                               |                                  |                                                                               |                                    |                                                                      |

| VIH                                                        | 2.4                              | 2.4                                                                           | V min                              |                                                                      |

|                                                            | 0.8                              | 0.8                                                                           | V max                              |                                                                      |

| V <sub>IL</sub><br>I <sub>IN</sub> (Input Leakage Current) | 1                                | 1                                                                             |                                    | Ver = 0V or Ve =                                                     |

|                                                            |                                  | 8                                                                             | μA max                             | $V_{IN} = 0V \text{ or } V_{DD}$                                     |

| C <sub>IN</sub> (Input Capacitance) <sup>5</sup>           | 8<br>16 Rie Unional              | 10000                                                                         | pF max                             | See Einer 7                                                          |

| Input Coding                                               | 16-Bit Unipol:<br>16-Bit Offset  |                                                                               |                                    | See Figure 7<br>See Figure 8                                         |

| DOWED CUDDLY                                               | to bit offset                    |                                                                               |                                    | occ righte o                                                         |

| POWER SUPPLY                                               | . 1.5                            | .15                                                                           | N/                                 | +5% for an official performance                                      |

| V <sub>DD</sub>                                            | +15                              | +15                                                                           | V                                  | ±5% for specified performance                                        |

| Vss                                                        | -5                               | -5                                                                            | v                                  | ±5% for specified performance                                        |

| IDD                                                        | 4                                | 4                                                                             | mA max                             | $V_{IN} = V_{IL} \text{ or } V_{IH}$                                 |

| lDD                                                        | 200                              | 200                                                                           | μA max                             | $V_{IN} = 0V \text{ or } V_{DD}, \overline{CS} = \overline{WR} = 0V$ |

| ·UU                                                        | 100                              | 100                                                                           | P                                  |                                                                      |

NOTES

<sup>1</sup> Temperature ranges as follows: AD7546JN, KN; 0 to +70°C

AD7546AD, BD; -25°C to +85°C

<sup>2</sup> FSR is Full Scale Range.

<sup>a</sup> These gain error specifications have assumed an input offset voltage for A2 of 0V. Actual gain error figures should include amplifier A2 input offset voltage.

<sup>a</sup> Gain TC specifications have assumed a zero input offset voltage drift with temperature for A2. Actual gain TC figures should include amplifier A2 drift with temperature.

Guaranteed but not tested.

Voltage settling time will be a function of the time constant RC seen at the buffer amplifier inputs. The resistance component of

Voltage setting time will be a function of the constant KC seen at the outrer amplifier inputs. The resistance component of this time constant is the equivalent output impedance of the resistor string and will vary depending on which segment is decoded. Maximum equivalent resistance occurs at mid-scale. Worst case settling thus occurs from zero to mid-scale or from full-scale to mid-scale. \*15V logic can be used to reduce power dissipation but no improvement is achieved in the timing specifications. All control signals are measured with  $t_{\rm F} = t_{\rm F} = 20$ ns for +5V logic and timed from  $\frac{(V_{\rm IH} + V_{\rm IL})}{2}$ . Data is timed from  $V_{\rm IH}$  or  $V_{\rm IL}$ . Sample tested at  $12^{10}$  cm. +25°C to ensure conformance. 2

Specifications subject to change without notice.

### CAUTION:

ESD (Electro-Static-Discharge) sensitive device. The digital control inputs are zener protected; however, permanent damage may occur on unconnected devices subject to high energy electrostatic fields. Unused devices must be stored in conductive foam or shunts. The protective foam should be discharged to the destination socket before devices are removed.

### ABSOLUTE MAXIMUM RATINGS

| $(T_A)$ | = +25° | С | unless | otherwise | noted) |  |

|---------|--------|---|--------|-----------|--------|--|

|         |        |   |        |           |        |  |

| (Note  | that | cavity | lid | on | Ceramic | Package | 1S | Electrically | Con- |

|--------|------|--------|-----|----|---------|---------|----|--------------|------|

| nected | to V | (nn)   |     |    |         |         |    |              |      |

|        |      | DD'    |     |    |         |         |    |              |      |

| $V_{\text{DD}}$ (Pin 40) to DCND $OV + 17V$                               |

|---------------------------------------------------------------------------|

| V <sub>DD</sub> (Pin 40) to DGND 0V, +17V                                 |

| V <sub>SS</sub> (Pin 21) to DGND0V, -7V                                   |

| $V_{REF}^+$ (Pin 37) to DGND $V_{DD}$ , $V_{REF}^-$                       |

| $V_{REF}$ <sup>-</sup> (Pin 34) to DGND $V_{SS}$ , $V_{REF}$ <sup>+</sup> |

| R1 (Pin 36) to DGND±25V                                                   |

| R2 (Pin 35) to DGND±25V<br>*DB12 LØW (S1) S19 Closed)                     |

| *DB12 LOW (S17 S19 Closed)                                                |

| A1 - (Pin 32) dr A1 (Qut (Pin 33))                                        |

| to A2 - (Pin 28) or A2 Out (Pin 29)0.3V, +5V                              |

| *DB12 HIGH (\$18, \$20 Closed)                                            |

| A2 (Pin 28) or A2 Out (Pin 19)                                            |

| to A1 - (Pin 32) or A1 Out (Pin 32)0.3V, +5V                              |

| A1 + (Pin 31), A2 + (Pin 27) to DGVD (). VS\$, VDD                        |

| $V_{OUT}$ (Pin 25) to DGND $\pm 25V$                                      |

| SW1 (Pin 24), SW2 (Pin 22) to DGND $V_{SS}$ $V_{DS}$                      |

|                                                                           |

| Digital Inputs (Pins 2 -19) to D | G | N | D |   | • |  |   |   |   | -( | 0.3V, +17V |

|----------------------------------|---|---|---|---|---|--|---|---|---|----|------------|

| Power Dissipation (Package)      |   |   |   |   |   |  |   |   |   |    |            |

| Plastic (AD7546JN, KN)           |   |   |   |   |   |  |   |   |   |    |            |

| Up to +50°C                      |   |   |   |   |   |  |   |   |   |    | 1200mW     |

| Derates above +50°C by           |   |   |   |   |   |  |   |   |   |    | . 12mW/°C  |

| Ceramic (AD7546AD, BD)           |   |   |   |   |   |  |   |   |   |    |            |

| Up to +50°C                      |   |   |   |   |   |  | • |   | • | •  | 1000mW     |

| Derates above +50°C by           |   |   |   | • | • |  |   | • | · | •  | . 10mW/°C  |

\*The absolute maximum rating refers to the voltage VX-VY across the inputs of the 12-bit DAC. See Functional Diagram of Figure 2.

### STRESS

Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or at any other condition above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### ACCURACY SPECIFICATIONS

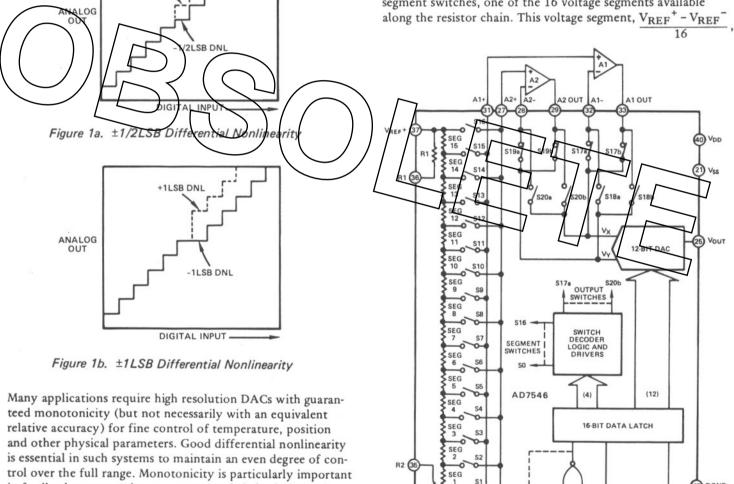

Two types of nonlinearity errors exist in D/A converters, relative accuracy and differential nonlinearity. Relative accuracy is the error resulting from departure of the DAC transfer characteristic from the ideal straight line drawn between measured zero and measured full scale.

Differential Nonlinearity (DNL) is the difference between the measured output voltage change between two adjacent input codes and the ideal change of 1LSB. A specified DNL of ±1 LSB guarantees monotonicity (i.e. the output voltage will never decrease for any increase in input code). To ensure that the output voltage will always increase when the input code is increased requires a DNL specification of less than ±1LSB. This point is illustrated in Figure 1.

+1/2LSB DNL

### **THEORY OF OPERATION OF THE AD7546**

The traditional solution to achieving high resolution DACs with guaranteed monotonicity is the R-2R ladder approach. This technique usually constrains the converter to have ±1/2LSB nonlinearity in order to guarantee monotonicity, which in turn requires very tight resistor matching and tracking. The resistor ladder tolerance is most critical for the major carry where, in a 16-bit DAC, the 15LSBs turn off and the most significant bit turns on. If the MSB is more than 0.0015% low, the converter will be nonmonotonic. Table I shows the maximum tracking error which can be allowed over a 60°C range to maintain monotonicity, which is ±1LSB DNL. A standard R-2R approach therefore imposes severe constraints on resistor matching.

The design technique used in the AD7546 sidesteps the penalty inherent in the R-2R design (i.e. that tight differential nonlinearity figures require tight nonlinearity figures). The block diagram of the AD7546 is shown in Figure 2. The top four bits of the 16-bit input data are decoded to select, via the segment switches, one of the 16 voltage segments available along the resistor chain. This voltage segment, VREF - VREF

in feedback systems where nonmonotonic behavior constitutes positive feedback which may lead to catastrophic results. To ensure monotonic behavior of a particular device, only those bits which are guaranteed monotonic for that grade should be exercised e.g., for the AD7546 IN (14-bit monotonic), DB0 and DB1 should be tied LOW and DB2 - DB15 exercised.

CS

SEG

VREP

SO

24

SW1 SW2 WR C NOTE: SWITCHES ARE SHOWN FOR SEGMENT 0

20 DGND

DB15 ---- DB0

|                               | Initial Matchin | ng Required for: | Tracking Required for:            |                                     |  |  |  |  |

|-------------------------------|-----------------|------------------|-----------------------------------|-------------------------------------|--|--|--|--|

| Converter<br>Type             | ±1LSB DNL       | ±1/2LSB DNL      | ±1LSB DNL<br>(1/2LSB INITIAL DNL) | ±1/2LSB DNL<br>(1/4LSB INITIAL DNL) |  |  |  |  |

| Straight R-2R                 | ±0.0015%        | ±0.00076%        | ±0.127ppm/°C                      | ±0.063ppm/°C                        |  |  |  |  |

| Segmented 4<br>Bits + 12 Bits | ±0.024%         | ±0.012%          | ±2ppm/°C                          | ±1ppm/°C                            |  |  |  |  |

Table I. Resistor Matching Requirements for 16-Bit DAC

is used as a voltage reference to feed a 12-bit R-2R type D/A converter operating in the voltage switching mode (Reference 1). From Figure 2 the reference voltage is the voltage between  $V_X$  and  $V_Y$  and is always equal to one voltage segment. The output of the D/A converter may be expressed as follows:

$$V_{OUT} = V_Y + D(V_X - V_Y)$$

12-bit digital code, V<sub>X</sub> is the higher seg-D is the segment voltage. The 12-bit ent voltage and converter reference inputs, VK and VV, are connected to to resistor chain nodes which define the segment of crest and the 12-bit/D/A converter interpolates between these two points.

Thus the 65,536 output levels available from the 16-bit DAC are composed of 16 groups of 4,096 steps each. Since the major carry of the 12-bit DAC is repeated in each of the segments it requires sixteen times lower initial resistor accuracy and tracking to maintain a given differential nonlinearity over temperature. The resistors that determine monotonicity are in the 12-bit DAC. The truth table for the switch decoder is shown in Table II.

| DB15 | DB14 | DB13 | DB12 | Segment<br>Switches | Output<br>Switches |

|------|------|------|------|---------------------|--------------------|

| 1    | 1    | 1    | 1    | S15, S16            | S18, S20           |

| 1    | 1    | 1    | 0    | S14, S15            | S17, S19           |

| 1    | 1    | 0    | 1    | S13, S14            | S18, S20           |

| 1    | 1    | 0    | 0    | S12, S13            | S17, S19           |

| 1    | 0    | 1    | 1    | S11, S12            | S18, S20           |

| 1    | 0    | 1    | 0    | S10, S11            | S17, S19           |

| 1    | 0    | 0    | 1    | S9, S10             | S18, S20           |

| 1    | 0    | 0    | 0    | S8, S9              | S17, S19           |

| 0    | 1    | 1    | 1    | S7, S8              | S18, S20           |

| 0    | 1    | 1    | 0    | S6, S7              | S17, S19           |

| 0    | 1    | 0    | 1    | S5, S6              | S18, S20           |

| 0    | 1    | 0    | 0    | S4, S5              | S17, S19           |

| 0    | 0    | 1    | 1    | S3, S4              | S18, S20           |

| 0    | 0    | 1    | 0    | S2, S3              | S17, S19           |

| 0    | 0    | 0    | 1    | S1, S2              | S18, S20           |

| 0    | 0    | 0    | 0    | S0, S1              | S17, S19           |

|  | Table II. | Truth | Table | for | Switch | Decoder |

|--|-----------|-------|-------|-----|--------|---------|

|--|-----------|-------|-------|-----|--------|---------|

Since the input impedance of the D/A converter is low and varies with code, two external amplifiers are used to buffer the selected reference segment from the D/A converter. The buffer amplifiers, A1, A2, could give rise to differential nonlinearity if connected directly to  $V_X$  and  $V_Y$  and stepped up the ladder.

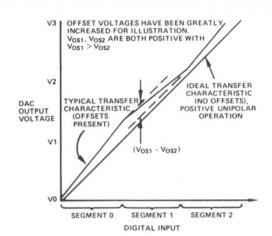

For example consider A1 and A2 to have input offset voltages VOS1 and VOS2 respectively, then the first major carry from segment 0 to segment 1 occurs as follows:

Segment 0:

$$V_X = V_1 + V_{OS1}, V_Y = V_0 + V_{OS2}$$

$V_{OUT} = V_0 + V_{OS2} + (1 - 1/2^{12})$

$[(V_1 + V_{OS1}) - (V_0 + V_{OS2})]$

$V_{OUT} = V_1 + V_{OS1} - \frac{(V_1 - V_0)}{2^{12}} - \frac{(V_{OS1} - V_{OS2})}{2^{12}}$

Segment 1:  $V_X = V_2 + V_{OS1}, V_Y = V_1 + V_{OS2}$

$V_{OUT} = V_1 + V_{OS2}$

The error term generated by this segment change is:

$$V_{OS2} - V_{OS1} + \frac{(V_{OS1} - V_{OS2})}{2^{12}}$$

$$V_{052} - V_{051} = \frac{212}{212}$$

It can be seen that  $V_{051}$  and  $V_{052}$  must match to within one

LSB to guarantee monotonic behavior at this transition To overcome this problem the AD7\$46 circuit interchange the amplifiers at each segment transition and, as a result differential nonlinearity can be guaranteed for a very large range of VOS. Switching inside the feedback loop of the op amp is used to remove the effect of switch RON. With this technique the first major carry from segment 0 to segment 1 now occurs as follows:

Segment 0:

$$V_{X} = V_{1} + V_{OS1}, V_{Y} = V_{0} + V_{OS2}$$

$$V_{OUT} = V_{1} + V_{OS1} - \frac{(V_{1} - V_{0})}{212} - \frac{(V_{OS1} - V_{OS2})}{212}$$

Segment 1: Interchange amplifiers

$$V_X = V_2 + V_{OS2}, V_Y = V_1 + V_{OS1}$$

$$V_{OUT} = V_1 + V_{OS1}$$

The error term at the transition from one segment to another is now  $(V_{OS1} - V_{OS2})/4096$  which gives very good differential nonlinearity for reasonable offsets. At the next segment transition,  $V_X = V_3 + V_{OS1}$ ,  $V_Y = V_2 + V_{OS2}$  and so on through each segment. The amplifiers are interchanged via output switches S17 - S20, see Table II.

In the segmented DAC the precision of the resistor chain determines integral nonlinearity only. If the resistor chain is trimmed for perfect matching such that Vn + 1 = Vn = Vn - 1 =Vsegment, then the resulting nonlinearity due to amplifier offset voltage corresponds to a gain error in adjacent segments of VOS1 - VOS2, see Figure 3. This term may be nulled to zero with offset adjustment of one op amp.

This adjustment is facilitated by tying VREF+ and VREFto ground, tying DB0 through DB11 and DB13 through DB15 to digital ground and toggling DB12. The AD7546 output (V<sub>OUT</sub>, pin 25) will have a square wave at the toggling frequency with an amplitude of VOS1 - VOS2. This can be adjusted to zero as mentioned.

Figure 3. Positive Unipolar Transfer Characteristic  $(V_{REF}^{-} = 0V, V_{REF}^{+} = +4V)$  Exaggerated to Show the Effect of Amplifier Offset Voltages

If offsets are equal in magnitude and sign, the result is a constant offset shift in the D/A transfer function and the device will have true 16-bit linearity.

For Differential Nonlinearity:

MAX DNL (in LSBs)

$$=\frac{14}{16} \cdot \frac{(I_{BLAS})(R)}{1LSB}$$

For Relative Accuracy:

MAX NL (in LSBs)

$$=\frac{15}{2} \cdot \frac{(I_{BLAS})(R)}{1LSB}$$

Where  $I_{BIAS}$  = Input bias current for the noninverting input terminal of A1 or A2 in amps 1LSB =  $\frac{V_{REF} + - V_{REF} -}{2N}$  volts

N is determined by the required system resolution up to N = 16.

R = R segment, typically  $2k\Omega$

Low bias current op amps, BIFET or Super-Beta types, should be used such as the AD542K, AD544K, AD517K, TL071, TL081. Table III lists some important parameters against various op amps. Note that the AD7546 output settling time is dependent upon the op amps used. The figures in column two give the additional offset voltage contribution to nonlinearity of A1 and A2.

|                             | Maximum<br>Additional | Settling Time (μs)<br>to ±1/2LSB |         |  |  |  |  |

|-----------------------------|-----------------------|----------------------------------|---------|--|--|--|--|

| A1, A2                      | Nonlinearity          | 14 Bits                          | 16 Bits |  |  |  |  |

| 2 X AD544KH<br>1 X TL072BCP | ±0.01%                | 15                               | 35      |  |  |  |  |

| (Dual)                      | ±0.05%                | 5                                | 10      |  |  |  |  |

| 2 X AD517JH<br>1 X AD644JH  | ±0.003%               | 90                               | 100     |  |  |  |  |

| (Dual AD544)                | ±0.01%                | 15                               | 35      |  |  |  |  |

| 2 X LF256                   | ±0.05%                | 5                                | 10      |  |  |  |  |

Settling time measurements were made with a similar op amp to buffer  $V_{OUT}$  (A4 in Figure 8)

Table III. AD7546 Performance vs. A1, A2

### DATA LOADING AND DEGLITCH SWITCH

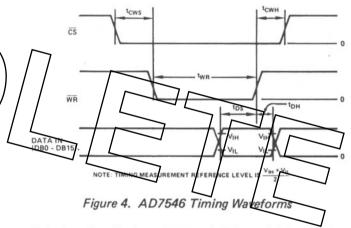

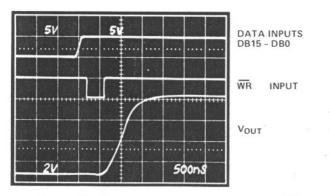

The AD7546 timing specifications are included on Specifications page and illustrated here in Figure 4. Signals  $\overline{CS}$  and  $\overline{WR}$  have the same interpretation as in normal microprocessor systems. When both  $\overline{CS}$  and  $\overline{WR}$  are low the input latches are transparent and the DAC output voltage follows the input data. With  $\overline{CS}$  low, the input data is latched on the rising edge of  $\overline{WR}$ .

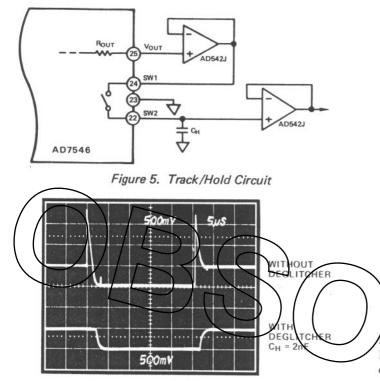

Included on the chip is an SPST switch intended for use in a Track/Hold circuit to remove glitches from the DAC output and simplify low-pass filtering of the reconstructed output voltage. The switch is synchronized with the latch loading signals, being open when both  $\overline{CS}$  and  $\overline{WR}$  inputs are low. The internal logic of the AD7546 ensures that the switch opens before data to the latches can change. To function as a Track/Hold the switch is placed in series with the DAC output as shown in Figure 5. Pin 23 is a no-connect pin which should be grounded to minimize any feedthrough resulting from stray capacitances at the two switch terminals. The switch should be used with pin 24 as the input and pin 22 as the output. When the switch is open the Hold capacitor stores the previous output voltage of the DAC. The WR pulse should be of sufficient duration to allow the DAC to settle to its new analog output and for all glitches to have settled out. Driving the WR input from a one-shot will ensure sufficient settling time.

When WR returns high the switch is closed, updating the output voltage on the capacitor. Typical output waveforms using the circuit of Figure 5 are shown below.

### UNIPOLAR OPERATION

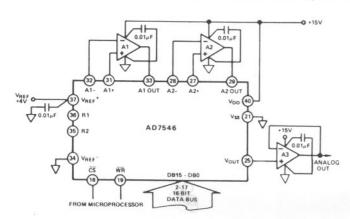

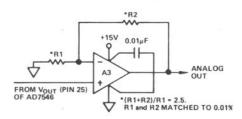

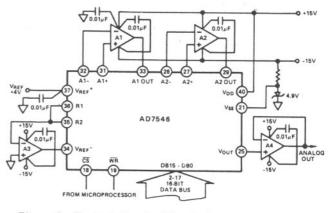

Unipolar (single quadrant) operation is obtained when one end of the resistor chain is tied to ground i.e., when  $V_{REF}$  =  $+V_{REF}$  and  $V_{REF}$  = 0V or when  $V_{REF}$  = 0V and  $V_{REF}$  = -VREF. A typical unipolar circuit configuration for the AD7546 is shown in Figure 6a. In this positive unipolar application V<sub>SS</sub> has been set to 0V and the AD7546 operates as a single supply device. If a full scale output is required which is different from the ideal V<sub>REF</sub> - 1LSB then output amplifier A3 of Figure 6a can be configured to provide the necessary scaling. Figure 6b shows the additional components required to boost the full scale output voltage to +10V with  $V_{REF}$  = +4V. Any full scale gain error (introduced by R1, R2 tolerances) can be trimmed out by adjusting  $V_{REF}$ . Note that R1, R2 should be the same type of resistor (preferably metal film) so that their temperature coefficients match. The transfer characteristic for the circuit of Figure 6a is shown in Figure 7.

Figure 6a. Typical Unipolar Circuit Configuration for the AD7546 (Positive Reference, VREF+ = VREF, VREF- = 0V)

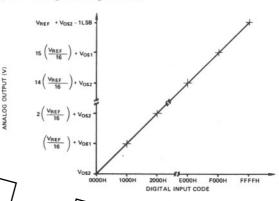

Figure 7. Unipolar Transfer Characteristic of Figure 6a. BIFOLAR OPERATION

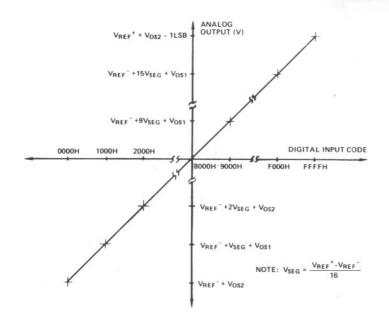

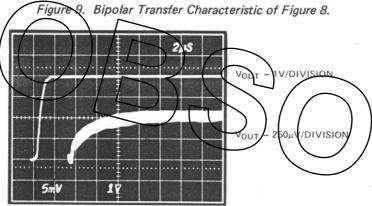

Bipolar (two quadrant) operation is obtained when both ends of the resistor chain are driven with voltage references of opposite polarity. A symmetrical transfer function around 0V is achieved with  $|V_{REF}^+| = |V_{REF}^-|$ . For this case the zero crossing occurs with DB15=1 and DB14 to DB0 all 0s. Figure 8 shows a typical bipolar circuit configuration for the AD7546 to obtain a symmetrical transfer function around 0V. Figure 9 shows the transfer characteristic of Figure 8.

Two equal trimmed resistors, R1 and R2, are included on the AD7546 to allow one reference to be generated from the other with the addition of an external amplifier (A3 in Figure 8). Note that  $V_{REF}^+$  must always be more positive than  $V_{REF}^-$ ; operation is confined to two quadrants (1st and 3rd). It is possible to use an ac reference signal with the AD7546 as long as  $V_{REF}^+$  always remains more positive than  $V_{REF}^-$ .

Figure 8. Typical Bipolar Circuit Configuration for the AD7546

Figure 10. Typical Settling Characteristics of Figure 8 Using TL071 for Full Scale Code Change

Figure 11. Typical Loading Waveforms with  $\overline{CS} = OV$

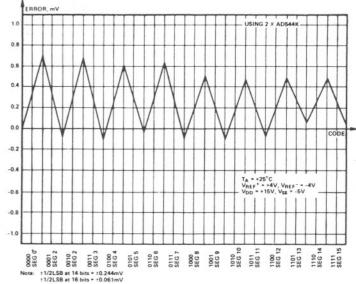

Figure 12a. Typical Error vs Input Code with A1 = A2 = AD544K

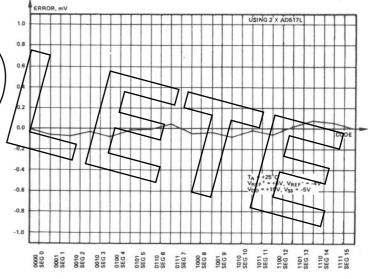

Figure 12b. Typical Error vs Input Code with A1 = A2 = AD517L

D-40 40-Lead Side Brazed Ceramic DIP

\*For complete package dimensions see reference manual or data sheet.