# **General Description**

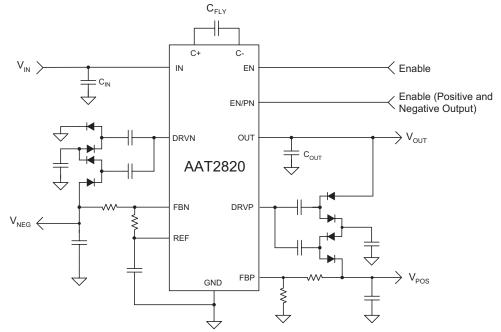

The AAT2820 is a member of AnalogicTech's Total Power Management IC<sup>TM</sup> (TPMIC<sup>TM</sup>) product family. It is a triple output charge pump targeted for active matrix thin-film transistor (TFT), liquid crystal displays (LCDs), and CCD camera bias for systems operating with lithium-ion/polymer batteries. The device generates three regulated output voltages for turn-on gate drive bias (V<sub>POS</sub>), turn-off gate voltage bias (V<sub>NEG</sub>), and logic voltage.

The V<sub>POS</sub> and V<sub>NEG</sub> output voltages are independently regulated. Both outputs use external diode and capacitor multiplier stages (as many stages as required) to regulate output voltages up to +25V and -25V. An additional regulated output voltage is provided for biasing the display module. Built-in soft-start circuitry prevents excessive inrush current during start-up. A high switching frequency enables the use of very small external capacitors. A low shutdown feature disconnects the load from V<sub>IN</sub> and reduces quiescent current to less than 0.1 $\mu$ A.

The AAT2820 is available in a Pb-free TDFN44-16 package and is specified over the -40°C to +85°C operating temperature range.

#### **Features**

# **ChargePump**<sup>™</sup>

- V<sub>IN</sub> Range: 2.7V to 5.5V

- 5V Regulated Output Voltage

- Two Adjustable Regulated Output Voltages:

V<sub>POS</sub> and V<sub>NEG</sub>

- Positive Charge Pump Up to +25V

- Negative Charge Pump Down to -25V

- Optional Power-Up Sequence with AAT2820-1

- Internal Power MOSFETs

- <1µA of Shutdown Current</p>

- Internally Controlled Soft Start

- Fast Transient Response

- Ultra-Thin Solution (No Inductors)

- 16-Pin TDFN44 Package

- Temperature Range: -40°C to +85°C

# Applications

- CCD Cameras

- Hand-Held Instruments

- Passive-Matrix Displays

- Personal Digital Assistants (PDAs)

- TFT Active-Matrix LCDs

# **Typical Application**

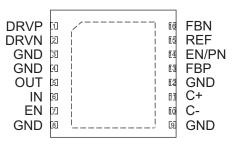

# **Pin Description**

| Pin #          | Symbol | Function                                                                                          |

|----------------|--------|---------------------------------------------------------------------------------------------------|

| 1              | DVRP   | Positive charge pump driver output. Output high level is V <sub>SUPP</sub> and low level is PGND. |

| 2              | DRVN   | Negative charge pump driver output. Output high level is $V_{SUPN}$ and low level is PGND.        |

| 3, 4, 8, 9, 12 | GND    | Ground connection.                                                                                |

| 5              | OUT    | Regulated 5V output. Requires a 4.7µF bypass capacitor to ground.                                 |

| 6              | IN     | Input power supply. A 1 $\mu$ A capacitor should be connected between this pin and ground.        |

| 7              | EN     | Enable input control pin. When low, the device is powered down and consumes less than             |

|                |        | 0.1µA. This pin should not be left floating.                                                      |

| 10             | C-     | Flying capacitor negative terminal.                                                               |

| 11             | C+     | Flying capacitor positive terminal. Connect a 1µF capacitor between C+ and C                      |

| 13             | FBP    | Positive charge pump feedback input. Regulates to 1.2V nominal. Connect feedback                  |

|                |        | resistive divider to analog ground (GND).                                                         |

| 14             | EN/PN  | Enable input. When EN/PN is pulled low, $V_{POS}$ and $V_{NEG}$ are turned off.                   |

| 15             | REF    | Internal reference bypass terminal. Connect a 0.1µF capacitor from this terminal to ana-          |

|                |        | log ground (GND). External load capability to 50uA. REF is disabled in shutdown.                  |

| 16             | FBN    | Negative charge pump regulator feedback input. Regulates to 0V nominal. Connect feed-             |

|                |        | back resistive divider to the reference (REF).                                                    |

| EP             |        | Exposed paddle (bottom); connect to GND directly beneath package.                                 |

# **Pin Configuration**

#### TDFN44-16 (Top View)

# Absolute Maximum Ratings<sup>1</sup>

| Symbol            | Description                                      | Value                             | Units |  |

|-------------------|--------------------------------------------------|-----------------------------------|-------|--|

| V <sub>IN</sub>   | Input Voltage                                    | -0.3 to 6.0                       | V     |  |

| V <sub>OUT</sub>  | Charge Pump Output                               | -0.3 to 6.0                       | V     |  |

| V <sub>EN</sub>   | EN or EN/PN to GND                               | -0.3 to 6.0                       | V     |  |

| V <sub>N CH</sub> | DRVN to GND                                      | -0.3V to (V <sub>IN</sub> + 0.3V) | V     |  |

| V <sub>P CH</sub> | DRVP to GND                                      | -0.3V to (V <sub>IN</sub> + 0.3V) | V     |  |

| Other Inputs      | REF, FBN, FBP to GND                             | -0.3V to (V <sub>IN</sub> + 0.3V) | V     |  |

| I                 | Continuous Current into DRVN, DRVP, OUT          | ±200                              | mA    |  |

| I <sub>MAX</sub>  | All Other Pins                                   | ±10                               | IIIA  |  |

| T <sub>LEAD</sub> | Maximum Soldering Temperature (at leads, 10 sec) | 300                               | °C    |  |

# **Thermal Information**<sup>2</sup>

| Symbol          | Description                    | Value | Units |

|-----------------|--------------------------------|-------|-------|

| θ <sub>JA</sub> | Maximum Thermal Resistance     | 50    | °C/W  |

| P <sub>D</sub>  | Power Dissipation <sup>3</sup> | 2.0   | W     |

<sup>1.</sup> Stresses above those listed in Absolute Maximum Ratings may cause permanent damage to the device. Functional operation at conditions other than the operating conditions specified is not implied. Only one Absolute Maximum Rating should be applied at any one time.

<sup>2.</sup> Mounted on an FR4 board.

<sup>3.</sup> Derate 6.25mW/°C above 25°C.

# **Electrical Characteristics**<sup>1</sup>

$V_{IN}$  = 3.3V;  $C_{IN}$  =  $C_{OUT}$  =  $C_{FLY}$  = 1.0µF,  $T_A$  = 0°C to +85°C, unless otherwise noted. Typical values are  $T_A$  = 25°C.

| Symbol              | Description                                  | Conditions                                                                              | Min  | Тур  | Max  | Units    |

|---------------------|----------------------------------------------|-----------------------------------------------------------------------------------------|------|------|------|----------|

| V <sub>IN</sub>     | Input Supply Range                           |                                                                                         | 2.7  |      | 5.5  | V        |

| UVLO                | Input Under-Voltage Lockout                  | V <sub>IN</sub> Rising                                                                  |      | 1.8  |      |          |

| UVLO                | Threshold                                    | V <sub>IN</sub> Falling                                                                 |      | 1.6  |      | V        |

| I <sub>CC</sub>     | Operating Current                            | $V_{FBP}$ = 1.5V, $V_{FBN}$ = -0.2V, No Load on<br>DRVN and DRVP; EN = EN/PN = $V_{IN}$ |      | 5.0  |      | mA       |

| I <sub>SD</sub>     | Shutdown Supply Current                      | $V_{\rm EN} = V_{\rm EN/PN} = 0V$                                                       |      | 0.1  | 1.0  | μA       |

| T <sub>SS</sub>     | Soft-Start Time                              |                                                                                         |      | 200  |      | μs       |

| F <sub>osc</sub>    | Operating Frequency                          |                                                                                         |      | 1.0  |      | MHz      |

|                     | Low-Power Charge Pump                        |                                                                                         |      |      | 1    |          |

| V <sub>FBN</sub>    | FBN Regulation Voltage                       |                                                                                         | -100 | 0    | +100 | mV       |

| I <sub>FBN</sub>    | FBN Input Bias Current                       | V <sub>FBN</sub> = -50mV                                                                | -100 |      | +100 | nA       |

| I <sub>NEG</sub>    | Maximum Negative Output Current <sup>2</sup> | $3.3 \le V_{IN} \le 5.5$ ; No Load at $V_{POS}$ and $V_{OUT}$                           |      |      | 25   | mA       |

| R <sub>DS_NCH</sub> | DRVN NCH On-Resistance                       |                                                                                         |      | 1.5  | 5.0  | Ω        |

|                     | MIN DRVN PCH On-Resistance                   | V <sub>FBN</sub> = 100mV, V <sub>IN</sub> = 4V                                          |      | 1.0  | 5.0  | Ω        |

| $R_{DS_PCH}$        | MAX DRVN PCH On-Resistance                   | $V_{\text{FBN}} = -100 \text{mV}, V_{\text{IN}} = 4 \text{V}$                           |      | 20   |      | kΩ       |

| Positive L          | ow-Power Charge Pump                         |                                                                                         |      | -    |      |          |

| V <sub>FBP</sub>    | FBP Regulation Voltage                       |                                                                                         | 1.15 | 1.2  | 1.25 | V        |

| I <sub>FBP</sub>    | FBP Input Bias Current                       | V <sub>FBP</sub> = 1.5V                                                                 | -60  |      | +100 | nA       |

| I <sub>POS</sub>    | Maximum Positive Output Current <sup>2</sup> | $3.3 \le V_{IN} \le 5.5$ ; No Load at $V_{NEG}$ and $V_{OUT}$                           |      |      | 25   | mA       |

| R <sub>DS_PCH</sub> | DRVP PCH On-Resistance                       |                                                                                         |      | 1.0  | 5.0  | Ω        |

|                     | MIN DRVP NCH On-Resistance                   | V <sub>FBP</sub> = 1.15V, V <sub>IN</sub> = 4V                                          |      | 3    | 15   | Ω        |

| R <sub>DS_NCH</sub> | MAX DRVP NCH On-Resistance                   | $V_{\text{FBP}} = 1.25\text{V}, V_{\text{IN}} = 4\text{V}$                              |      | 20   |      | kΩ       |

| Reference           |                                              |                                                                                         |      |      |      |          |

|                     | Reference Voltage                            | -2.0μA < Ι <sub>REF</sub> < 50μA                                                        | 1.18 | 1.2  | 1.22 |          |

| $V_{REF}$           | Reference Under-Voltage Lockout<br>Threshold | V <sub>REF</sub> Rising                                                                 |      | 0.8  |      | V        |

| V <sub>EN(L)</sub>  | EN and EN/PN Threshold Low                   |                                                                                         |      |      | 0.5  | V        |

| V <sub>EN(H)</sub>  | EN and EN/PN Threshold High                  |                                                                                         | 1.5  |      |      | V        |

|                     | Enable Input Current                         |                                                                                         | -1.0 |      | 1.0  | μA       |

| T <sub>SD</sub>     | Over-Temperature Shutdown<br>Threshold       |                                                                                         |      | 140  |      | °C       |

| T <sub>HYS</sub>    | Over-Temperature Shutdown<br>Hysteresis      |                                                                                         |      | 15   |      | °C       |

| Regulated           | 1 5V Charge Pump                             | 1                                                                                       |      | l    | I    | ·        |

| -                   | Output Voltage Tolerance                     | 2.7V < V <sub>IN</sub> < 5V, I <sub>OUT</sub> = 50mA                                    |      | ±4.0 |      | %        |

| V <sub>OUT</sub>    | Output Voltage                               | $3.0V < V_{IN} < 5V, I_{OUT} = 100 \text{mA}$                                           | 4.8  | 5.0  | 5.2  | V        |

|                     |                                              |                                                                                         |      |      |      | <u> </u> |

<sup>1.</sup> The AAT2820 is guaranteed to meet performance specifications from 0°C to 70°C. Specification over the -40°C to +85°C operating temperature range is assured by design, characterization, and correlation with statistical process controls.

<sup>2.</sup> Loads greater than those listed in maximum output load conditions may cause permanent damage to the device.

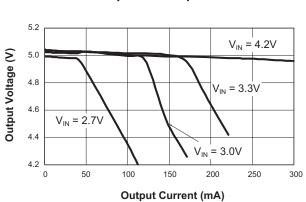

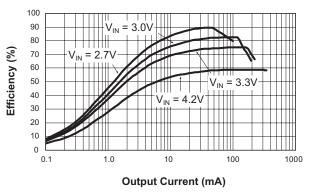

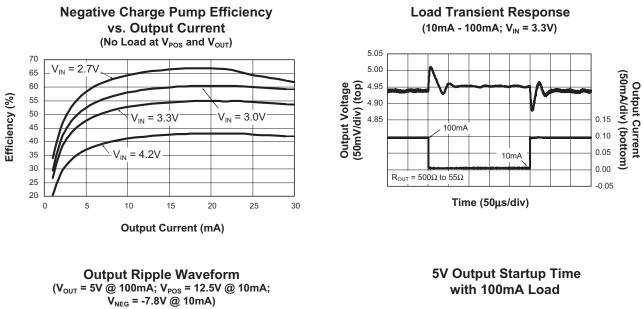

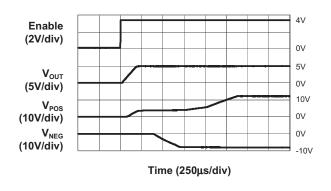

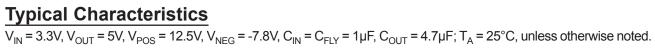

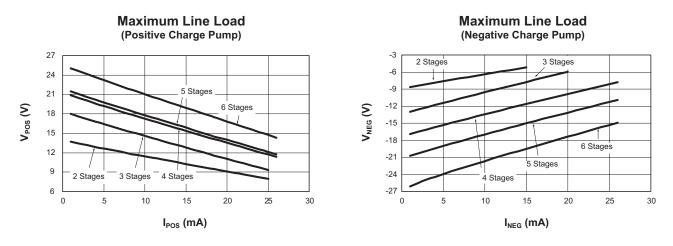

# **Typical Characteristics**

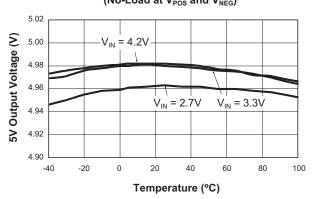

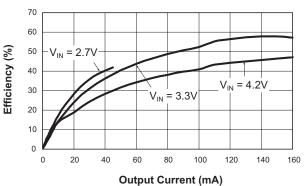

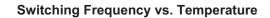

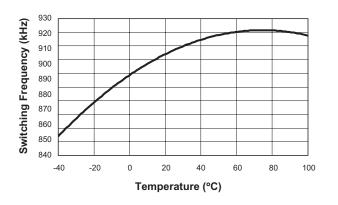

$V_{IN} = 3.3V, V_{OUT} = 5V, V_{POS} = 12.5V, V_{NEG} = -7.8V, C_{IN} = C_{FLY} = 1\mu$ F,  $C_{OUT} = 4.7\mu$ F;  $T_A = 25^{\circ}$ C, unless otherwise noted.

5V Output vs. Output Current

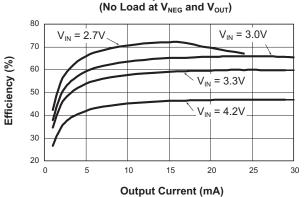

5V Output Efficiency vs. Output Current (No-Load at V<sub>POS</sub> and V<sub>NEG</sub>)

5V Output Efficiency vs. Output Current ( $V_{OUT}$  = 5V;  $V_{POS}$  = 12.5V @ 10mA;  $V_{NEG}$  = -7.8V @ 5mA)

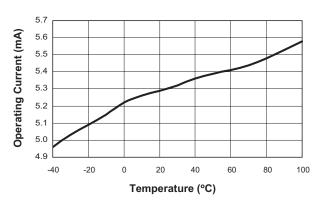

**Operating Current vs. Temperature**

2820.2006.04.1.4

### **Typical Characteristics**

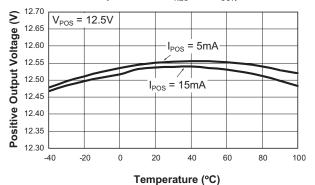

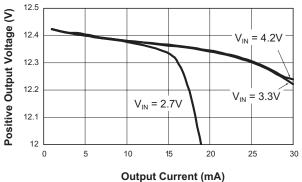

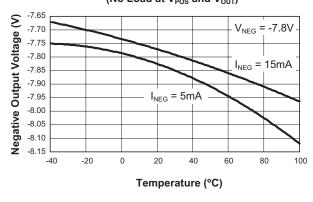

Positive Charge Pump Output Voltage vs. Temperature (No Load at V<sub>NEG</sub> and V<sub>OUT</sub>)

Positive Charge Pump Efficiency vs. Output Current

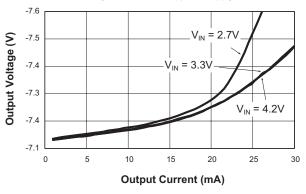

# **Typical Characteristics**

$V_{IN} = 3.3V, V_{OUT} = 5V, V_{POS} = 12.5V, V_{NEG} = -7.8V, C_{IN} = C_{FLY} = 1\mu F, C_{OUT} = 4.7\mu F; T_A = 25^{\circ}C, unless otherwise noted.$

$V_{\text{NEG}} = -7.8V @ 10\text{mA})$

Time (250ns/div)

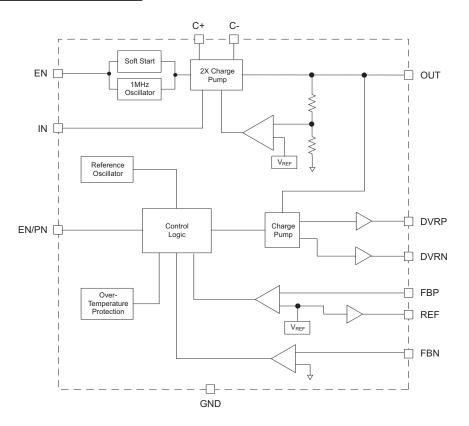

# **Functional Block Diagram**

# **Functional Description**

#### **5V Regulated Output**

The main power supply is a charge pump doubler architecture used to support the high-current demand required by the application. Charge pump regulation is achieved by sensing the output voltage through an internal resistor divider network. A switch doubling circuit is enabled when the divided output drops below a preset trip point controlled by an internal comparator. The free-running charge pump switching frequency is approximately 1MHz. The charge pump is designed to deliver 150mA of continuous current (loads greater than the maximum load condition may cause permanent damage to the device).

#### **Dual Charge Pump Regulators**

The dual charge pump provides low-power regulated output voltages from two individual charge

pumps. Using a single stage, the first charge pump inverts the supply voltage ( $V_{\rm IN}$ ) and provides a regulated negative output voltage. The second charge pump doubles  $V_{\rm IN}$  and provides a regulated positive output voltage. These outputs use external Schottky diodes and capacitor multiplier stages (as many as required) to regulate up to ±25V. A constant switching frequency of 1MHz minimizes the output ripple and capacitor size.

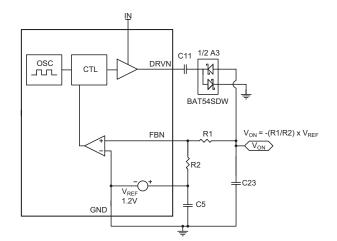

### **Negative Charge Pump Regulator**

During the first half-cycle, the P-channel MOSFET turns on and the flying capacitor C11 charges to  $V_{\rm IN}$  minus a diode drop (Figure 1). During the second half-cycle, the P-channel MOSFET turns off and the N-channel MOSFET turns on, level shifting C11. This connects C11 in parallel with the output reservoir capacitor C23. If the voltage across C23 minus a diode drop is less than the voltage across C11, current flows from C11 to C23 until the diode turns off.

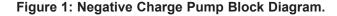

#### **Positive Charge Pump Regulator**

During the first half-cycle, the N-channel MOSFET turns on and charges the flying capacitor C12 (Figure 2). During the second half-cycle, the Nchannel MOSFET turns off and the P-channel MOSFET turns on, level shifting C12 the input voltage. This connects C12 in parallel with the reservoir capacitor C24. If the voltage across C24 plus a diode drop is less than the level shifted by the flying capacitor (C12 + V<sub>IN</sub>), charge is transferred from C12 to C24 until the diode turns off. If the positive charge pump output is connected to ground, output may not recover until power is recycled. Loads greater than the maximum load condition may cause permanent damage to the device; please review the Maximum Line Load Curves and the Electrical Characteristics table.

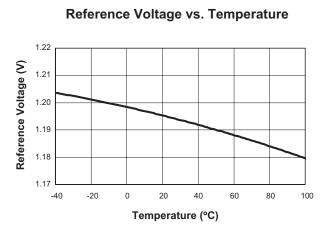

#### **Voltage Reference**

The voltage reference is a simple band gap with an output voltage equal to  $V_{BE}$  + K\*V<sub>T</sub>. The band gap reference amplifier has an additional compensation capacitor from the negative input to the output. This capacitor serves to slow down the circuit during startup and soft starts the voltage reference and the regulator output from overshoot. The reference circuit amplifier also increases the overall PSRR of the device. An 80k $\Omega$  resistor serves to isolate and buffer the amplifier from a small internal filter capacitor and an optional large external filter capacitor.

#### Enable

In the normal operating state, the AAT2820 typically consumes 5mA of quiescent operating current. By pulling the enable pin (EN) low, the AAT2820 disables all three outputs. Once the device is shut down, the supply current drops to less than  $1\mu$ A to maximize battery life.

The AAT2820 gives the application an option to independently turn on/off the positive and negative charge pump outputs. These two outputs can be disabled by pulling the EN/PN pin low. The threshold levels lie between 0.5V and 1.5V. Depending on the application, the supplies must be sequenced properly to avoid damage or latch-up.

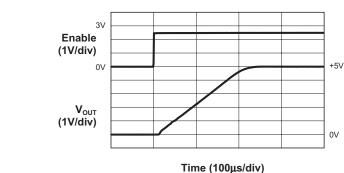

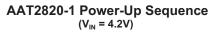

#### Soft-Start and Start-up Sequence

The AAT2820 has an internal soft-start circuit to guarantee a smooth transition to 5V for the main output when the device is enabled (typical 200µs). This device has two versions for the start-up sequence. The AAT2820 ramps up the positive charge pump after the negative charge pump is present; the AAT2820-1 ramps up the positive charge pump before the negative charge pump.

#### **Over-Temperature Protection**

To protect the AAT2820, as well as the system application, this device has a thermal protection circuit that will shut down all the charge pumps if the die temperature rises above the preset internal thermal limit. This protects the device if the ambient temperature exceeds the operating limit for the device.

Figure 2: Postive Charge Pump Block Diagram.

# Design Procedure and Component Selection

#### Number of Stages for Dual Charge Pump Regulators

The number of stages required can be determined by:

$$N_{POS} = \frac{V_{POS} - 5}{5 - 2V_{FWD}}$$

for the positive output, and

$$N_{\text{NEG}} = \frac{V_{\text{NEG}}}{2V_{\text{FWD}} - 5}$$

for the negative output.

Where,

V<sub>NEG</sub> = Negative output voltage

V<sub>POS</sub> = Positive output voltage

$V_{FWD}$  = Forward voltage drop of the Schottky diode (0.31V, based on BAT54SDW diode when  $I_F$  = 4mA)

After solving for the number of stages ( $N_{POS}$  and  $N_{NEG}$ ), round up the solutions to the next highest integers for the number of stages required.

Tables 1 and 2 show the number of stages required for positive and negative charge pumps, respectively.

| V <sub>POS</sub> (V) | # of Stages (n) |

|----------------------|-----------------|

| 7                    | 1               |

| 8                    | 1               |

| 9                    | 1               |

| 10                   | 2               |

| 11                   | 2               |

| 12                   | 2               |

| 13                   | 2               |

| 14                   | 3               |

| 15                   | 3               |

| 16                   | 3               |

| 17                   | 3               |

| 18                   | 3               |

| 19                   | 4               |

| 20                   | 4               |

| 21                   | 4               |

| 22                   | 4               |

| 23                   | 5               |

| 24                   | 5               |

| 25                   | 5               |

#### Table 1: Number of Stages Required for Positive Charge Pump.

| V <sub>NEG</sub> (V) | # of Stages (n) |

|----------------------|-----------------|

| -7                   | 2               |

| -8                   | 2               |

| -9                   | 3               |

| -10                  | 3               |

| -11                  | 3               |

| -12                  | 3               |

| -13                  | 3               |

| -14                  | 4               |

| -15                  | 4               |

| -16                  | 4               |

| -17                  | 4               |

| -18                  | 5               |

| -19                  | 5               |

| -20                  | 5               |

| -21                  | 5               |

| -22                  | 6               |

| -23                  | 6               |

| -24                  | 6               |

| -25                  | 6               |

Table 2: Number of Stages Required forNegative Charge Pump.

### $V_{NEG}$

The negative output voltage is adjusted by a resistive divider from the output ( $V_{NEG}$ ) to the FBN and REF pin. The maximum reference voltage current is 50µA; therefore, the minimum allowable value for R2 of Figure 1 is 24k $\Omega$ . It is best to select the smallest value possible for R2 as this will keep R1 to a minimum. This limits errors due to the FBN input bias current. The FBN input has a maximum input bias current of 100nA. Using the full 50µA reference current for programming  $V_{NEG}$ :

$$I_{PGM} = \frac{V_{REF}}{R2} = \frac{1.2V}{24k\Omega} = 50\mu A$$

will limit the error due to the input bias current at FBN to less than 0.2%.

$$\frac{I_{FBN}}{I_{PGM}} = \frac{0.1 \mu A}{50 \mu A} = 0.2\%$$

With R2 selected, R1 can be determined by:

$$R1 = \frac{V_{\text{NEG}} \cdot R2}{-V_{\text{RFF}}}$$

See the example in Table 3.

| V <sub>NEG</sub> (V) | R1, Closest Value (k $\Omega$ ) |

|----------------------|---------------------------------|

| -7                   | 143                             |

| -8                   | 162                             |

| -9                   | 182                             |

| -10                  | 205                             |

| -11                  | 226                             |

| -12                  | 243                             |

| -13                  | 267                             |

| -14                  | 287                             |

| -15                  | 309                             |

| -16                  | 324                             |

| -17                  | 348                             |

| -18                  | 360                             |

| -19                  | 390                             |

| -20                  | 412                             |

| -21                  | 430                             |

| -22                  | 453                             |

| -23                  | 470                             |

| -24                  | 487                             |

| -25                  | 510                             |

Table 3: Closest Value for R1 if Using 24.3k $\Omega$  as R2.

#### V<sub>POS</sub>

The positive output voltage is set by way of a resistive divider from the output (V<sub>POS</sub>) to the FBP and ground pin. Limiting the size of R3 reduces the effect of the FBP bias current. For less than 0.1% error, limit R3 to less than 12k $\Omega$ .

$$I_{PGM} = \frac{V_{REF}}{R3} = \frac{1.2V}{12k\Omega} = 100\mu A$$

$$\frac{I_{FBN}}{I_{PGM}} = \frac{0.1\mu A}{100\mu A} = 0.1\%$$

Once R3 has been determined, then solve for R4 (see example in Table 4).

$$R4 = R3 \cdot \left(\frac{V_{POS}}{V_{REF}} - 1\right)$$

| V <sub>POS</sub> (V) | R4, Closest Value (k $\Omega$ ) |

|----------------------|---------------------------------|

| 7                    | 59.0                            |

| 8                    | 69.8                            |

| 9                    | 78.7                            |

| 10                   | 88.7                            |

| 11                   | 100.0                           |

| 12                   | 110.0                           |

| 13                   | 120.0                           |

| 14                   | 130.0                           |

| 15                   | 140.0                           |

| 16                   | 150.0                           |

| 17                   | 160.0                           |

| 18                   | 169.0                           |

| 19                   | 180.0                           |

| 20                   | 191.0                           |

| 21                   | 200.0                           |

| 22                   | 210.0                           |

| 23                   | 220.0                           |

| 24                   | 232.0                           |

| 25                   | 240.0                           |

Table 4: Closest Value for R4 if Using 12.1kΩ as R3.

#### **Capacitor Selection**

Careful selection of the three external capacitors  $C_{IN}$ ,  $C_{FLY}$ , and  $C_{OUT}$  is important because they will affect turn-on time, output ripple, efficiency, and load transient response. Optimum performance will be obtained when low equivalent series resistance (ESR) ceramic capacitors are used. In general, low ESR may be defined as less than 100m $\Omega$ . A value of 1µF for input and flying capacitors is a good starting point when designing with the AAT2820. This not only provides for a very small printed circuit board area, but cost is further reduced by the minimized bill of materials.

#### **Input Capacitor**

A 1 $\mu$ F multilayer ceramic chip capacitor is suggested for the input. This capacitor should be connected between the IN pin and ground; 1 $\mu$ F should be suitable for most applications. Even though the AAT2820 switching ripple and noise are very low, back-injected line noise may be further reduced by increasing the value of  $C_{\rm IN}$ . A low equivalent series inductance (ESL) ceramic capacitor is ideal for this function. The size required will vary depending on the load, output voltage, and input voltage characteristics. Other types of capacitors may be used for  $C_{\rm IN}$  at the cost of compromised circuit performance.

#### **Output Capacitor**

The output capacitor ( $C_{OUT}$ ) should be connected between the OUT pin and ground. Switching noise and ripple seen on the charge pump output increases with load current. Typically, the output capacitor should be 5 to 10 times greater than the flying capacitor. To minimize stray inductance, the capacitor should be placed as closely as possible to the IC. This keeps the high frequency content of the input current localized, minimizing radiated and conducted EMI.

A 1µF ceramic capacitor is recommended for most applications for optimum transient response. However, if the application has a larger load from the main and multiplier stage charge pump outputs, a 4.7µF ceramic capacitor is suggested to reduce the feedback injection noise from the multiplier stage and lower switching ripple. Capacitor types other than ceramic capacitors can be used for  $C_{OUT}$ . However, capacitors composed of non-ceramic material will typically have a greater value of ESR, resulting in increased output switching ripple.

### Charge Pump Capacitor (C<sub>FLY</sub>)

Due to the switching operation of the voltage doubling circuit topology, current flow through the flying capacitor is bi-directional. The flying capacitor selected must be a non-polarized type. A  $1\mu$ F low ESR ceramic capacitor is ideal for most applications.

#### **Capacitor Characteristics**

Ceramic composition capacitors are highly recommended over all other types of capacitors for use with the AAT2820. Ceramic capacitors offer many advantages over their tantalum and aluminum electrolytic counterparts. A ceramic capacitor typically has very low ESR, is lowest cost, has a smaller

PCB footprint, and is non-polarized. Low ESR ceramic capacitors help maximize charge pump transient response. Since ceramic capacitors are non-polarized, they are not prone to incorrect connection damage.

#### **Rectifier Diodes**

For the rectifiers, use Schottky diodes with a voltage rating of 1.5X the input voltage. The maximum steady-state voltage seen by the rectifier diodes for both the positive and negative charge pumps (regardless of the number of stages) is:

$$V_{RESERVE} = V_{IN} - V_F$$

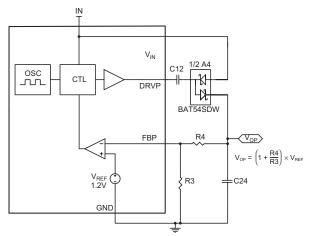

The BAT54SDW quad Schottky in an SOT363 (2x2mm) package is a good choice for multiplestage charge pump configuration (see evaluation board schematic in Figure 3).

C18, C19, C28, C29 Taiyo Yuden TMK212 BJ105KG 1 $\mu$ F 25V X5R 0805 [Optional] C4 Taiyo Yuden LMK212 BJ105KD 1 $\mu$ F 10V X7R 0805

Figure 3: AAT2820 Evaluation Board Schematic (Shown With Six Stages).

# Flying and Output Capacitor Multiplier Stages

A 0.1 $\mu$ F X7R or X5R ceramic capacitor is typically used. The voltage rating of the flying and reservoir output capacitors will vary with the number of charge pump stages. The reservoir output capacitor should be roughly 10X the flying capacitor. Use larger capacitors for reduced output ripple. A 1 $\mu$ F X7R or X5R type ceramic is typically used.

# Positive Charge Pump Capacitor Voltage Ratings

The absolute steady-state maximum output voltage (neglecting the internal  $R_{DS(ON)}$  drop of the internal MOSFETs) for the nth stage is:

$$V_{\text{BULK}(n)} = (n + 1) \cdot V_{\text{IN}} - 2 \cdot n \cdot V_{\text{FWD}}$$

where  $V_{FWD}$  is the estimated forward drop of the Schottky diode. This is also the voltage rating required for the nth bulk capacitor in the positive output charge pump.

The voltage rating for the nth flying capacitor in the positive stage is:

$$V_{FLY(n)} = V_{BULK(n+1)} - V_{FWD}$$

where  $V_{BULK(0)}$  is the input voltage (see Table 5).

| # of Stages (n) | V <sub>BULK(n)</sub> | V <sub>FLY(n)</sub> |  |

|-----------------|----------------------|---------------------|--|

| 1               | 9.4V                 | 4.7V                |  |

| 2               | 13.8V                | 9.1V                |  |

| 3               | 18.2V                | 13.5V               |  |

| 4               | 22.6V                | 17.9V               |  |

| 5               | 27.0V                | 22.3V               |  |

| 6               | 31.4V                | 26.7V               |  |

Table 5: Positive Charge Pump CapacitorVoltages (V<sub>FWD</sub> = 0.31V).

# Negative Charge Pump Capacitor Voltage Ratings

The absolute steady-state maximum output voltage (neglecting the internal  $R_{DS(ON)}$  drop of the internal MOSFETs) for the nth stage is:

$$V_{\text{BULK}(n)} = -n \cdot V_{\text{IN}} + 2 \cdot n \cdot V_{\text{FWD}}$$

This is also the voltage rating required for the nth bulk capacitor in the negative output charge pump.

The voltage rating for the nth flying capacitor in the negative stage (see Table 6) is:

$$V_{FLY(n)} = V_{FWD} - V_{BULK(n)}$$

| # of Stages (n) | V <sub>BULK(n)</sub> | V <sub>FLY(n)</sub> |

|-----------------|----------------------|---------------------|

| 1               | -4.4V                | 4.7V                |

| 2               | -8.8V                | 9.1V                |

| 3               | -13.2V               | 13.5V               |

| 4               | -17.6V               | 17.9V               |

| 5               | -22.0V               | 22.3V               |

| 6               | -26.4V               | 26.7V               |

Table 6: Negative Charge Pump Capacitor Voltages ( $V_{FWD}$  = 0.31V).

#### **PC Board Layout**

The input and reference capacitor should be placed as closely to the IC as possible. Place the programming resistors (R1-R4) close to the IC, minimizing trace length to FBN and FBP. Place the main charge pump flying capacitor close to the C+ and C- pins, with wide traces and no vias. Place all multiplier stage (charge pump) circuitry to the IC as closely as possible using wide traces, and avoid using vias when possible.

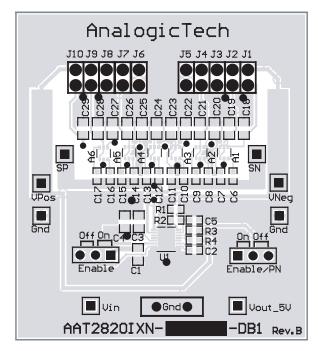

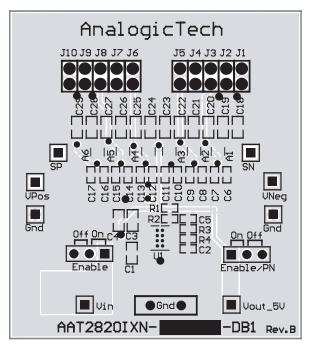

Figures 4 and 5 show the recommended evaluation board layout with the TDFN44-16 package.

Figure 4: AAT2820 Evaluation Board Top Side Layout.

Figure 5: AAT2820 Evaluation Board Bottom Side Layout.

# **Ordering Information**

| Package   | Power-Up Sequence | Marking <sup>1</sup> | Part Number (Tape and Reel) <sup>2</sup> |

|-----------|-------------------|----------------------|------------------------------------------|

| TDFN44-16 | -, +              | OCXYY                | AAT2820IXN-5.0-T1                        |

| TDFN44-16 | +, -              | ODXYY                | AAT2820IXN-5.0-1-T1                      |

All AnalogicTech products are offered in Pb-free packaging. The term "Pb-free" means semiconductor products that are in compliance with current RoHS standards, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. For more information, please visit our website at http://www.analogictech.com/pbfree.

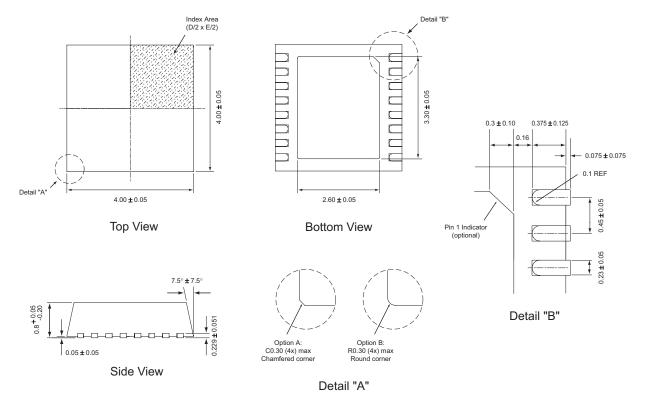

# Package Information

All dimensions in millimeters

<sup>2.</sup> Sample stock is generally held on part numbers listed in BOLD.

© Advanced Analogic Technologies, Inc.

AnalogicTech cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in an AnalogicTech product. No circuit patent licenses, copyrights, mask work rights, or other intellectual property rights are implied. AnalogicTech reserves the right to make changes to their products or specifications or to discontinue any product or service without notice. Customers are advised to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgement, including those pertaining to warranty, patent infringement, and limitation of liability. AnalogicTech warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with AnalogicTech's standard warranty. Testing and other quality control techniques are utilized to the extent AnalogicTech deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed.

AnalogicTech and the AnalogicTech logo are trademarks of Advanced Analogic Technologies Incorporated. All other brand and product names appearing in this document are registered trademarks or trademarks of their respective holders.

Advanced Analogic Technologies, Inc. 830 E. Arques Avenue, Sunnyvale, CA 94085 Phone (408) 737-4600 Fax (408) 737-4611