# Universal asynchronous receiver transmitter 6402 and 6402-1

Stock numbers 309-284 and 304-144

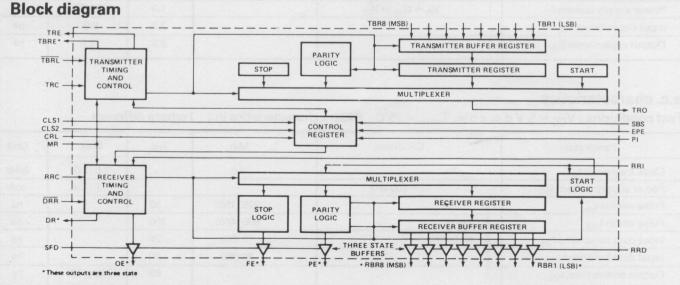

The RS Universal asynchronous receiver transmitters, UARTS are designed for interfacing an asynchronous serial data channel and a parallel data channel. The devices can be used in a wide range of applications including modems, printers, peripherals and remote data acquisition systems.

The transmitter converts parallel data into serial form and automatically adds start, parity and stop bits. The receiver converts serial start, data parity and stop bits to parallel data verifying proper code transmission, parity and stop bits. Utilising CMOS – LSI technology the devices operate at low power levels and can be clocked at frequencies up to 1 MHz (6402) or 2 MHz (6402-1). Several status output flags are provided thereby increasing flexibility and simplifying the user interface.

#### Absolute maximum ratings

| Operating temperature range-          | $-40^{\circ}$ C to $+85^{\circ}$ C  |

|---------------------------------------|-------------------------------------|

| Storage temperature                   | $-65^{\circ}$ C to $+150^{\circ}$ C |

| Supply voltage                        | +7.0 V d.c.                         |

| Voltage on any input or<br>output pin | -0.3 V to V <sub>CC</sub> +0.3 V    |

#### **Features**

- Two speed options up to 1 MHz 6402 or 2 MHz 6402-1

- Low power less than 10 mW at 2 MHz

- Programmable word length, stop bits and parity

- Automatic data formatting and status generation

- CMOS and LS TTL compatible.

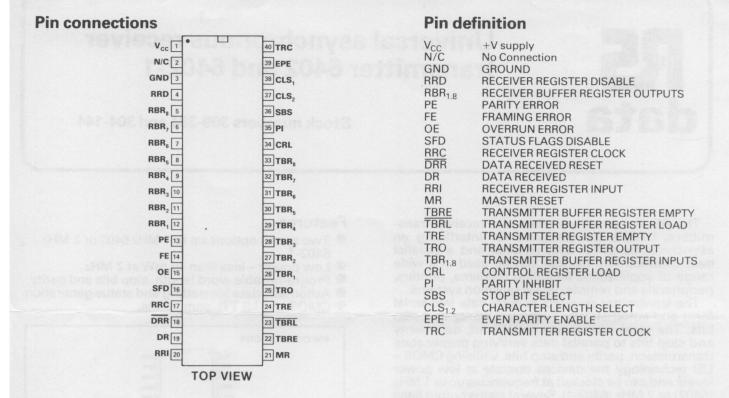

| PIN CONNECTI | 0145                |                     |  |

|--------------|---------------------|---------------------|--|

|              | V <sub>cc</sub> 1 • | 40 TRC              |  |

|              | N/C 2               | 39 EPE              |  |

|              | GND 3               | 38 CLS,             |  |

|              | RRD 4               | 37 CLS <sub>2</sub> |  |

|              | RBR <sub>8</sub> 5  | 36 SBS              |  |

|              | RBR, 6              | 35 PI               |  |

|              | RBR <sub>6</sub> 7  | 34 CRL              |  |

|              | RBR <sub>s</sub> 8  | 33 TBR <sub>8</sub> |  |

|              | RBR <sub>4</sub> 9  | 32 TBR <sub>7</sub> |  |

|              | RBR <sub>3</sub> 10 | 31 TBR <sub>6</sub> |  |

|              | RBR <sub>2</sub> 11 | 30 TBR <sub>5</sub> |  |

|              | RBR, 12             | 29 TBR4             |  |

|              | PE 13               | 28 TBR <sub>3</sub> |  |

|              | FE 14               | 27 TBR <sub>2</sub> |  |

|              | OE 15               | 26 TBR,             |  |

|              | SFD 16              | 25 TRO              |  |

|              | RRC 17              | 24 TRE              |  |

|              | DRR 18              | 23 TBRL             |  |

|              | DR 19               | 22 TBRE             |  |

|              | RRI 20              | 21 MR               |  |

# d.c. characteristics

data

Test conditions:  $V_{CC} = 5 V d.c. \pm 5\%$ ,  $T_{amb} = 25^{\circ}C$  6402-1 characteristics in ( ) where different.

| Parameter                            | Condition                            | Min.                         | Тур.       | Max.      | Unit |

|--------------------------------------|--------------------------------------|------------------------------|------------|-----------|------|

| Input voltage High V <sub>IH</sub>   |                                      | V <sub>CC</sub> - 2.0        | lest liter | 201       | V    |

| Input voltage Low V <sub>IL</sub>    | and a set                            |                              |            | 0.8       | V    |

| Input leakage I <sub>IL</sub>        | $G_{nd} \leq V_{IN} \leq V_{CC}$     | -5.0 (-1)                    | 1          | 5.0 (1)   | μA   |

| Output voltage High V <sub>OH</sub>  | $I_{OH} = -0.2 \text{ mA}$           | 2.4                          |            |           | V    |

| Output voltage Low V <sub>OL</sub>   | I <sub>OL</sub> = 1.6 mA             | And the second               |            | 0.45      | V    |

| Output leakage I <sub>OL</sub>       | $G_{nd} \leq V_{OUT} \leq V_{CC}$    | -5.0 (-1)                    |            | 5.0 (1)   | μΑ   |

| Power supply current I <sub>CC</sub> | $V_{IN} = G_{nd} \text{ or } V_{CC}$ |                              | 1.0        | 800 (100) | μΑ   |

| Input capacitance C <sub>IN</sub>    | a second and a second department     |                              | 7.0        | 8.0       | pF   |

| Output capacitance Co                |                                      | and the second second second | 8.0        | 10.0      | pF   |

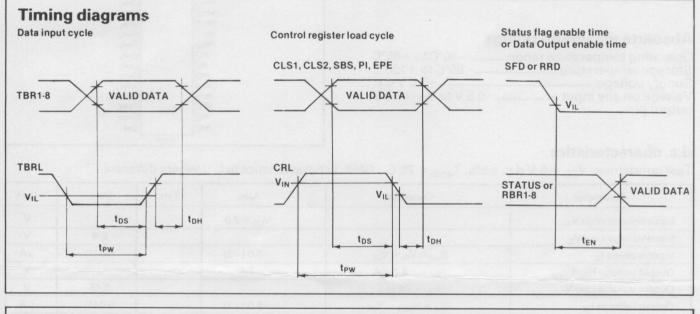

## a.c. characteristics

Test conditions :  $V_{CC} = 5 V d.c. \pm 5\%$ ,  $T_{amb} = 25^{\circ}C$  6402-1 characteristics in ( ) where different.

| Parameter                             | Condition                               | Min.                | Тур. | Max.              | Unit |

|---------------------------------------|-----------------------------------------|---------------------|------|-------------------|------|

| Clock frequency f <sub>c</sub>        |                                         | d.c.                | T    | 1.0 (2.0)         | MHz  |

| Power supply current I <sub>CC</sub>  | $f_c = 500 \text{ kHz}$                 | and a second second |      | 1.2 (1.9)         | mA   |

| Pulse widths t <sub>pw</sub>          |                                         | 225 (150)           | 50   | 1 Martin Partie 1 | ns   |

| Pulse width t <sub>MR</sub>           | see timing                              | 600 (400)           | 200  | Service 18        | ns   |

| Input data setup time t <sub>DS</sub> | diagrams                                | 75 (50)             | 20   |                   | ns   |

| Input data hold time t <sub>DH</sub>  | C Y Y X X Y Y Y Y Y Y Y Y Y Y Y Y Y Y Y | 90 (60)             | 40   |                   | ns   |

| Output enable time t <sub>EN</sub>    |                                         |                     | 80   | 190 (160)         | ns   |

## **Control inputs**

- Receiver register disable a high level on this input forces the receiver RRD holding register outputs RBR1 - RBR8 to a high impedance state thus allowing direct connection in data bus applications. SFD Status flag disable – a high level forces the outputs PE, FE, OE, DR, and TBRE (see status flag description) to a high impedance state. DRR Data received reset - a low level on this input clears Data received output (DR) to a low level thereby permitting the next character to be received without an overrun error. MR Master reset - a high level clears the PE, FE, OE, DR, and TRE status flags and sets the TBRE and TRO outputs high. Eighteen clock periods after MR goes low, TRE returns high. Note: MR does not clear the receiver buffer register. CRL Control register load - a high level loads the control register with the character length, parity and stop bit length. See control register description below. TBRL Transmitter buffer register load - a low level transfers data from the inputs TBR1 to TBR8 into the transmitter buffer register. A low to high transition on this input requests data transfer to the transmitter register. If the transmitter register is busy, transfer is automatically delayed until the current transmission is completed at this point the next character is loaded and transmission of that character commences so that the two characters are transmitted end to end.

- **Control** The following inputs are used to set the control register status when the CRL input goes high.

- **CLS1**, Character length select these two inputs select the character length according to the following table.

| Character length (bits) | 5 | 6 | 7 | 8 |

|-------------------------|---|---|---|---|

| CLS1                    | L | Н | L | Н |

| CLS2                    | L | L | Н | н |

- PI Parity inhibit a high level inhibits parity generation, parity checking and forces the PE status flag output low. This input overrides the EPE input.

- **EPE** Even parity enable when the PI is set low a high level on the EPE input generates and checks even parity conversely a low level selects odd parity.

- SBS Stop bit select this input selects the number of stop bits. The number of stop bits added to the transmitted character also depends on the character length selected by the CLS1 and CLS2 inputs. The following table lists the number of stop bits selected versus the character length and state of the SBS input.

|           | Character length selected |                |           |

|-----------|---------------------------|----------------|-----------|

| SBS input | 5 bits                    | 6, 7 or 8 bits |           |

| L         | 1                         | 1              | 1         |

| н         | 11/2                      | 2              | Stop bits |

# **Status flags**

- TBRE\* Transmitter buffer register empty a high level on this output indicates that the transmitter buffer register has transferred its contents to the transmitter register and is ready to accept new data.

- TRE Transmitter register empty a logic high level indicates the transmission is completed including stop bits.

- PE\* Parity error a high level on parity error indicates that the received parity does not match the parity programmed by the control register bits. When parity is inhibited (refer to PI control input) the output is forced low.

- **FE**\* Framing error a high level indicates the first stop bit is invalid.

- **OE**\* Overrun error a high level indicates the data received flag was not cleared before the last character was transferred to the receiver register buffer.

- DR\* Data received a high level indicates a character has been correctly received and transferred to the receiver buffer register this output must be reset before a new character can be received (refer to DRR control input).

\* Status flags are three state and can be disabled (high impedance state) by using the status flags disable input (SFD) – refer to control input description.

## Data inputs and outputs

- **RBR1 to** The contents of the receiver buffer register appears on these outputs. Word formats less than 8 bits are right justified to RBR1. The outputs are forced to a high impedance state by applying a logic high to the RRD input.

- **RRI** Receiver register input serial data on this input is clocked into the receiver register.

- TBR1 to TBR8 - Character data is loaded into the transmitter buffer register via these inputs in conjunction with the TBRL input. For character formats of less than 8 bits, the TBR8, 7 or 6 inputs are ignored corresponding to the programmed character length.

- TRO Transmitter register output character data, start, stop and parity bits appear serially at this output.

## **Clock inputs**

- **RRC** Receiver register clock this input determines the rate at which the received data is clocked into the receiver register. The actual clock frequency should be 16 times the required data rate.

- **TRC** Transmitter register clock this input sets the transmitted data rate. The frequency of the clock should be 16 times the required data rate.

#### **Transmitter operation**

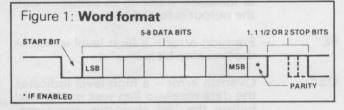

The transmitter section accepts parallel data, formats and transmits in serial form adding start, parity (if selected) and stop bits as shown in Fig. 1.

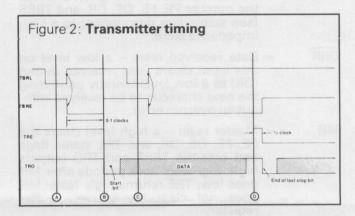

The sequence of events prior to and following the transmission of the data is described below together with the aid of the timing diagram shown in Fig. 2.

Data is loaded into the <u>TBR</u> from the inputs TR1 to TBR8 by a logic low on TBRL. Valid data must be present  $t_{DS}$  prior to the low to high transition of TBRL and remain valid at  $t_{DH}$  after this transition. If the data is less than 8 bits only the least significant bits are accepted. Following the transition of TBRL from low to high TBRE goes low indicating the TRB is not empty. If the transmitter register TR, is empty indicated by the TRE status output being high the data is transferred to the TR and transmission commences B between 0 to 1 clock periods later. Should TBRL go low again during the transmission shown at  $\bigcirc$  in Fig. 2 the data is loaded into the TBR as before and the TBRE status goes low following the TBRL low to high transition however the data is not immediately loaded into the TR, due to the transmission in progress, instead the data remains in the TBR until the last stop bit of the current transmission has been transmitted.

At (1) the data-in the TBR is automatically transferred into the TR and transmission of that character commences.

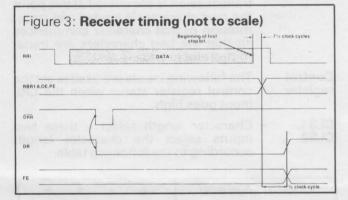

#### Receiver operation – refer to Fig. 3.

Data is received in serial form at the RR1 input, when no data is being received this input must remain high, the data is clocked into the RR at the clock rate which should be <u>16 times</u> the required data rate. A low level on the DRR clears the DR line and during the first stop bit data is transferred from the RR to the RBR. If the word length is less than 8

**R.S. Components Ltd.** PO Box 99, Corby, Northants, NN17 9RS An Electrocomponents Group Company

bits the unused most significant bits will be a logic low. The output character is right justified to the least significant bit RBR1.

A logic high on the OE status output indicates an overrun which occurs when the DR line has not been cleared before the present character was transferred to the RBR. A logic high on PE indicates a parity error.

One half clock cycle after the data is transferred to the RBR the DR line is set high and FE is evaluated. A logic high on the FE output indicates an invalid stop bit was received. The receiver will not begin searching for the next start bit until a correct stop bit is received.

## **Start bit detection**

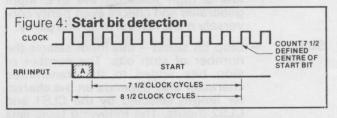

The receiver uses a 16 times clock for timing. The start bit  $\bigotimes$  in Fig. 4 could have occurred as much as one clock cycle before it was detected, as indicated by the crosshatched section. The centre of the start bit is defined as clock count 7½. If the receiver clock is a symmetrical square wave, the centre of the start bit will be located within  $\pm \frac{1}{2}$  clock cycles,  $\pm \frac{1}{32}$  bit or 3.125%. The receiver begins searching for the next start bit at the centre of the first stop bit.

Telephone: 0536 201234 ©RS Components Ltd. 1984

## 4046