# 3N 155,A (SILICON) 3N 156,A

CASE 20 (TO-72) P-channel silicon nitride passivated MOS field-effect enhancement mode transistors designed for chopper and switching application.

1 0 0 3

PIN 1. SOURCE

2. GATE

3. DRAIN

4. SUBSTRATE A

CASE LEAD

## MAXIMUM RATINGS

| Rating                                                                | Symbol                       | Value       | Unit        |  |

|-----------------------------------------------------------------------|------------------------------|-------------|-------------|--|

| Drain-Source Voltage                                                  | ${ m v}_{ m DS}$             | 35          | Vdc         |  |

| Drain-Gate Voltage                                                    | $v_{ m DG}$                  | 35          | Vdc         |  |

| Gate-Source Voltage                                                   | $v_{GS}$                     | 50          | Vdc         |  |

| Drain Current                                                         | $I_{D}$                      | 30          | mAdc        |  |

| Total Device Dissipation @ T <sub>A</sub> = 25°C<br>Derate above 25°C | $^{\mathrm{P}}\mathrm{_{D}}$ | 300<br>1.7  | mW<br>mW/°C |  |

| Operating Junction Temperature Range                                  | $^{\mathrm{T}}\mathrm{_{J}}$ | -65 to +175 | °C          |  |

| Storage Temperature Range                                             | T <sub>stg</sub>             | -65 to +200 | °C          |  |

### HANDLING PRECAUTIONS:

MOS field-effect transistors have extremely high input resistance. They can be damaged by the accumulation of excess static charge. Avoid possible damage to the devices while handling, testing, or in actual operation, by following the procedures outlined below:

- To avoid the build-up of static charge, the leads of the devices should remain shorted together with a metal ring except when being tested or used.

- 2. Avoid unnecessary handling. Pick up devices by the case instead of the leads.

- 3. Do not insert or remove devices from circuits with the power on because transient voltages may cause permanent damage to the devices.

# 3N155,A, 3N156,A (continued)

| Characteristic                                                                                                         | Symbol               | Min                   | Тур                   | Max         | Unit     |

|------------------------------------------------------------------------------------------------------------------------|----------------------|-----------------------|-----------------------|-------------|----------|

| OFF CHARACTERISTICS                                                                                                    |                      | 1                     |                       |             |          |

| Drain-Source Breakdown Voltage $(I_D = -10 \mu Adc, V_G = V_S = 0)$                                                    | V <sub>(BR)DSS</sub> | 35                    | -                     | -           | Vdc      |

| Gate Reverse Current $(V_{GS} = +50 \text{ Vdc}, V_{DS} = 0)$ $(V_{GS} = +25 \text{ Vdc}, V_{DS} = 0)$                 | I <sub>GSS</sub>     | -                     | -                     | 1000<br>10  | pAdc     |

| Zero-Gate Voltage Drain Current $(V_{DS} = -10 \text{ Vdc}, V_{GS} = 0)$ 3N155, 3N156 3N155A, 3N156A                   | I <sub>DSS</sub>     | -                     | -                     | 1.0<br>0.25 | nAdc     |

| $(V_{DS} = -10 \text{ Vdc}, V_{GS} = 0, T_A = 125^{\circ}\text{C}) 3N155, 3N156 3N155A, 3N156A$                        |                      | -                     | -                     | 1000<br>250 |          |

| Resistance Drain Source $(I_D = 0, V_{GS} = 0)$                                                                        | R <sub>DS(off)</sub> | 1 x 10 <sup>+10</sup> | -                     | -           | Ohms     |

| Resistance Gate Source Input $(V_{GS} = -25 \text{ Vdc})$                                                              | R <sub>GS</sub>      | -                     | 1 x 10 <sup>+16</sup> | -           | Ohms     |

| ON CHARACTERISTICS                                                                                                     |                      |                       |                       |             |          |

| Gate Source Threshold Voltage $(V_{DS} = -10 \text{ Vdc}, I_{D} = -10 \mu \text{Adc})$ 3N155, 3N155A 3N156A            | V <sub>GS(TH)</sub>  | 1.5<br>3.0            | -                     | 3.2<br>5.0  | Vdc      |

| Drain Source "ON" Voltage $(I_D = -2.0 \text{ mAdc}, V_{GS} = -10 \text{ Vdc})$                                        | V <sub>DS(on)</sub>  | -                     | ~                     | -1.0        | Vdc      |

| Gate Forward Leakage Current ( $V_{GS} = -50 \text{ Vdc}, V_{DS} = 0$ ) ( $V_{GS} = -25 \text{ Vdc}, V_{DS} = 0$ )     | I <sub>G(f)</sub>    |                       | -                     | 1000<br>10  | pAdc     |

| "ON" Drain Current<br>(V <sub>DS</sub> = -15 Vdc, V <sub>GS</sub> = -10 Vdc)                                           | I <sub>D(on)</sub>   | 5.0                   | -                     | -           | mAdc     |

| Static Drain-Source ''ON'' Resistance (I <sub>D</sub> = 0 mAdc, V <sub>GS</sub> = -10 Vdc) 3N155, 3N156 3N155A, 3N156A | r <sub>DS(on)</sub>  |                       | -                     | 600<br>300  | Ohms     |

| SMALL-SIGNAL CHARACTERISTICS                                                                                           |                      |                       |                       |             |          |

|                                                                                                                        | rds(on)              |                       | -                     | 600<br>300  | Ohms     |

| $(V_{GS} = -15 \text{ Vdc}, I_{D} = 0, f = 1.0 \text{ kHz})$ 3N155, 3N156 3N155A, 3N156A                               |                      | -                     | -                     | 500<br>250  |          |

| Forward Transfer Admittance ( $V_{DS} = -15 \text{ Vdc}, I_D = -2.0 \text{ mAdc}, f = 1.0 \text{ kHz}$ )               | y <sub>fs</sub>      | 1000                  | -                     | 4000        | μmhos    |

| Input Capacitance $(V_{DS} = -15 \text{ Vdc}, V_{GS} = -10 \text{ Vdc}, f = 140 \text{ kHz})$                          | C <sub>iss</sub>     | -                     | -                     | 5.0         | pF       |

| Reverse Transfer Capacitance ( $V_{DS} = 0$ , $V_{GS} = 0$ , $f = 140 \text{ kHz}$ )                                   | C <sub>rss</sub>     | -                     | -                     | 1, 3        | pF       |

| Drain-Substrate Capacitance<br>$(V_{D(SUB)} = -10 \text{ Vdc}, \text{ f} = 140 \text{ kHz})$                           | C <sub>d(sub)</sub>  | 4.0                   | -                     | -           | pF       |

| SWITCHING CHARACTERISTICS                                                                                              | Т.                   | T -                   | I                     | 45          | 1        |

| Turn-On Delay $(V_{DD} = -10 \text{ Vdc}, I_{D(on)} = -2.0 \text{ mAdc},$                                              | t <sub>d</sub>       | <u> </u>              | -                     | 65          | μs<br>ns |

| Rise Time $V_{GS(on)} = -10 \text{ Vdc}, V_{GS(off)} = 0$                                                              | t <sub>r</sub>       | _                     | _                     | 1 00        | 1115     |

| Turn-Off Delay GS(on) GS(off)                                                                                          | ts                   | _                     | _                     | 60          | ns       |

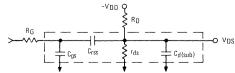

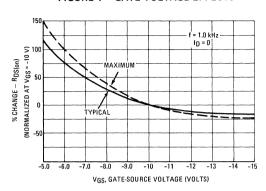

FIGURE 1 - GATE VOLTAGE EFFECTS

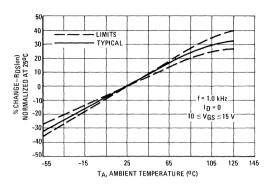

FIGURE 2 - TEMPERATURE EFFECTS

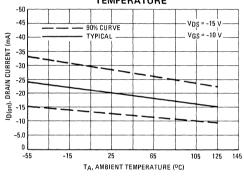

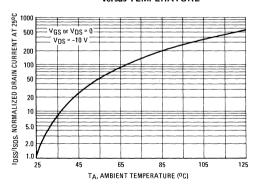

FIGURE 3 – DRAIN CURRENT versus TEMPERATURE

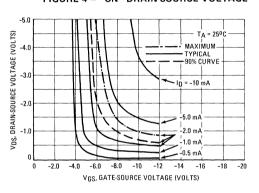

FIGURE 4 - "ON" DRAIN-SOURCE VOLTAGE

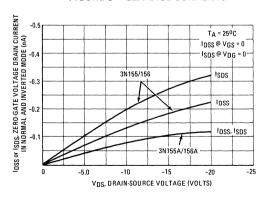

FIGURE 5 - LEAKAGE CURRENTS

FIGURE 6 - LEAKAGE CURRENT versus TEMPERATURE

## SWITCHING CHARACTERISTICS

$T_A = 25^{\circ}C$

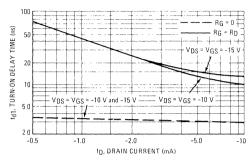

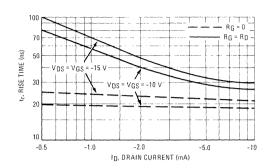

#### FIGURE 7 - TURN-ON DELAY TIME

FIGURE 8 - RISE TIME

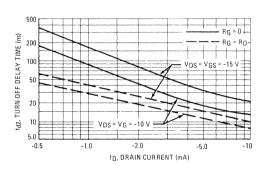

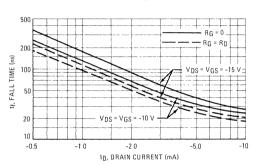

FIGURE 9 - TURN-OFF DELAY TIME

FIGURE 10 - FALL TIME

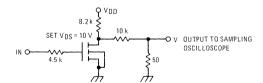

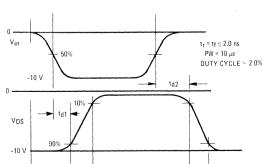

FIGURE 11 - SWITCHING CIRCUIT and WAVEFORMS

The switching characteristics shown above were measured in a test circuit similar to Figure 11. At the beginning of the switching interval, the gate voltage is at ground and the gate-source capacitance ( $C_{05} = C_{15} = C_{75} = C_{75}$ ) has no charge. The drain voltage is at  $V_{DD}$ , and thus the feedback capacitance ( $C_{C_{15}}$ ) is charged to  $V_{DD}$  Similarly, the drain-substrate capacitance ( $C_{d(Sub)}$ ) is charged to  $V_{DD}$  since the substrate and source are connected to ground

nected to ground During the turn-on interval,  $C_{gS}$  is charged to  $V_{GS}$  (the input voltage) through  $R_G$  (generator impedance) (Figure 12).  $C_{rSS}$  must be discharged to  $V_{GS} - V_{D(n)}$  through  $R_G$  and the parallel combination of the load resistor  $(R_D)$  and the channel resistance  $(r_{rgs})$ . In addition,  $C_{d(Sh)}$  is discharged to a low value  $(V_{D(n)})$ through  $R_D$  in parallel with  $d_S$ . During turn-off this charge flow is reversed.

$(r_{dS})$ . In addition,  $(J_{dSub})$  is discharged to a low value  $(V|J_{OR})$ /through RD in parallel with  $d_s$  During turn-off this charge flow is reversed. Predicting turn-on time proves to be somewhat difficult since the channel resistance  $(r_{dS})$  is a function of the gate-source voltage  $(V_{dS})$ . As  $C_{dS}$  becomes charged  $V_{GS}$  is approaching  $V_{dS}$  and  $C_{dSub}$  are charged through  $C_{dSub}$  and  $C_{dSub}$  are charged  $C_{dSub}$  and  $C_{dSub}$

If the charging time of  $G_{SS}$  is short compared to that of  $C_{TSS}$  and  $C_{d(Sub)}$ , then  $r_{dS}$  (which is in parallel with  $R_D$ ) will be low compared to  $R_D$  during the switching interval and will largely determine the turn-on time. On the other hand, during turn-off  $r_{dS}$  will be almost an open circuit requiring  $G_{TSS}$  and  $G_{d(Sub)}$  to be charged through  $R_D$  and resulting in a turn-off time that is long compared to the turn-on time. This is especially noticeable for the curves where  $R_D = 0$  and  $G_{DSS}$  is charged through the pulse generator impedance only.

The switching curves shown with  $R_G=R_D$  simulate the switching behavior of cascaded stages where the driving source impedance is normally the same as the load impedance. The set of curves with  $R_G=0$  simulates a low source impedance drive such as might occur in complementary logic circuits.

FIGURE 12 – SWITCHING CIRCUIT with MOSFET EQUIVALENT MODEL