The RS2376 Keyboard Encoder I.C. is a fully integrated P-MOS keyswitch encoding circuit, suitable for encoding a keyboard with up to 88 switches, plus shift and control, into a useable 9 bit data code, i.e. the standard 8 bit ASC II data code + one parity bit.

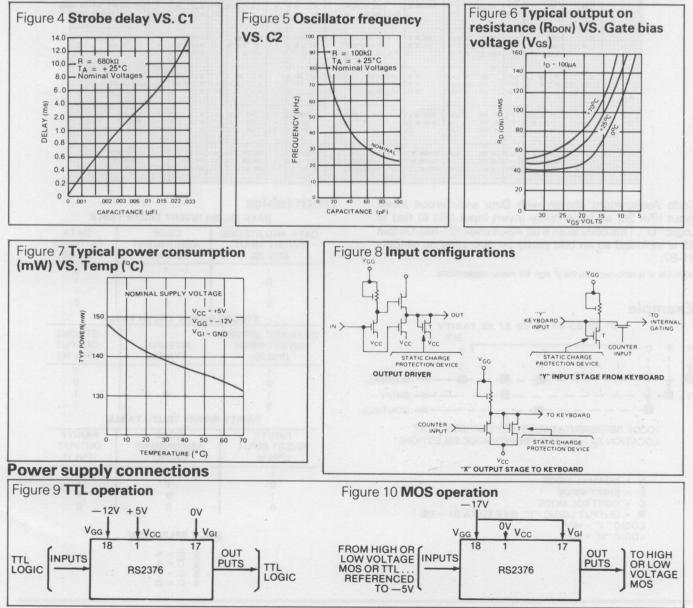

The RS2376 offers the facilities of two key roll-over operation with N-key lockout and has userselectable odd or even parity and output polarity. A self contained oscillator and debounce circuit are incorporated in the device, requiring only the addition of a resistor and capacitor for each function. The outputs are directly TTL/MOS logic compatible.

The RS 76 key Keyboard (336-703) is designed to accept the RS2376 Keyboard Encoder I.C., enabling a full ASCII code keyboard to be easily constructed.

## Features

- •One integrated circuit required for complete keyboard assembly.

- Outputs directly compatible with TTL or MOS logic arrays.

- External control provided for output polarity selection.

- External control provided for selection of odd or even parity.

- Two key roll-over operation.

- N-key lockout.

- Self-contained oscillator circuit.

- Externally controlled delay network provided to eliminate the effect of contact bounce.

- Static charge protection on all input and output terminals.

## 4080 **Electrical characteristics Maximum ratings**

$V_{GI}$  and  $V_{GG}$  (with respect to  $V_{CC}$ ) \_\_\_\_\_20V to +0.3 V Logic input voltages (with respect to  $V_{CC}$ ) \_\_\_\_20 V to 0.3 V \_\_\_65°C to +150°C Storage Temperature\_\_\_ Operating Temperature Range\_  $-0^{\circ}C$  to  $+70^{\circ}C$  Exceeding these ratings could cause permanent damage. Functional operation of this device at these conditions is not implied—operating ranges are specified below.

Standard Conditions (unless otherwise noted)

$\begin{array}{ll} V_{CC}{=}5 \mbox{ Volts }{\pm} \ 0.5 \mbox{ Volts,} & (V_{cc}{=}Substrate \mbox{ Voltage}) \\ V_{GG}{=}{-}12 \mbox{ Volts }{\pm} \ 1.0 \mbox{ Volts,} \ V_{GI}{=}OV \\ Operating \mbox{ Temperature } (TA){=}0^{\circ}C \mbox{ to }{+}70^{\circ}C \end{array}$

| Characteristics ·                                                                                             | Conditions                                                                                                              | Symbol                                  | Min                                     | Тур*                            | Max                             | Units                |

|---------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|-----------------------------------------|---------------------------------|---------------------------------|----------------------|

| Clock Frequency                                                                                               | See Block diagram (Figure 2)<br>footnote for typical<br>R — C values                                                    | f                                       | 10                                      | 50                              | 100                             | kHz                  |

| Data Input<br>(Shift, Control, Parity<br>invert, data & strobe invert).<br>Logic "0" Level<br>Logic "1" Level | Aver + arrays.<br>•External control<br>Il over adiation.<br>user • External control p<br>wity A even ownby              | V <sub>10</sub><br>V <sub>11</sub>      | V <sub>GG</sub><br>V <sub>CC</sub> —1.5 | the fac<br>N-⊡y                 | + 0.8<br>V <sub>cc</sub> + 0.3  | v<br>v               |

| Shift & Control Input<br>Current                                                                              | $V_1 = +5V$<br>$V_1 = 0V$                                                                                               |                                         | 15<br>8                                 |                                 | 60<br>30                        | μΑ<br>μΑ             |

| Data, Parity Invert Input<br>Current                                                                          | $V_1 = -5V \text{ to } + 5V$                                                                                            | J <sub>IND,P</sub>                      |                                         | .01                             | 1                               | μΑ                   |

| X Output (X <sub>0</sub> -X <sub>7</sub> )<br>Logic "1" Output Current                                        | $V_{OUT} = V_{CC}$ $V_{OUT} = V_{CC} - 1.3V$ $V_{OUT} = V_{CC} - 2.0V$ $V_{OUT} = V_{CC} - 5V$ $V_{OUT} = V_{CC} - 10V$ | · I <sub>XI</sub>                       |                                         | 0<br>150<br>300<br>700<br>1500  | 400<br>800<br>1500<br>3000      | μΑ<br>μΑ<br>μΑ<br>μΑ |

| Logic "0" Output Current                                                                                      | $V_{OUT} = V_{CC}$ $V_{OUT} = V_{CC} - 1.3V$ $V_{OUT} = V_{CC} - 2.0V$ $V_{OUT} = V_{CC} - 5V$ $V_{OUT} = V_{CC} - 10V$ | Ixo                                     | 15<br>13<br>12<br>5<br>—                | 30<br>27<br>25<br>10<br>1       | 80<br>65<br>60<br>40<br>20      | μΑ<br>μΑ<br>μΑ<br>μΑ |

| Y Input (Y <sub>0</sub> -Y <sub>10</sub> )<br>Trip Level                                                      | Y Input Going<br>Positive                                                                                               | Vy                                      | V <sub>cc</sub> —5                      | V <sub>cc</sub> —3              | V <sub>cc</sub> -2              | v                    |

| Hysteresis                                                                                                    | Note 1<br>Note 2                                                                                                        | ΔV <sub>Y</sub>                         | 0.5                                     | 0.9                             | 1.4                             | V                    |

| Selected Y Input Current                                                                                      | $V_{IN} = V_{CC} \\ V_{IN} = V_{CC} - 1.3V \\ V_{IN} = V_{CC} - 2.0V \\ V_{IN} = V_{CC} - 5V \\ V_{IN} = V_{CC} - 10V$  | I <sub>YS</sub>                         | 30<br>26<br>24<br>10                    | 60<br>54<br>50<br>20<br>2       | 160<br>130<br>120<br>80<br>20   | μΑ<br>μΑ<br>μΑ<br>μΑ |

| Unselected Y Input Current                                                                                    | $V_{IN} = V_{CC}$ $V_{IN} = V_{CC} - 1.3V$ $V_{IN} = V_{CC} - 2.0V$ $V_{IN} = V_{CC} - 10$                              | I <sub>YU</sub>                         | 15<br>13<br>12<br>5                     | 30<br>27<br>25<br>10            | 80<br>65<br>60<br>40            | μΑ<br>μΑ<br>μΑ<br>μΑ |

| Input Capacitance                                                                                             | at OV                                                                                                                   | CIN                                     | _                                       | 3                               | 10                              | pF                   |

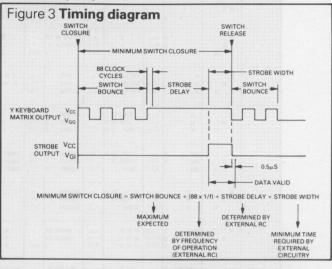

| Switch Characteristics<br>Minimum Switch Closure<br>Contact Closure<br>Resistance                             | See Timing Diagram (Figure 3)                                                                                           | –<br>Z <sub>cc</sub><br>Z <sub>co</sub> | —<br>—<br>10 <sup>7</sup>               |                                 | <br>300                         | <br>Ω                |

| Strobe Delay<br>Trip Level (Pin 19)<br>Hysteresis<br>Quiescent Voltage (Pin 19)                               | See Note 1 With 680k $\Omega$ to V <sub>CC</sub>                                                                        | V <sub>SD</sub><br>V <sub>SD</sub>      | V <sub>cc</sub> -4<br>0.5<br>-3         | V <sub>cc</sub> —3<br>0.9<br>—5 | V <sub>cc</sub> -2<br>1.4<br>-8 | V<br>V<br>V          |

| Data Output (B <sub>1</sub> -B <sub>9</sub> )<br>Logic "O"<br>Logic "1"                                       | I <sub>OL</sub> = 1.6mA<br>I <sub>OH</sub> =-100μA                                                                      |                                         | _<br>V <sub>cc</sub> _1                 |                                 | 0.4                             | V<br>V               |

| Power<br>I <sub>CC</sub><br>I <sub>GG</sub>                                                                   | $V_{CC} = +5V$ $V_{GG} = -12V$                                                                                          |                                         | _                                       | 5<br>5                          | 10<br>10                        | mA<br>mA             |

Typical values at +25°C and nominal voltages.

NOTE 1. Hysteresis is defined as the amount of return required to unlatch an input.

2. Guaranteed number of X & Y loads which may be applied to an X

output=eleven.

2

## Operation

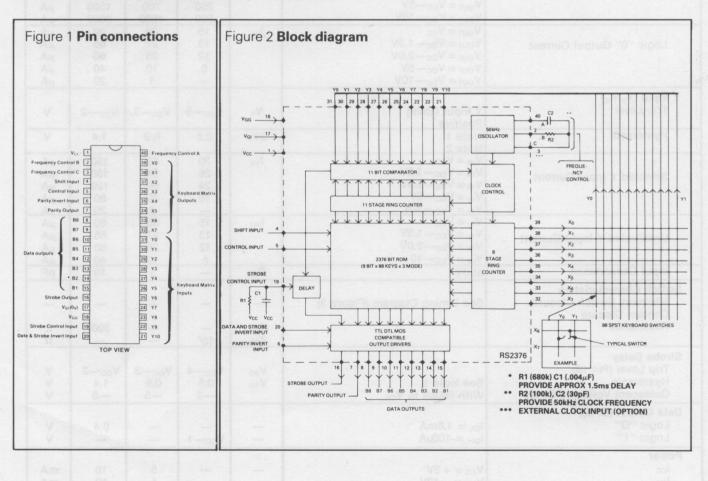

The RS2376 contains a 2376-bit ROM, 8-stage and 11-stage ring counters, an 11-bit comparator, an oscillator circuit, an externally controllable delay network for eliminating the effect of contact bounce, and TTL/MOS compatible output drivers.

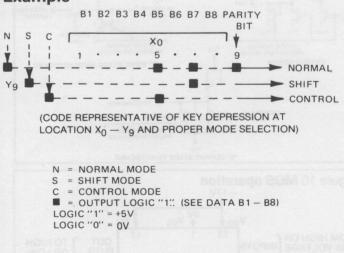

The ROM portion of the chip is a 264 by 9 bit memory arranged into three 88-word by 9-bit groups. The appropriate levels on the Shift and Control Inputs selects one of the three 88-word groups; the 88-individual word locations are addressed by the two ring counters. Thus, the ROM address is formed by combining the Shift and Control Inputs with the two ring counters.

The external outputs of the 8-stage ring counter and the external inputs to the 11-bit comparator are wired to the keyboard to form an X-Y matrix with the 88-keyboard switches as the crosspoints. In the standby condition, when no key is depressed, the two ring counters are clocked and sequentially address the ROM; the absence of a Strobe Output indicates that the Data Outputs are 'not valid' at this time.

When a key is depressed, a single path is completed between one output of the 8-stage ring counter (X0-X7) and one input of the 11-bit cmparator (Y0-Y10). After a number of clock cycles, a condition will occur where a level on the selected path to the comparator matches a level on the corresponding comparator input from the 11-stage ring counter. When this occurs, the comparator generates a signal to the clock control and the Strobe Output (via the

delay network). The clock control stops the clocks to the ring counters and the Data Outputs (B1-B9) stabilize with the selected 9-bit code, indicated by a 'valid' signal on the Strobe Output. The Data Outputs remain stable until the key is released.

As an added feature two inputs are provided for external polarity control of the Data Outputs. Parity Invert (pin 6) provides polarity control of the Parity Output (pin 7) while the Data and Strobe Invert Input (pin 20) provides for polarity control of Data Outputs B1-D8 (pins 8-15) and the Strobe Output (pin 16).

3

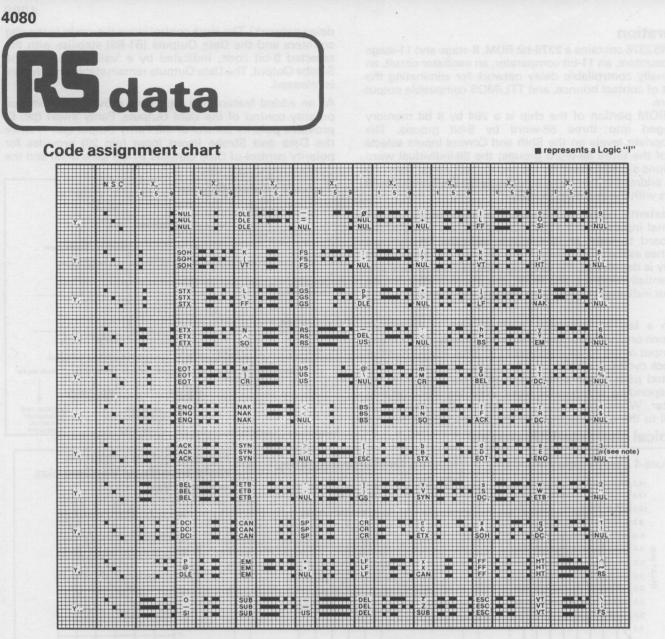

Code Assignment shown with Data and Strobe Invert Input (Pin 20) and the Parity Invert Input (Pin 6) tied to Logic "O". This code is an 8 bit ASCII code (B1-B8). Output B9 is included as an odd parity bit operating on outputs B1-B7.

Note: the # is replaced with the € sign for many applications.

## **Truth tables**

| DATA AND STROBE                             | CODE                                                                                                                                 | DATA                         |  |

|---------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|------------------------------|--|

| INVERT INPUT                                | ASSIGNMENT                                                                                                                           | OUTPUTS                      |  |

| (PIN 20)                                    | CHART                                                                                                                                | (B1-B8)                      |  |

| 1                                           | 1                                                                                                                                    | 0                            |  |

| 0                                           | 1                                                                                                                                    | 1                            |  |

| 1                                           | 0                                                                                                                                    | 1                            |  |

| 0                                           | 0                                                                                                                                    | 0                            |  |

| STROBE I                                    | NVERT TRUTH TAE                                                                                                                      | 1                            |  |

| DATA AND STROBE<br>INVERT INPUT<br>(PIN 20) | INTERNAL<br>STROBE                                                                                                                   | STROBE<br>OUTPUT<br>(PIN 16) |  |

| 1                                           | 1                                                                                                                                    | 0                            |  |

| 0                                           | 0                                                                                                                                    | 0                            |  |

| 1                                           | 0                                                                                                                                    | 1                            |  |

| 0                                           | 1                                                                                                                                    | 1                            |  |

| PARITY IN                                   | IVERT TRUTH TAB                                                                                                                      | LE                           |  |

| PARITY                                      | CODE                                                                                                                                 | PARITY                       |  |

| INVERT INPUT                                | ASSIGNMENT                                                                                                                           | OUTPUT                       |  |

| (PIN 6)                                     | CHART                                                                                                                                | (PIN 7)                      |  |

| 1                                           | 1                                                                                                                                    | 0                            |  |

| 0                                           | 1                                                                                                                                    | 1                            |  |

| 1                                           | 0                                                                                                                                    | 1                            |  |

| 0                                           | 0                                                                                                                                    | 0                            |  |

| M                                           | ODE SELECTION                                                                                                                        |                              |  |

|                                             | $ \begin{array}{c} \overline{S}  \overline{C} = S \\ \overline{S}  \overline{C} = S \\ \overline{S}  C = C \\ S  C = C \end{array} $ |                              |  |

**R.S. Components Ltd.** PO Box 99, Corby, Northants, NN17 9RS An Electrocomponents Group Company Telephone: 0536 201234 ©RS Components Ltd. 1984