# Intel StrataFlash® Embedded Memory (P33)

### **Datasheet**

## **Product Features**

- High performance:

- 85 ns initial access

- 52MHz with zero wait states, 17ns clock-todata output synchronous-burst read mode

- 25 ns asynchronous-page read mode

- 4-, 8-, 16-, and continuous-word burst mode

- Buffered Enhanced Factory Programming (BEFP) at 5 µs/byte (Typ)

- 3.0 V buffered programming at 7 μs/byte (Typ)

- Architecture:

- Multi-Level Cell Technology: Highest Density at Lowest Cost

- Asymmetrically-blocked architecture

- Four 32-KByte parameter blocks: top or bottom configuration

- 128-KByte main blocks

- Voltage and Power:

- V<sub>CC</sub> (core) voltage: 2.3 V 3.6 V

- $V_{CCQ} (I/O)$  voltage: 2.3 V 3.6 V

- Standby current: 70 μA (Typ) for 256-Mbit

- 4-Word synchronous read current: 16 mA (Typ) at 52MHz

- Quality and Reliability

- Operating temperature: -40 °C to +85 °C

- Minimum 100,000 erase cycles per block

- ETOX™ VIII process technology (130 nm)

### Security:

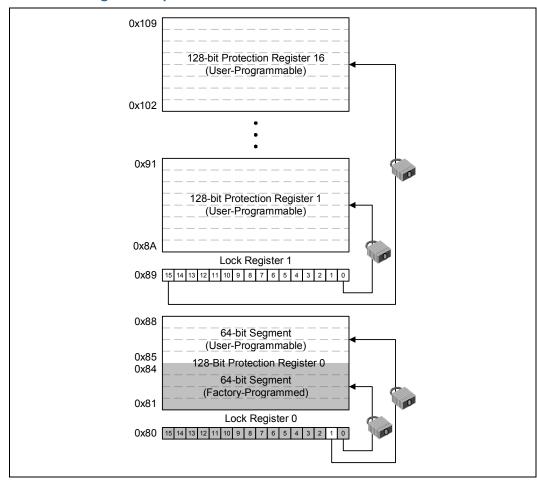

- One-Time Programmable Registers:

- 64 unique factory device identifier bits

- 64 user-programmable OTP bits

- Additional 2048 user-programmable OTP bits

- Selectable OTP space in Main Array:

- Four pre-defined 128-KByte blocks (top or bottom configuration.

- Entire Array OTP (Top or Bottom Config.)

- Absolute write protection:  $V_{PP} = V_{SS}$

- Power-transition erase/program lockout

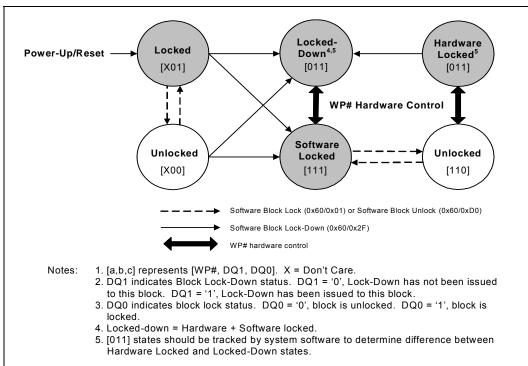

- Individual zero-latency block locking

- Individual block lock-down

- Software:

- 20 μs (Typ) program suspend

- 20 μs (Typ) erase suspend

Intel<sup>®</sup> Flash Data Integrator optimized

- Basic Command Set and Extended Command Set compatible

- Common Flash Interface capable

- Density and Packaging

- 56-Lead TSOP package (64, 128, 256, 512-Mbit)

- 64-Ball Intel® Easy BGA package (64, 128, 256, 512-Mbit)

- Intel® QUAD+ SCSP (64, 128, 256, 512-Mbit)

- 16-bit wide data bus

P33 is the latest generation of Intel StrataFlash® memory devices. Offered in 64-Mbit up through 512-Mbit densities, the P33 flash memory device brings reliable, two-bit-per-cell storage technology to the embedded flash market segment. Benefits include more density in less space, high-speed interface, lowest cost-per-bit NOR device, and support for code and data storage. Features include high-performance synchronous-burst read mode, fast asynchronous access times, low power, flexible security options, and three industry standard package choices.

P33 product family is manufactured using Intel<sup>®</sup> 130 nm ETOX™ VIII process technology.

Order Number: 314749-002US

August 2006

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL® PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER, AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. Intel products are not intended for use in medical, life saving, life sustaining, critical control or safety systems, or in nuclear facility applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Intel Corporation may have patents or pending patent applications, trademarks, copyrights, or other intellectual property rights that relate to the presented subject matter. The furnishing of documents and other materials and information does not provide any license, express or implied, by estoppel or otherwise, to any such patents, trademarks, copyrights, or other intellectual property rights.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an order number and are referenced in this document, or other Intel literature may be obtained by calling 1-800-548-4725 or by visiting Intel's website at http://www.intel.com.

Intel the Intel logo, Intel StrataFlash, and ETOX are trademarks or registered trademarks of Intel Corporation or its subsidiaries in the United States and other countries.

August 2006

www.DataSheet4U.com

Order Number: 314749-002US

\*Other names and brands may be claimed as the property of others.

Copyright  $\ensuremath{@}$  2006, Intel Corporation. All Rights Reserved.

## **Contents**

| 1.0  | Intro  | duction                              | . 7 |

|------|--------|--------------------------------------|-----|

|      | 1.1    | Nomenclature                         | . 7 |

|      | 1.2    | Acronyms                             |     |

|      | 1.3    | Conventions                          | . 7 |

| 2.0  | Funct  | tional Overview                      | . ( |

|      | 2.1    | Virtual Chip Enable Description      | . 9 |

| 3.0  | Packa  | age Information                      | 11  |

|      | 3.1    | 56-Lead TSOP Package                 |     |

|      | 3.2    | 64-Ball Easy BGA Package             |     |

|      | 3.3    | QUAD+ SCSP Packages                  | 15  |

| 4.0  | Ballo  | ut and Signal Descriptions           | 18  |

|      | 4.1    | Signal Ballout                       | 18  |

|      | 4.2    | Signal Descriptions                  | 21  |

|      | 4.3    | Dual Die SCSP Configurations         |     |

|      | 4.4    | Memory Maps                          | 25  |

| 5.0  | Maxir  | mum Ratings and Operating Conditions | 28  |

|      | 5.1    | Absolute Maximum Ratings             |     |

|      | 5.2    | Operating Conditions                 | 29  |

| 6.0  | Electi | rical Specifications                 | 30  |

|      | 6.1    | DC Current Characteristics           | 30  |

|      | 6.2    | DC Voltage Characteristics           | 32  |

| 7.0  | AC C   | naracteristics                       | 33  |

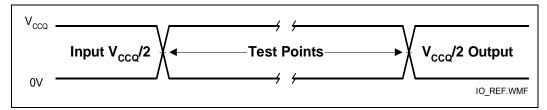

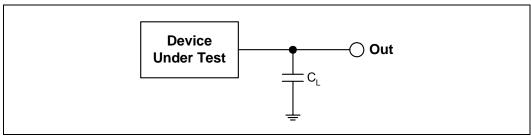

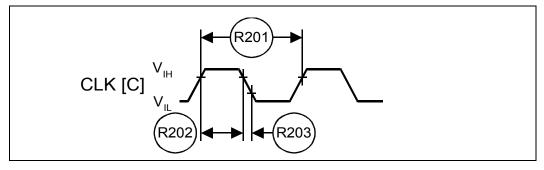

|      | 7.1    | AC Test Conditions                   |     |

|      | 7.2    | Capacitance                          | 34  |

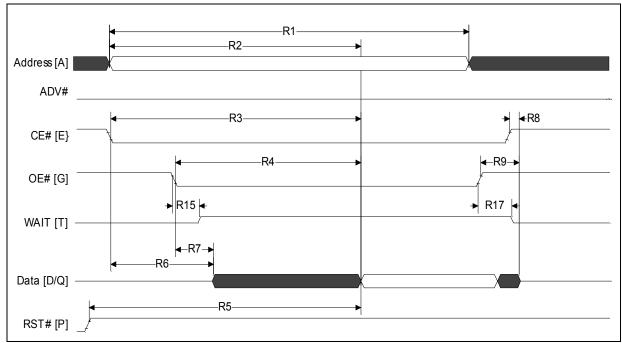

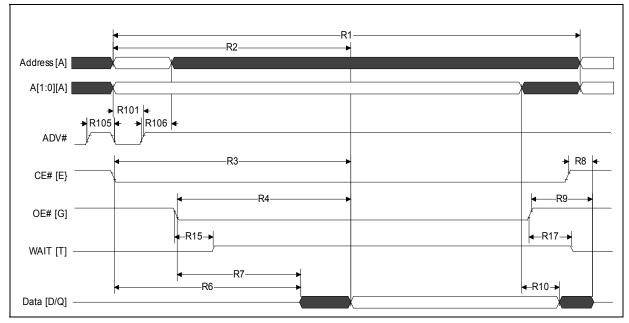

|      | 7.3    | AC Read Specifications               |     |

|      | 7.4    | AC Write Specifications              |     |

|      | 7.5    | Program and Erase Characteristics    | 43  |

| 8.0  | Powe   | er and Reset Specifications          | 44  |

|      | 8.1    | Power Up and Down                    |     |

|      | 8.2    | Reset Specifications                 |     |

|      | 8.3    | Power Supply Decoupling              | 45  |

| 9.0  | Devic  | e Operations                         |     |

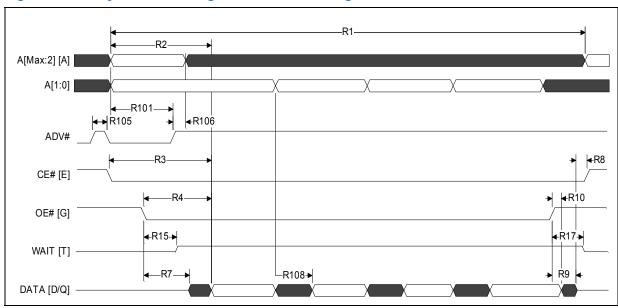

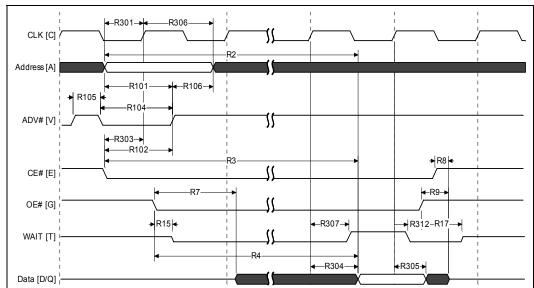

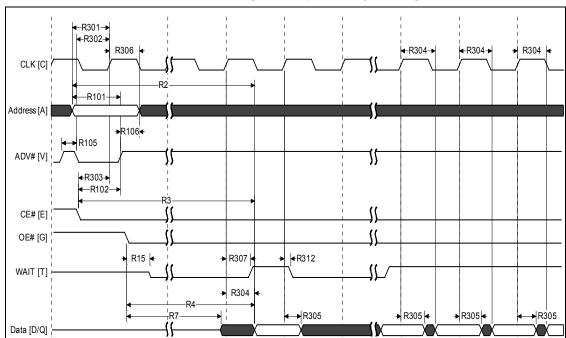

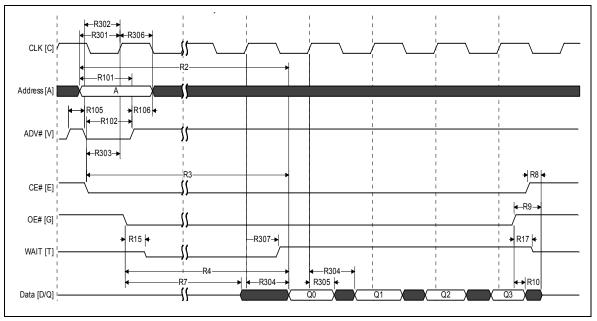

|      | 9.1    | Bus Operations                       |     |

|      |        | 9.1.1 Reads                          |     |

|      |        | 9.1.2 Writes                         |     |

|      |        | 9.1.3 Output Disable                 |     |

|      |        | 9.1.5 Reset.                         |     |

|      | 9.2    | Device Commands                      |     |

|      | 9.3    | Command Definitions                  |     |

| 10.0 | Read   | Operations                           | 51  |

|      | 10.1   | Asynchronous Page-Mode Read          |     |

|      |        | Synchronous Burst-Mode Read          |     |

|      |        | Read Configuration Register          |     |

|      |        | 10.3.1 Read Mode                     | 53  |

|      |        | 10.3.2 Latency Count                 | 53  |

|      |       | 10.3.3 WAIT Polarity                                    |    |

|------|-------|---------------------------------------------------------|----|

|      |       | 10.3.3.1 WAIT Signal Function                           |    |

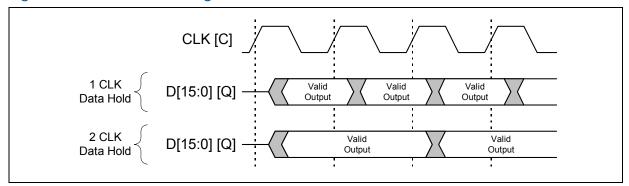

|      |       | 10.3.4 Data Hold                                        |    |

|      |       | 10.3.5 WAIT Delay                                       |    |

|      |       | 10.3.6 Burst Sequence                                   |    |

|      |       | 10.3.7 Clock Edge                                       |    |

|      |       | 10.3.8 Burst Wrap                                       |    |

|      |       | 10.3.9 Burst Length                                     | 58 |

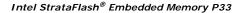

| 11.0 | Progr | ramming Operations                                      | 59 |

|      | 11.1  | Word Programming                                        | 59 |

|      |       | 11.1.1 Factory Word Programming                         |    |

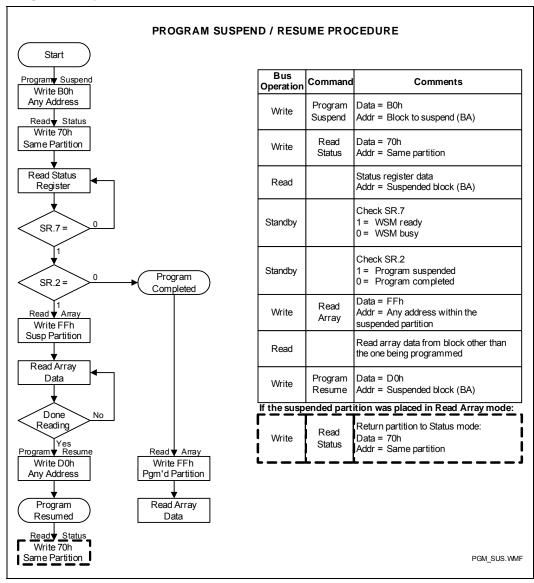

|      | 11.2  | Buffered Programming                                    |    |

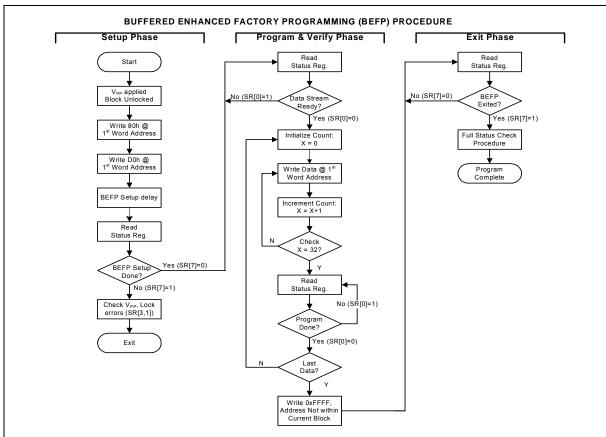

|      | 11.3  | Buffered Enhanced Factory Programming                   | 61 |

|      |       | 11.3.1 BEFP Requirements and Considerations             | 61 |

|      |       | 11.3.2 BEFP Setup Phase                                 | 62 |

|      |       | 11.3.3 BEFP Program/Verify Phase                        |    |

|      |       | 11.3.4 BEFP Exit Phase                                  | 63 |

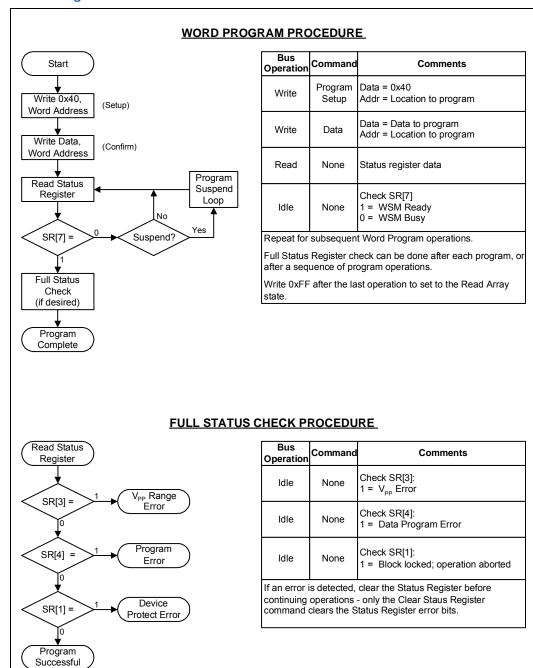

|      | 11.4  | Program Suspend                                         |    |

|      | 11.5  | 3                                                       |    |

|      | 11.6  | Program Protection                                      | 64 |

| 12.0 | Erase | e Operations                                            | 65 |

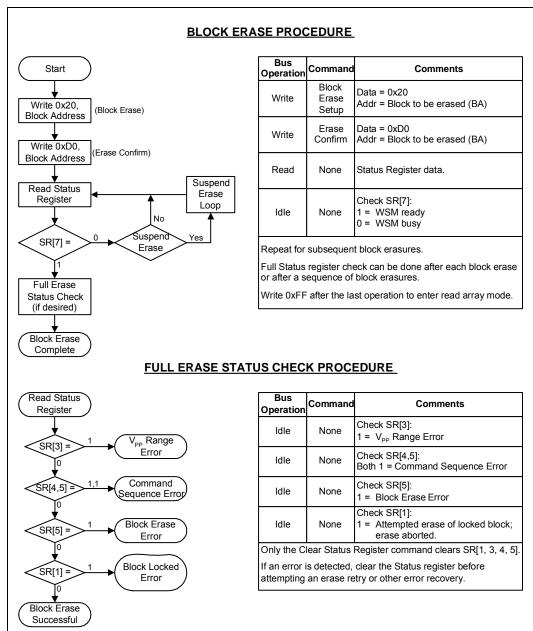

|      | 12.1  | Block Erase                                             |    |

|      |       |                                                         |    |

|      | 12.3  |                                                         |    |

|      |       | Erase Protection                                        |    |

| 400  |       |                                                         |    |

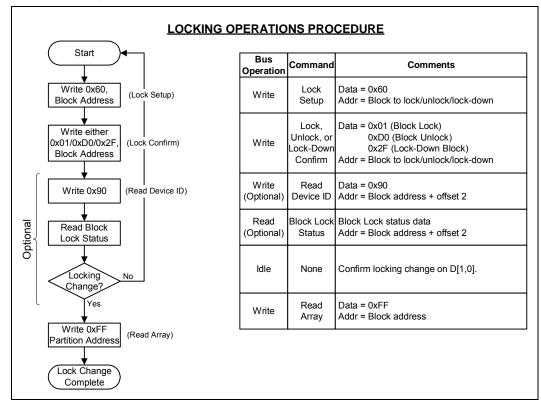

| 13.0 |       | rity Modes                                              |    |

|      | 13.1  |                                                         |    |

|      |       | 13.1.1 Lock Block                                       |    |

|      |       | 13.1.2 Unlock Block                                     |    |

|      |       | 13.1.3 Lock-Down Block                                  |    |

|      |       | 13.1.4 Block Lock Status                                |    |

|      | 13.2  | Selectable One-Time Programmable Blocks                 |    |

|      | 13.2  | 13.2.1 Permanent Block Locking of up to 512KB           |    |

|      |       | 13.2.2 Permanent Block Locking of up to Full Main Array | 70 |

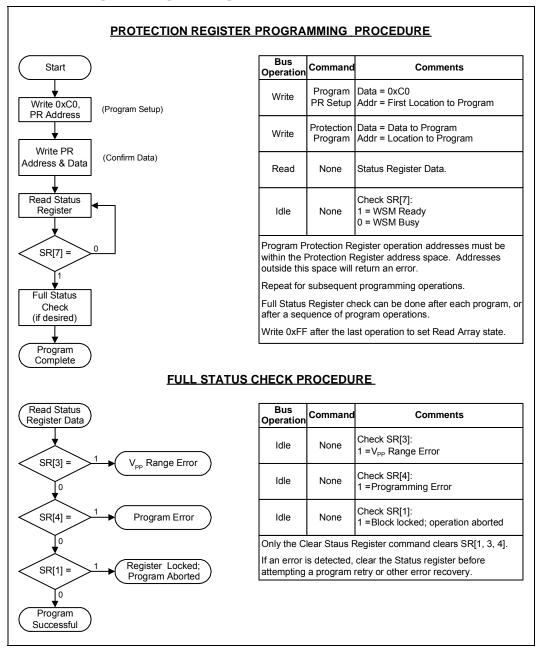

|      | 13.3  | Protection Registers                                    |    |

|      | 13.3  | 13.3.1 Reading the Protection Registers                 |    |

|      |       | 13.3.2 Programming the Protection Registers             |    |

|      |       | 13.3.3 Locking the Protection Registers                 |    |

| 440  | C:    |                                                         |    |

| 14.0 | •     | ial Read States                                         |    |

|      | 14.1  | Read Status Register                                    |    |

|      | 110   | 14.1.1 Clear Status Register                            |    |

|      | 14.2  | Read Device Identifier                                  |    |

|      | 14.3  | CFI Query                                               | /5 |

| Α    | Write | e State Machine                                         | 76 |

| В    | Flows | charts                                                  | Q٥ |

| ט    |       |                                                         |    |

| С    | Comn  | mon Flash Interface                                     |    |

|      | C.1   | Query Structure Output                                  |    |

|      | C.2   | Query Structure Overview                                |    |

|      | C.3   | CFI Query Identification String                         |    |

|      | C.4   | Device Geometry Definition                              | 94 |

## Intel StrataFlash® Embedded Memory P33

|   | C.5   | Intel-Specific Extended Query Table    | 95  |

|---|-------|----------------------------------------|-----|

| D | Addit | ional Information                      | 101 |

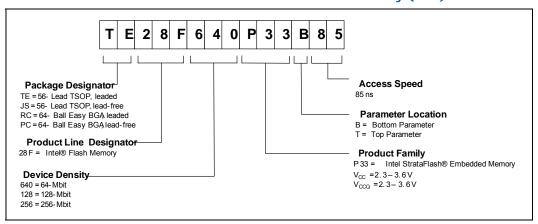

| E | Orde  | ring Information for Discrete Products | 102 |

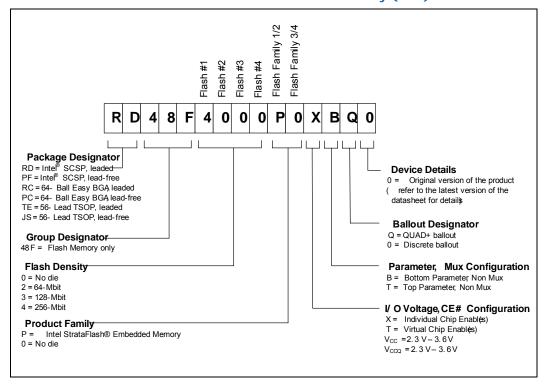

| F | Orde  | ring Information for SCSP Products     | 103 |

August 2006 Order Number: 314749-002US Intel StrataFlash® Embedded Memory P33 Flash Memory Datasheet 5 WWW.DataSheet4U.com

August 2006 Order Number: 314749-002US www.DataSheet4U.com

# **Revision History**

| Date        | Revision | Description     |

|-------------|----------|-----------------|

| April 2006  | 001      | Initial release |

| August 2006 | 002      | Product release |

#### 1.0 Introduction

This document provides information about the Intel StrataFlash® Embedded Memory P33 device and describes its features, operation, and specifications.

#### 1.1 Nomenclature

$V_{CC}$  (core) and  $V_{CCO}$  (I/O) voltage range of 2.3 V – 3.6 V 3.0 V:

9.0 V : V<sub>PP</sub> voltage range of 8.5 V – 9.5 V

A group of bits, bytes, or words within the flash memory array that erase simultaneously when the Erase command is issued to the device. The Intel StrataFlash® Embedded Memory P33 has two block sizes: 32-Block:

KByte and 128-KByte.

An array block that is usually used to store code and/or data. Main Main block:

blocks are larger than parameter blocks.

An array block that is usually used to store frequently changing data or Parameter block:

small system parameters that traditionally would be stored in EEPROM.

A device with its parameter blocks located at the highest physical Top parameter device:

address of its memory map.

A device with its parameter blocks located at the lowest physical Bottom parameter device :

address of its memory map.

### 1.2 **Acronyms**

BEFP: **Buffer Enhanced Factory Programming**

CUI: Command User Interface

MLC: Multi-Level Cell

OTP: One-Time Programmable PLR: Protection Lock Register PR: Protection Register

RCR: Read Configuration Register RFU: Reserved for Future Use

SR: Status Register WSM: Write State Machine

#### 1.3 Conventions

VCC: Signal or voltage connection  $\mathbf{v}_{cc}$ : Signal or voltage level Ox: Hexadecimal number prefix Binary number prefix

SR[4]: Denotes an individual register bit.

Denotes a group of similarly named signals, such as address or data A[15:0]:

August 2006 Order Number: 314749-002US Intel® P33 Flash Memory Datasheet www.DataSheet4U.com

Denotes one element of a signal group membership, such as an individual address bit. A5 :

Bit: Binary unit Eight bits Byte:

Word : Two bytes, or sixteen bits

Kbit : 1024 bits KByte: 1024 bytes KWord: 1024 words Mbit : 1,048,576 bits MByte: 1,048,576 bytes MWord: 1,048,576 words

August 2006 Order Number: 314749-002US www.DataSheet4U.com

## 2.0 Functional Overview

This section provides an overview of the features and capabilities of the Kearny Family Flash memory.

The Intel StrataFlash<sup>®</sup> Embedded Memory P33 provides density upgrades from 64-Mbit through 512-Mbit. This family of devices provides high performance at low voltage on a 16-bit data bus. Individually erasable memory blocks are sized for optimum code and data storage.

Upon initial power up or return from reset, the device defaults to asynchronous pagemode read. Configuring the Read Configuration Register enables synchronous burstmode reads. In synchronous burst mode, output data is synchronized with a usersupplied clock signal. A WAIT signal provides an easy CPU-to-flash memory synchronization.

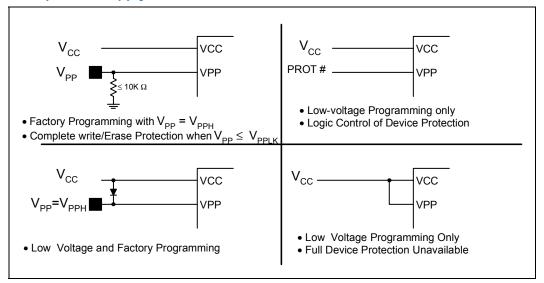

In addition to the enhanced architecture and interface, the device incorporates technology that enables fast factory program and erase operations. Designed for low-voltage systems, the Intel StrataFlash  $^{\circledR}$  Embedded Memory P33 supports read operations with  $V_{CC}$  at 3.0 V, and erase and program operations with  $V_{PP}$  at 3.0 V or 9.0 V. Buffered Enhanced Factory Programming (BEFP) provides the fastest flash array programming performance with  $V_{PP}$  at 9.0 V, which increases factory throughput. With  $V_{PP}$  at 3.0 V, VCC and VPP can be tied together for a simple, ultra low power design. In addition to voltage flexibility, a dedicated VPP connection provides complete data protection when  $V_{PP} \leq V_{PPLK}$ .

A Command User Interface (CUI) is the interface between the system processor and all internal operations of the device. An internal Write State Machine (WSM) automatically executes the algorithms and timings necessary for block erase and program. A Status Register indicates erase or program completion and any errors that may have occurred.

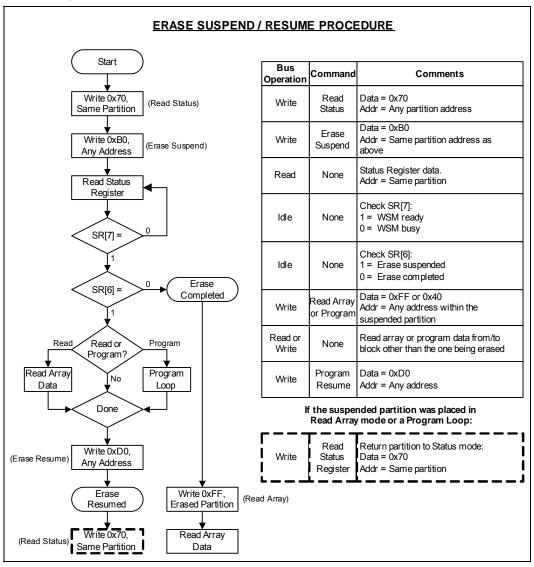

An industry-standard command sequence invokes program and erase automation. Each erase operation erases one block. The Erase Suspend feature allows system software to pause an erase cycle to read or program data in another block. Program Suspend allows system software to pause programming to read other locations. Data is programmed in word increments (16 bits).

The Intel StrataFlash<sup>®</sup> Embedded Memory P33 protection register allows unique flash device identification that can be used to increase system security. The individual Block Lock feature provides zero-latency block locking and unlocking. In addition, the Intel StrataFlash<sup>®</sup> Embedded Memory P33 may also pre-define main array space as One-Time Programmable (OTP).

## 2.1 Virtual Chip Enable Description

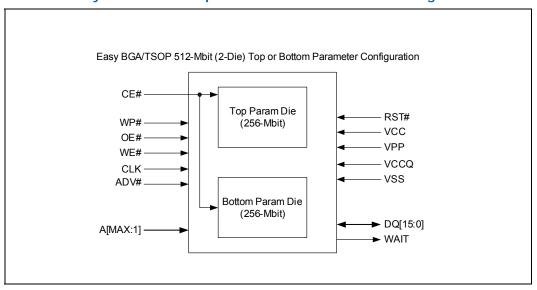

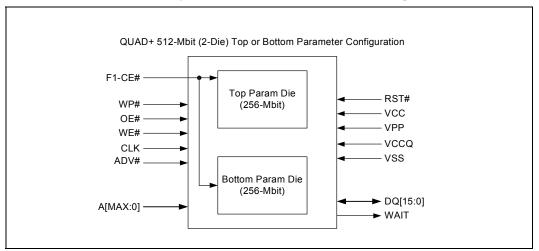

The Intel StrataFlash <sup>®</sup> Embedded Memory P33 512Mbit devices employ a Virtual Chip Enable which combines two 256-Mbit die with a common chip enable, F1-CE# for Quad+ packages or CE# for Easy BGA packages (refer to Figure 10 and Figure 11 for additional details). Address A24 (Quad+ package) or A25 (Easy BGA and TSOP package) is then used to select between the die pair with F1-CE# / CE# asserted depending upon the package option used. When chip enable is asserted and Quad+ A24 (EasyBGA A25) is low (V<sub>IL</sub>), The lower parameter die is selected; when chip enable is asserted and Quad+ A24 (EasyBGA A25) is high (V<sub>IH</sub>), the upper parameter die is selected. Refer to Table 1, "Flash Die Virtual Chip Enable Truth Table for 512Mbit Quad+ Package" and Table 2, "Flash Die Virtual Chip Enable Truth Table for 512Mbit TSOP / EasyBGA package" for additional details.

August 2006 Order Number: 314749-002US

## Table 1. Flash Die Virtual Chip Enable Truth Table for 512Mbit Quad+ Package

| Die Selected    | F1-CE# | A24 |

|-----------------|--------|-----|

| Lower Param Die | L      | L   |

| Upper Param Die | L      | Н   |

# Table 2. Flash Die Virtual Chip Enable Truth Table for 512Mbit TSOP / EasyBGA package

| Die Selected    | CE# | A25 |

|-----------------|-----|-----|

| Lower Param Die | L   | L   |

| Upper Param Die | L   | Н   |

August 2006 Order Number: 314749-002US www.DataSheet4U.com

# 3.0 Package Information

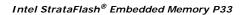

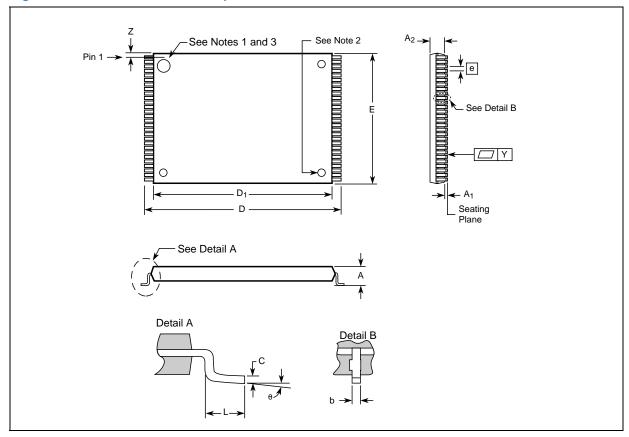

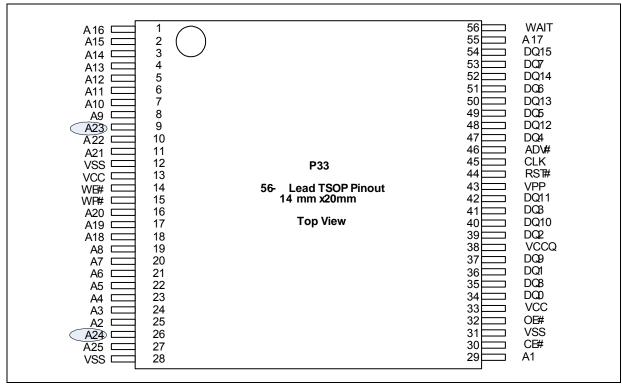

## 3.1 56-Lead TSOP Package

Figure 1. TSOP Mechanical Specifications

Table 3. TSOP Package Dimensions (Sheet 1 of 2)

| Product Information    | Symphol        |        | Millimeters Inches |        |       |        | Notes |       |

|------------------------|----------------|--------|--------------------|--------|-------|--------|-------|-------|

| Product Information    | Symbol         | Min    | Nom                | Max    | Min   | Nom    | Max   | Notes |

| Package Height         | Α              | -      | -                  | 1.200  | -     | -      | 0.047 |       |

| Standoff               | A <sub>1</sub> | 0.050  | -                  | -      | 0.002 | -      | -     |       |

| Package Body Thickness | A <sub>2</sub> | 0.965  | 0.995              | 1.025  | 0.038 | 0.039  | 0.040 |       |

| Lead Width             | b              | 0.100  | 0.150              | 0.200  | 0.004 | 0.006  | 0.008 |       |

| Lead Thickness         | С              | 0.100  | 0.150              | 0.200  | 0.004 | 0.006  | 0.008 |       |

| Package Body Length    | D <sub>1</sub> | 18.200 | 18.400             | 18.600 | 0.717 | 0.724  | 0.732 | 4     |

| Package Body Width     | E              | 13.800 | 14.000             | 14.200 | 0.543 | 0.551  | 0.559 | 4     |

| Lead Pitch             | е              | -      | 0.500              | -      | -     | 0.0197 | -     |       |

| Terminal Dimension     | D              | 19.800 | 20.00              | 20.200 | 0.780 | 0.787  | 0.795 |       |

| Lead Tip Length        | L              | 0.500  | 0.600              | 0.700  | 0.020 | 0.024  | 0.028 |       |

August 2006 Order Number: 314749-002US

#### TSOP Package Dimensions (Sheet 2 of 2) Table 3.

| Product Information       | Symbol |       | Millimeters |       |       | Notes |       |       |

|---------------------------|--------|-------|-------------|-------|-------|-------|-------|-------|

| Product Information       | Зуппон | Min   | Nom         | Max   | Min   | Nom   | Max   | Notes |

| Lead Count                | N      | -     | 56          | -     | -     | 56    | -     |       |

| Lead Tip Angle            | ý      | 0°    | 3°          | 5°    | 0°    | 3°    | 5°    |       |

| Seating Plane Coplanarity | Υ      | -     | -           | 0.100 | -     | -     | 0.004 |       |

| Lead to Package Offset    | Z      | 0.150 | 0.250       | 0.350 | 0.006 | 0.010 | 0.014 |       |

- Notes:

1.

2.

3.

4. One dimple on package denotes Pin 1. If two dimples, then the larger dimple denotes Pin 1. Pin 1 will always be in the upper left corner of the package, in reference to the product mark. Daisy Chain Evaluation Unit information is at Intel® Flash Memory Packaging Technology http://developer.intel.com/design/flash/packtech.

August 2006 Order Number: 314749-002US www.DataSheet4U.com

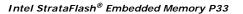

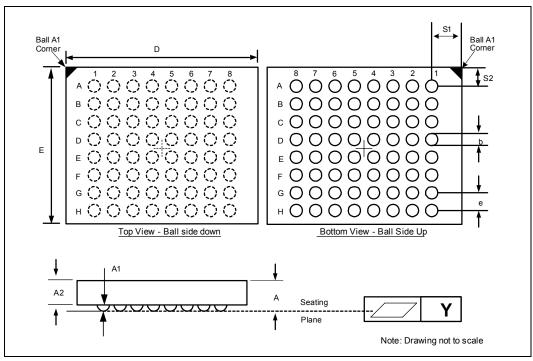

## 3.2 64-Ball Easy BGA Package

Figure 2. 64-Mbit and 128-Mbit Easy BGA Mechanical Specifications

Table 4. 64-Mbit and 128-Mbit Easy BGA Package Dimensions

| Due don't before attend            | Complete |       | Millimeter | s      |        | Inches |        | N1-4  |

|------------------------------------|----------|-------|------------|--------|--------|--------|--------|-------|

| Product Information                | Symbol   | Min   | Nom        | Max    | Min    | Nom    | Max    | Notes |

| Package Height                     | А        | -     | -          | 1.200  | -      | -      | 0.0472 |       |

| Ball Height                        | A1       | 0.250 | -          | -      | 0.0098 | -      | -      |       |

| Package Body Thickness             | A2       | -     | 0.780      | -      | -      | 0.0307 | -      |       |

| Ball (Lead) Width                  | b        | 0.330 | 0.430      | 0.530  | 0.0130 | 0.0169 | 0.0209 |       |

| Package Body Width                 | D        | 9.900 | 10.000     | 10.100 | 0.3898 | 0.3937 | 0.3976 | 1     |

| Package Body Length                | E        | 7.900 | 8.000      | 8.100  | 0.3110 | 0.3149 | 0.3189 | 1     |

| Pitch                              | [e]      | -     | 1.000      | -      | -      | 0.0394 | -      |       |

| Ball (Lead) Count                  | N        | -     | 64         | -      | -      | 64     | -      |       |

| Seating Plane Coplanarity          | Υ        | -     | -          | 0.100  | -      | -      | 0.0039 |       |

| Corner to Ball A1 Distance Along D | S1       | 1.400 | 1.500      | 1.600  | 0.0551 | 0.0591 | 0.0630 | 1     |

| Corner to Ball A1 Distance Along E | S2       | 0.400 | 0.500      | 0.600  | 0.0157 | 0.0197 | 0.0236 | 1     |

### Notes:

August 2006 Order Number: 314749-002US

<sup>1.</sup> Daisy Chain Evaluation Unit information is at Intel® Flash Memory Packaging Technology http://developer.intel.com/design/flash/packtech.

August 2006

www.DataSheet4U.com

Order Number: 314749-002US

Ball A1 Ball A1 Corner Corner D S1, 7 6 3 2 A 0 0 0 0 0 0 B 0 0 0 0 0 0 0 COOCOOOO  $\bullet \bigcirc \bigcirc \bigcirc \bigcirc \bigcirc \bigcirc \bigcirc \bigcirc \bigcirc \bigcirc$ Е F 0 0 0 0 0 0 0  $G \bigcirc O \bigcirc O \bigcirc O \bigcirc O \bigcirc O$ • 0 0 0 0 0 0 0 0 +00000000 H O O O O O O O Bottom View - Ball Side Up Top View - Ball side down Α1 Α2 Seating Plane Note: Drawing not to scale

Figure 3. 256-Mbit and 512-Mbit Easy BGA Mechanical Specifications

Table 5. 256-Mbit and 512-Mbit Easy BGA Package Dimensions

| Product Information                | Cumbal | 1      | Millimeter | s      |        | Inches |        | Netco |

|------------------------------------|--------|--------|------------|--------|--------|--------|--------|-------|

| Product Information                | Symbol | Min    | Nom        | Max    | Min    | Nom    | Max    | Notes |

| Package Height (256-Mbit)          | А      | -      | -          | 1.200  | -      | -      | 0.0472 |       |

| Package Height (512-Mbit)          | А      | -      | -          | 1.300  | -      | -      | 0.0512 |       |

| Ball Height                        | A1     | 0.250  | -          | -      | 0.0098 | -      | -      |       |

| Package Body Thickness (256-Mbit)  | A2     | -      | 0.780      | -      | -      | 0.0307 | -      |       |

| Package Body Thickness (512-Mbit)  | A2     | -      | 0.910      | -      | -      | 0.0358 | -      |       |

| Ball (Lead) Width                  | b      | 0.330  | 0.430      | 0.530  | 0.0130 | 0.0169 | 0.0209 |       |

| Package Body Width                 | D      | 9.900  | 10.000     | 10.100 | 0.3898 | 0.3937 | 0.3976 | 1     |

| Package Body Length                | E      | 12.900 | 13.000     | 13.100 | 0.5079 | 0.5118 | 0.5157 | 1     |

| Pitch                              | [e]    | -      | 1.000      | -      | -      | 0.0394 | -      |       |

| Ball (Lead) Count                  | N      | -      | 64         | -      | -      | 64     | -      |       |

| Seating Plane Coplanarity          | Υ      | -      | -          | 0.100  | -      | -      | 0.0039 |       |

| Corner to Ball A1 Distance Along D | S1     | 1.400  | 1.500      | 1.600  | 0.0551 | 0.0591 | 0.0630 | 1     |

| Corner to Ball A1 Distance Along E | S2     | 2.900  | 3.000      | 3.100  | 0.1142 | 0.1181 | 0.1220 | 1     |

### Notes:

Daisy Chain Evaluation Unit information is at Intel® Flash Memory Packaging Technology http://developer.intel.com/ design/flash/packtech.

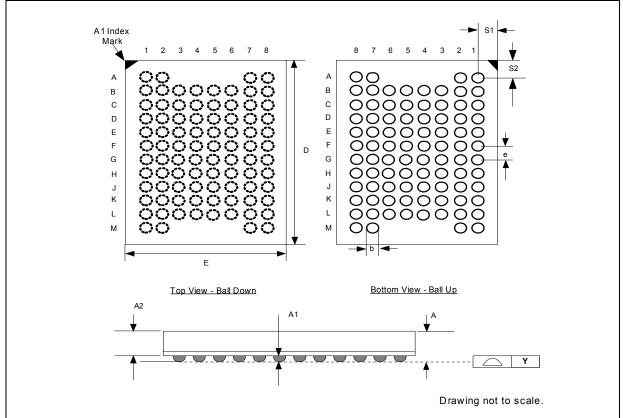

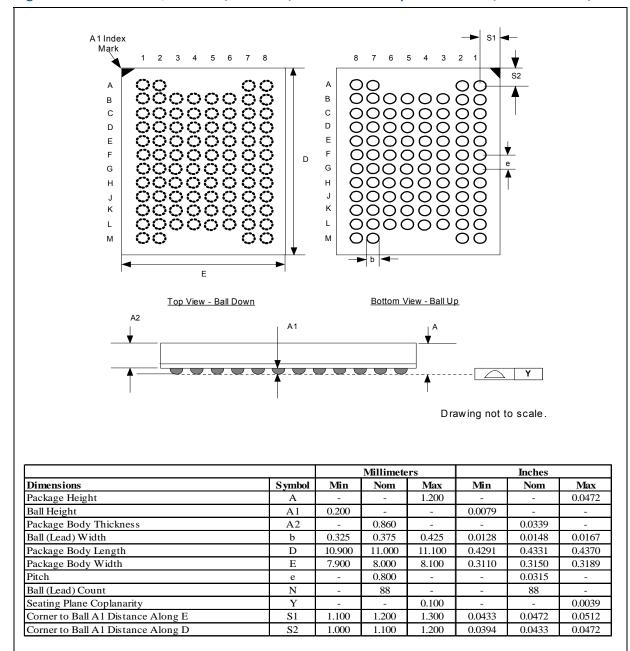

## 3.3 QUAD+ SCSP Packages

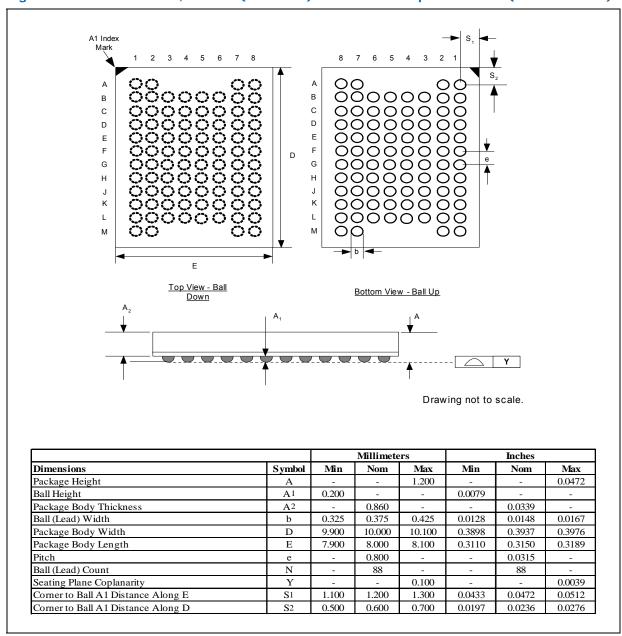

Figure 4. 64/128-Mbit, 88-ball (80 active) QUAD+ SCSP Specifications (8x10x1.2 mm)

August 2006 Order Number: 314749-002US Intel<sup>®</sup> P33 Flash Memory Datasheet 15 WWW.DataSheet4U.com

Figure 5. 256-Mbit, 88-ball (80 active) QUAD+ SCSP Specifications (8x11x1.0 mm)

Note: Dimensions A1, A2, and b are preliminary

|                                    |        |        | Millimete | ers    |        | Inches |        |

|------------------------------------|--------|--------|-----------|--------|--------|--------|--------|

| Dimensions                         | Symbol | Min    | Nom       | Max    | Min    | Nom    | Max    |

| Package Height                     | A      | -      | -         | 1.000  | -      | _      | 0.0394 |

| Ball Height                        | A1     | 0.117  | -         | -      | 0.0046 | _      | -      |

| Package Body Thickness             | A2     | -      | 0.740     | -      | -      | 0.0291 | -      |

| Ball (Lead) Width                  | b      | 0.300  | 0.350     | 0.400  | 0.0118 | 0.0138 | 0.0157 |

| Package Body Length                | D      | 10.900 | 11.00     | 11.100 | 0.4291 | 0.4331 | 0.4370 |

| Package Body Width                 | Е      | 7.900  | 8.00      | 8.100  | 0.3110 | 0.3150 | 0.3189 |

| Pitch                              | e      | -      | 0.80      | -      | -      | 0.0315 | -      |

| Ball (Lead) Count                  | N      | -      | 88        | -      | -      | 88     | -      |

| Seating Plane Coplanarity          | Y      | -      | -         | 0.100  | -      | -      | 0.0039 |

| Corner to Ball A1 Distance Along E | S1     | 1.100  | 1.200     | 1.300  | 0.0433 | 0.0472 | 0.0512 |

| Corner to Ball A1 Distance Along D | S2     | 1.000  | 1.100     | 1.200  | 0.0394 | 0.0433 | 0.0472 |

August 2006

Order Number: 314749-002US

www.DataSheet4U.com

Figure 6. 512-Mbit, 88-ball (80 active) QUAD+ SCSP Specifications (8x11x1.2 mm)

August 2006 Order Number: 314749-002US Intel<sup>®</sup> P33 Flash Memory Datasheet 17 WWW.DataSheet4U.com

August 2006

www.DataSheet4U.com

Order Number: 314749-002US

## **Ballout and Signal Descriptions**

### 4.1 **Signal Ballout**

Figure 7. 56-Lead TSOP Pinout (64/128/256/512-Mbit)

## Notes:

- A1 is the least significant address bit.

- A23 is valid for 128-Mbit densities and above; otherwise, it is a no connect (NC). A24 is valid for 256-Mbit densities; otherwise, it is a no connect (NC). A25 is valid for 512-Mbit densities; otherwise, it is a no connect (NC). 2.

- 3.

- 4.

- Synchronous burst read operation is currently not supported for the TSOP package. The synchronous read input signals (i.e. ADV# and CLK) should be tied off to support asynchronous reads. See Section 4.2, "Signal Descriptions" on page 21.

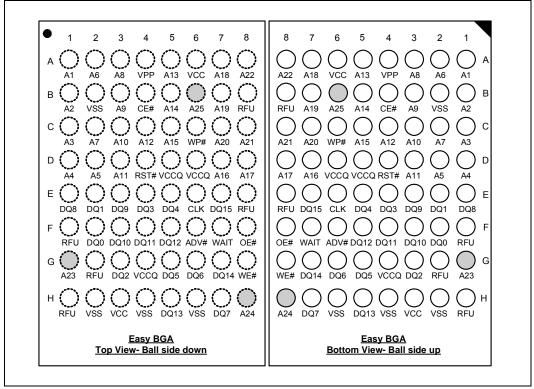

## Figure 8. 64-Ball Easy BGA Ballout (64/128/256/512-Mbit)

### Notes:

- A1 is the least significant address bit.

- 2. A23 is valid for 128-Mbit densities and above; otherwise, it is a no connect (NC).

- 3. A24 is valid for 256-Mbit densities and above; otherwise, it is a no connect (NC).

- 4. A25 is valid for 512-Mbit densities; otherwise, it is a no connect (NC).

August 2006 Order Number: 314749-002US Intel® P33 Flash Memory

Datasheet

19

www.DataSheet4U.com

August 2006 Order Number: 314749-002US www.DataSheet4U.com

Figure 9. 88-Ball (80-Active Ball) QUAD+ SCSP Ballout

| <u>Pin 1</u> | 1      | 2      | 3     | 4     | 5     | 6     | 7    | 8      |   |

|--------------|--------|--------|-------|-------|-------|-------|------|--------|---|

| Α            | DU     | DU     | Depop | Depop | Depop | Depop | DU   | DU     | Α |

| В            | A4     | A18    | A19   | vss   | vcc   | vcc   | A21  | A11    | В |

| С            | A5     | RFU    | A23   | VSS   | RFU   | CLK   | A22  | A12    | С |

| D            | А3     | A17    | A24   | VPP   | RFU   | RFLI  | А9   | A13    | D |

| E            | A2     | A7     | RFU   | WP#   | ADV#  | A20   | A10  | A15    | E |

| F            | A1     | A6     | rfu   | RST#  | WE#   | A8    | A14  | A16    | F |

| G            | Α0     | DQ8    | DQ2   | DQ10  | DQ5   | DQ13  | WAIT | F2-CE# | G |

| Н            | RFU    | DQ0    | DQ1   | DQ3   | DQ12  | DQ14  | DQ7  | F2-OE# | н |

| J            | RFU    | F1-OE# | DQ9   | DQ11  | DQ4   | DQ6   | DQ15 | VCCQ   | J |

| K            | F1-CE# | RFU    | RFU   | RFU   | RFU   | vcc   | VCCQ | RFU    | К |

| L            | vss    | vss    | VCCQ  | vcc   | vss   | vss   | vss  | vss    | L |

| М            | DU     | DU     | Depop | Depop | Depop | Depop | DU   | DU     | М |

|              | 1      | 2      | 3     | 4     | 5     | 6     | 7    | 8      |   |

### Notes:

- 1. 2.

- A22 is valid for 128-Mbit densities and above; otherwise, it is a no connect (NC). A23 is valid for 256-Mbit densities and above; otherwise, it is a no connect (NC). A24 is valid for 512-Mbit densities and above; otherwise, it is a no connect (NC). 3.

- 4. F2-CE# and F2-OE# are no connects (NC).

## 4.2 Signal Descriptions

This section has signal descriptions for the various Intel StrataFlash  $^{\circledR}$  Embedded Memory P33 packages.

Table 6. TSOP and Easy BGA Signal Descriptions (Sheet 1 of 2)

| Symbol   | Туре             | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

|----------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| A[MAX:1] | Input            | ADDRESS INPUTS: Device address inputs. 64-Mbit: A[22:1]; 128-Mbit: A[23:1]; 256-Mbit: A[24:1]; 512-Mbit: A[25:1]. Note: The virtual selection of the 256-Mbit "Top parameter" die in the dual-die 512-Mbit configuration is accomplished by setting A[25] high (V <sub>IH</sub> )                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

| DQ[15:0] | Input/<br>Output | DATA INPUT/OUTPUTS: Inputs data and commands during write cycles; outputs data during memory, Status Register, Protection Register, and Read Configuration Register reads. Data balls float when the CE# or OE# are deasserted. Data is internally latched during writes.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| ADV#     | Input            | ADDRESS VALID: Active low input. During synchronous read operations, addresses are latched of the rising edge of ADV#, or on the next valid CLK edge with ADV# low, whichever occurs first. In asynchronous mode, the address is latched when ADV# going high or continuously flows through if ADV# is held low.  WARNING: Designs not using ADV# must tie it to VSS to allow addresses to flow through.                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

| CE#      | Input            | FLASH CHIP ENABLE: Active low input. CE# low selects the associated flash memory die. When asserted, flash internal control logic, input buffers, decoders, and sense amplifiers are active. When deasserted, the associated flash die is deselected, power is reduced to standby levels, data and WAIT outputs are placed in high-Z state.  WARNING: All chip enables must be high when device is not in use.                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

| CLK      | Input            | <b>CLOCK:</b> Synchronizes the device with the system's bus frequency in synchronous-read mode. During synchronous read operations, addresses are latched on the rising edge of ADV#, or on the next valid CLK edge with ADV# low, whichever occurs first.  WARNING: Designs not using CLK for synchronous read mode must tie it to VCCQ or VSS.                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

| OE#      | Input            | <b>OUTPUT ENABLE:</b> Active low input. OE# low enables the device's output data buffers during read cycles. OE# high places the data outputs and WAIT in High-Z.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

| RST#     | Input            | <b>RESET:</b> Active low input. RST# resets internal automation and inhibits write operations. This provides data protection during power transitions. RST# high enables normal operation. Exit from reset places the device in asynchronous read array mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| WAIT     | Output           | <ul> <li>WAIT: Indicates data valid in synchronous array or non-array burst reads. Read Configuration Register bit 10 (RCR[10], WT) determines its polarity when asserted. WAIT's active output is V<sub>OL</sub> or V<sub>OH</sub> when CE# and OE# are V<sub>IL</sub>. WAIT is high-Z if CE# or OE# is V<sub>IH</sub>.</li> <li>In synchronous array or non-array read modes, WAIT indicates invalid data when asserted and valid data when deasserted.</li> <li>In asynchronous page mode, and all write modes, WAIT is deasserted.</li> </ul>                                                                                                                                                                                                                                                                    |  |  |  |

| WE#      | Input            | <b>WRITE ENABLE:</b> Active low input. WE# controls writes to the device. Address and data are latched on the rising edge of WE#.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

| WP#      | Input            | WRITE PROTECT: Active low input. WP# low enables the lock-down mechanism. Blocks in lock-down cannot be unlocked with the Unlock command. WP# high overrides the lock-down function enabling blocks to be erased or programmed using software commands.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| VPP      | Power/<br>Input  | Erase and Program Power: A valid voltage on this pin allows erasing or programming. Memory contents cannot be altered when $V_{PP} \leq V_{PPLK}$ . Block erase and program at invalid $V_{PP}$ voltages should not be attempted. Set $V_{PP} = V_{PPL}$ for in-system program and erase operations. To accommodate resistor or diode drops from the system supply, the $V_{IH}$ level of $V_{PP}$ can be as low as $V_{PPL}$ min. $V_{PP}$ must remain above $V_{PPL}$ min to perform in-system flash modification. VPP may be 0 V during read operations. $V_{PPH}$ can be applied to main blocks for 1000 cycles maximum and to parameter blocks for 2500 cycles. VPP can be connected to 9 V for a cumulative total not to exceed 80 hours. Extended use of this pin at 9 V may reduce block cycling capability. |  |  |  |

| VCC      | Power            | <b>Device Core Power Supply:</b> Core (logic) source voltage. Writes to the flash array are inhibited when $V_{CC} \le V_{LKO}$ . Operations at invalid $V_{CC}$ voltages should not be attempted.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| VCCQ     | Power            | Output Power Supply: Output-driver source voltage.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| VSS      | Power            | Ground: Connect to system ground. Do not float any VSS connection.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

August 2006 Order Number: 314749-002US Intel® P33 Flash Memory Datasheet 21 www.DataSheet4U.com

August 2006 Order Number: 314749-002US www.DataSheet4U.com

## Table 6. TSOP and Easy BGA Signal Descriptions (Sheet 2 of 2)

| Symbol | Туре | Name and Function                                                                                                                                                |  |  |

|--------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| RFU    | _    | Reserved for Future Use: Reserved by Intel for future device functionality and enhancement. These should be treated in the same way as a Do Not Use (DU) signal. |  |  |

| DU     | _    | Do Not Use: Do not connect to any other signal, or power supply; must be left floating.                                                                          |  |  |

| NC     | _    | No Connect: No internal connection; can be driven or floated.                                                                                                    |  |  |

## Table 7. QUAD+ SCSP Signal Descriptions (Sheet 1 of 2)

| Symbol           | Туре             | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

|------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| A[MAX:0]         | Input            | ADDRESS INPUTS: Device address inputs. 64-Mbit: A[21:0]; 128-Mbit: A[22:0]; 256-Mbit: A[23:0]; 512-Mbit: A[24:0]. Note: The virtual selection of the 256-Mbit "Top parameter" die in the dual-die 512-Mbit configuration is accomplished by setting A[24] high (V <sub>IH</sub> ).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

| DQ[15:0]         | Input/<br>Output | <b>DATA INPUT/OUTPUTS:</b> Inputs data and commands during write cycles; outputs data during memory, Status Register, Protection Register, and Read Configuration Register reads. Data balls float when the CE# or OE# are deasserted. Data is internally latched during writes.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| ADV#             | Input            | ADDRESS VALID: Active low input. During synchronous read operations, addresses are latched of the rising edge of ADV#, or on the next valid CLK edge with ADV# low, whichever occurs first. In asynchronous mode, the address is latched when ADV# going high or continuously flows throug if ADV# is held low.  WARNING: Designs not using ADV# must tie it to VSS to allow addresses to flow through.                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

| F1-CE#<br>F2-CE# | Input            | FLASH CHIP ENABLE: Active low input. CE# low selects the associated flash memory die. When asserted, flash internal control logic, input buffers, decoders, and sense amplifiers are active. When deasserted, the associated flash die is deselected, power is reduced to standby levels, data and WAIT outputs are placed in high-Z state. Note: F2-CE# is a NC for this part  See Figure 11, "512-Mbit QUAD+ SCSP Top or Bottom Parameter Block Diagram" on page 24 for CE# assignments.  WARNING: All chip enables must be high when device is not in use.                                                                                                                                                                                                                                                        |  |  |  |  |

| CLK              | Input            | CLOCK: Synchronizes the device with the system's bus frequency in synchronous-read mode. During synchronous read operations, addresses are latched on the rising edge of ADV#, or on the next valid CLK edge with ADV# low, whichever occurs first.  WARNING: Designs not using CLK for synchronous read mode must tie it to VCCQ or VSS.                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

| F1-OE#<br>F2-OE# | Input            | <b>OUTPUT ENABLE:</b> Active low input. OE# low enables the device's output data buffers during reac cycles. OE# high places the data outputs and WAIT in High-Z. Note: F2-OE# is a NC for this part. F1-OE# and F2-OE# should be tied together for all densities.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

| RST#             | Input            | <b>RESET:</b> Active low input. RST# resets internal automation and inhibits write operations. This provides data protection during power transitions. RST# high enables normal operation. Exit from reset places the device in asynchronous read array mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| WAIT             | Output           | <ul> <li>WAIT: Indicates data valid in synchronous array or non-array burst reads. Read Configuration Register bit 10 (RCR[10], WT) determines its polarity when asserted. WAIT's active output is V<sub>OL</sub> or V<sub>OH</sub> when CE# and OE# are V<sub>IL</sub>. WAIT is high-Z if CE# or OE# is V<sub>IH</sub>.</li> <li>In synchronous array or non-array read modes, WAIT indicates invalid data when asserted and valid data when deasserted.</li> <li>In asynchronous page mode, and all write modes, WAIT is deasserted.</li> </ul>                                                                                                                                                                                                                                                                    |  |  |  |  |

| WE#              | Input            | WRITE ENABLE: Active low input. WE# controls writes to the device. Address and data are latched on the rising edge of WE#.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

| WP#              | Input            | WRITE PROTECT: Active low input. WP# low enables the lock-down mechanism. Blocks in lock-down cannot be unlocked with the Unlock command. WP# high overrides the lock-down function enabling blocks to be erased or programmed using software commands.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

| VPP              | Power/<br>Input  | Erase and Program Power: A valid voltage on this pin allows erasing or programming. Memory contents cannot be altered when $V_{pp} \leq V_{PPLK}$ . Block erase and program at invalid $V_{pp}$ voltages should not be attempted. Set $V_{pp} = V_{ppL}$ for in-system program and erase operations. To accommodate resistor or diode drops from the system supply, the $V_{IH}$ level of $V_{pp}$ can be as low as $V_{ppL}$ min. $V_{pp}$ must remain above $V_{ppL}$ min to perform in-system flash modification. VPP may be 0 V during read operations. $V_{ppH}$ can be applied to main blocks for 1000 cycles maximum and to parameter blocks for 2500 cycles. VPP can be connected to 9 V for a cumulative total not to exceed 80 hours. Extended use of this pin at 9 V may reduce block cycling capability. |  |  |  |  |

## Intel StrataFlash® Embedded Memory P33

## Table 7. QUAD+ SCSP Signal Descriptions (Sheet 2 of 2)

| Symbol | Туре  | Name and Function                                                                                                                                                                                  |  |  |  |

|--------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| vcc    | Power | <b>Pevice Core Power Supply:</b> Core (logic) source voltage. Writes to the flash array are inhibited when $V_{CC} \le V_{LKO}$ . Operations at invalid $V_{CC}$ voltages should not be attempted. |  |  |  |

| VCCQ   | Power | Output Power Supply: Output-driver source voltage.                                                                                                                                                 |  |  |  |

| VSS    | Power | Ground: Connect to system ground. Do not float any VSS connection.                                                                                                                                 |  |  |  |

| RFU    | _     | Reserved for Future Use: Reserved by Intel for future device functionality and enhancement. These should be treated in the same way as a Do Not Use (DU) signal.                                   |  |  |  |

| DU     | _     | Do Not Use: Do not connect to any other signal, or power supply; must be left floating.                                                                                                            |  |  |  |

| NC     | _     | No Connect: No internal connection; can be driven or floated.                                                                                                                                      |  |  |  |

August 2006 Order Number: 314749-002US Intel® P33 Flash Memory Datasheet 23 WWW.DataSheet4U.com

August 2006 Order Number: 314749-002US www.DataSheet4U.com

## 4.3 **Dual Die SCSP Configurations**

Figure 10. 512-Mbit Easy BGA / TSOP Top or Bottom Parameter Block Diagram

Figure 11. 512-Mbit QUAD+ SCSP Top or Bottom Parameter Block Diagram

## 4.4 Memory Maps

Table 8 through Table 10 show the Intel StrataFlash® Embedded Memory P33 maps. The memory array is divided into multiple 8-Mbit Programming Regions (see Section 11.0, "Programming Operations" on page 59).

Table 8. Discrete Top Parameter Memory Maps (all packages)

|                                 | Size<br>(KB) | Blk | 64-Mbit         |

|---------------------------------|--------------|-----|-----------------|

|                                 | 32           | 66  | 3FC000 - 3FFFFF |

| ing                             | :            | ::  | :               |

| One<br>Programming<br>Region    | 32           | 63  | 3F0000 - 3F3FFF |

| Or<br>gra<br>Reg                | 128          | 62  | 3E0000 - 3EFFFF |

| Pro                             | :            | :   | :               |

|                                 | 128          | 56  | 380000 - 38FFFF |

| ō                               | 128          | 55  | 370000 - 37FFFF |

| n<br>min<br>ns                  | 128          | 54  | 360000 - 36FFFF |

| eve<br>am                       | ÷            | :   | i               |

| Seven<br>Programming<br>Regions | 128          | 1   | 010000 - 01FFFF |

| ď                               | 128          | 0   | 000000 - 00FFFF |

|                                   | Size<br>(KB) | Blk | 128-Mbit        |

|-----------------------------------|--------------|-----|-----------------|

|                                   | 32           | 130 | 7FC000 - 7FFFFF |

| ing                               | :            | :   | i i             |

| One<br>Programming<br>Region      | 32           | 127 | 7F0000 - 7F3FFF |

| Or<br>gra<br>Reg                  | 128          | 126 | 7E0000 - 7EFFFF |

| Pro                               | :            | :   | ÷               |

|                                   | 128          | 120 | 780000 - 78FFFF |

| 0                                 | 128          | 119 | 770000 - 77FFFF |

| m<br>min<br>ns                    | 128          | 118 | 760000 - 76FFFF |

| Fifteen<br>grammi<br>Regions      | :            | :   | i i             |

| Fifteen<br>Programming<br>Regions | 128          | 1   | 010000 - 01FFFF |

| ٩                                 | 128          | 0   | 000000 - 00FFFF |

|                                      | Size<br>(KB) | Blk | 256-Mbit        |

|--------------------------------------|--------------|-----|-----------------|

|                                      | 32           | 258 | FFC000 - FFFFFF |

| ing                                  | :            | :   | :               |

| One<br>Programming<br>Region         | 32           | 255 | FF0000 - FF3FFF |

| Or<br>gra<br>Reg                     | 128          | 254 | FE0000 - FEFFFF |

| Pro                                  | ÷            | :   |                 |

|                                      | 128          | 248 | F80000 - F8FFFF |

| g                                    | 128          | 247 | F70000 - F7FFFF |

| One<br>min<br>ns                     | 128          | 246 | F60000 - F6FFFF |

| ty-(<br>am                           | ÷            | ::  | ••••            |

| Thirty-One<br>Programming<br>Regions | 128          | 1   | 010000 - 01FFFF |

| <u> </u>                             | 128          | 0   | 000000 - 00FFFF |

August 2006 Order Number: 314749-002US Intel® P33 Flash Memory Datasheet 25 WWW.DataSheet4U.com

## Table 9. Discrete Bottom Parameter Memory Maps (all packages)

|                                 | Size<br>(KB) | Blk | 64-Mbit         |

|---------------------------------|--------------|-----|-----------------|

| g                               | 128          | 66  | 3F0000 - 3FFFFF |

| Seven<br>Programming<br>Regions | 128          | 65  | 3E0000 - 3EFFFF |

| Seven<br>grammi<br>Regions      | :            | :   | :               |

| S<br>rogr<br>Re                 | 128          | 12  | 090000 - 09FFFF |

| Ь                               | 128          | 11  | 080000 - 08FFFF |

|                                 | 128          | 10  | 070000 - 07FFFF |

| ing                             | ÷            | :   | i               |

| One<br>ramm<br>egion            | 128          | 4   | 010000 - 01FFFF |

| Or<br>gra<br>Reg                | 32           | 3   | 00C000 - 00FFFF |

| One<br>Programming<br>Region    | ÷            | :   | :               |

|                                 | 32           | 0   | 000000 - 003FFF |

|                                   | Size<br>(KB) | Blk | 128-Mbit        |

|-----------------------------------|--------------|-----|-----------------|

| g                                 | 128          | 130 | 7F0000 - 7FFFFF |

| Fifteen<br>Programming<br>Regions | 128          | 129 | 7E0000 - 7EFFFF |

| Fifteen<br>grammi<br>Regions      | :            | :   | i i             |

| Fi<br>rogr<br>Re                  | 128          | 12  | 090000 - 09FFFF |

| P                                 | 128          | 11  | 080000 - 08FFFF |

|                                   | 128          | 10  | 070000 - 07FFFF |

| ing                               | :            | :   | :               |

| One<br>Programming<br>Region      | 128          | 4   | 010000 - 01FFFF |

| One<br>gramm<br>Region            | 32           | 3   | 00C000 - 00FFFF |

| Pro                               | :            | :   | :               |

|                                   | 32           | 0   | 000000 - 003FFF |

|                                      | Size<br>(KB) | Blk | 256-Mbit        |

|--------------------------------------|--------------|-----|-----------------|

| g                                    | 128          | 258 | FF0000 - FFFFFF |

| One<br>min<br>ns                     | 128          | 257 | FE0000 - FEFFFF |

| Thirty-One<br>Programming<br>Regions | :            | :   | :               |

| Thir<br>rogr<br>Re                   | 128          | 12  | 090000 - 09FFFF |

| _ <u>P</u>                           | 128          | 11  | 080000 - 08FFFF |

|                                      | 128          | 10  | 070000 - 07FFFF |

| ing                                  | :            | :   | :               |

| One<br>ramm<br>egion                 | 128          | 4   | 010000 - 01FFFF |

| One<br>Programming<br>Region         | 32           | 3   | 00C000 - 00FFFF |

| Pro                                  | :            | :   | :               |

|                                      | 32           | 0   | 000000 - 003FFF |

*Note:* The Dual-Die memory map are the same for both parameter options.

Table 10. 512-Mbit Top and Bottom Parameter Memory Map (Easy BGA, TSOP, and QUAD+ SCSP)

|                      |              | 512-Mk | oit Flash (2x256-Mbit w/ 1CE) |

|----------------------|--------------|--------|-------------------------------|

| Die Stack Config     | Size<br>(KB) | Blk    | Address Range                 |

|                      | 32           | 517    | 1FFC000 - 1FFFFFF             |

|                      | :            | :      | ÷                             |

| 256-Mbit             | 32           | 514    | 1FF0000 - 1FF3FFF             |

| Top Parameter Die    | 128          | 513    | 1FE0000 - 1FEFFFF             |

|                      | ÷            | i.     | :                             |

|                      | 128          | 259    | 1000000 - 100FFFF             |

|                      |              |        |                               |

|                      | 128          | 258    | FF0000 - FFFFFF               |

|                      | :            | :      | :                             |

| 256-Mbit             | 128          | 4      | 010000 - 01FFFF               |

| Bottom Parameter Die | 32           | 3      | 00C000 - 00FFFF               |

|                      | :            | :      | :                             |

|                      | 32           | 0      | 000000 - 003FFF               |

Note: Refer to 256-Mbit Memory Map (Table 8 and Table 9) for Programming Region information.

August 2006 Order Number: 314749-002US

August 2006

www.DataSheet4U.com

Order Number: 314749-002US

## **Maximum Ratings and Operating Conditions**

### 5.1 **Absolute Maximum Ratings**

Stressing the device beyond the "Absolute Maximum Ratings" may cause permanent Warning: damage. These are stress ratings only.

#### Table 11. **Absolute Maximum Ratings**

| Parameter                               | Maximum Rating    | Notes |

|-----------------------------------------|-------------------|-------|

| Temperature under bias                  | -40 °C to +85 °C  |       |

| Storage temperature                     | -65 °C to +125 °C |       |

| Voltage on any signal (except VCC, VPP) | -0.5 V to +4.1 V  | 1     |

| VPP voltage                             | -0.2 V to +10 V   | 1,2,3 |

| VCC voltage                             | -0.2 V to +4.1 V  | 1     |

| VCCQ voltage                            | -0.2 V to +4.1 V  | 1     |

| Output short circuit current            | 100 mA            | 4     |

### Notes:

- Voltages shown are specified with respect to  $V_{SS}$ . Minimum DC voltage is -0.5 V on input/output signals and -0.2 V on  $V_{CC}$ ,  $V_{CCQ}$ , and  $V_{PP}$  During transitions, this level may undershoot to -2.0 V for periods less than 20 ns. Maximum DC voltage on  $V_{CC}$  is  $V_{CC} + 0.5$  V, which, during transitions, may overshoot to  $V_{CC} + 2.0$  V for periods less than 20 ns. Maximum DC voltage on input/output signals and  $V_{CCQ}$  is  $V_{CCQ} + 0.5$  V, which, during transitions, may overshoot to  $V_{CCQ} + 2.0$  V for periods less than 20 ns. than 20 ns.

- Maximum DC voltage on  $V_{pp}$  may overshoot to +11.5 V for periods less than 20 ns. Program/erase voltage is typically 2.3 V 3.6 V. 9.0 V can be applied for 80 hours maximum total, to any blocks for 1000 cycles maximum. 9.0 V program/erase voltage may reduce block cycling

- 4. Output shorted for no more than one second. No more than one output shorted at a time.

### **Operating Conditions** 5.2

Operation beyond the "Operating Conditions" is not recommended and extended exposure beyond the "Operating Conditions" may affect device reliability. Note:

#### **Operating Conditions** Table 12.

| Symbol           | Parameter                                    | Min                | Max     | Units | Notes  |   |

|------------------|----------------------------------------------|--------------------|---------|-------|--------|---|

| T <sub>C</sub>   | Operating Temperature                        | 64Mb - 512Mb       |         | +85   | °C     | 1 |

| V <sub>CC</sub>  | VCC Supply Voltage                           | 2.3                | 3.6     |       |        |   |

| V                | I/O Supply Voltage                           | CMOS inputs        | 2.3     | 3.6   |        |   |

| V <sub>CCQ</sub> | 170 Supply Voltage                           | TTL inputs         | 2.4     | 3.6   | V      |   |

| V <sub>PPL</sub> | V <sub>PP</sub> Voltage Supply (Logic Level) | 1.5                | 3.6     |       |        |   |

| $V_{PPH}$        | Factory word programming V <sub>PP</sub>     |                    | 8.5     | 9.5   |        |   |

| t <sub>PPH</sub> | Maximum VPP Hours                            | $V_{PP} = V_{PPH}$ | -       | 80    | Hours  | 2 |

| Block            | Main and Parameter Blocks                    | $V_{PP} = V_{PPL}$ | 100,000 | -     |        | 2 |

| Erase            | Main Blocks                                  | $V_{PP} = V_{PPH}$ | -       | 1000  | Cycles |   |

| Cycles           | Parameter Blocks                             | -                  | 2500    |       |        |   |

## Notes:

August 2006 Order Number: 314749-002US

Intel® P33 Flash Memory Datasheet www.DataSheet4U.com

$T_{C}$  = Case Temperature. In typical operation VPP program voltage is  $V_{PPL}$ .

August 2006 Order Number: 314749-002US www.DataSheet4U.com

# 6.0 Electrical Specifications

## 6.1 DC Current Characteristics

Table 13. DC Current Characteristics (Sheet 1 of 2)

| Sym                                                            | Parameter                                                                                                             |                                      |                           | Inp<br>(V <sub>C</sub> (<br>2.3 V | IOS<br>outs<br>- 3.6 | (V <sub>C</sub><br>2.4 V | nputs<br>co =<br>' - 3.6 | Unit                                                                                                                                      | Test Conditions                                                                                                                               |                                                                                                                                     | Notes |

|----------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|--------------------------------------|---------------------------|-----------------------------------|----------------------|--------------------------|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|-------|

|                                                                |                                                                                                                       |                                      |                           | Тур                               | Max                  | Тур                      | Max                      |                                                                                                                                           |                                                                                                                                               |                                                                                                                                     |       |

| ILI                                                            | Input Load Current                                                                                                    |                                      | -                         | ±1                                | -                    | ±2                       | μΑ                       | V <sub>CC</sub> = V <sub>CC</sub> Max<br>V <sub>CCQ</sub> = V <sub>CCQ</sub> Max<br>V <sub>IN</sub> = V <sub>CCQ</sub> or V <sub>SS</sub> |                                                                                                                                               | 1                                                                                                                                   |       |

| I <sub>LO</sub>                                                | Output<br>Leakage<br>Current                                                                                          | DQ[15:0], \                          | WAIT                      | -                                 | ±1                   | -                        | ±10                      | μΑ                                                                                                                                        | $V_{CC} = V_{CC}Max$ $V_{CCQ} = V_{CCQ}Max$ $V_{IN} = V_{CCQ} \text{ or } V_{SS}$                                                             |                                                                                                                                     | ı     |

|                                                                |                                                                                                                       |                                      | 64-Mbit                   | 35                                | 135                  | 35                       | 200                      |                                                                                                                                           | ., ., .,                                                                                                                                      |                                                                                                                                     |       |

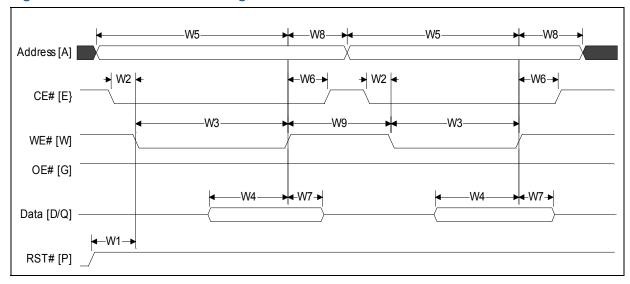

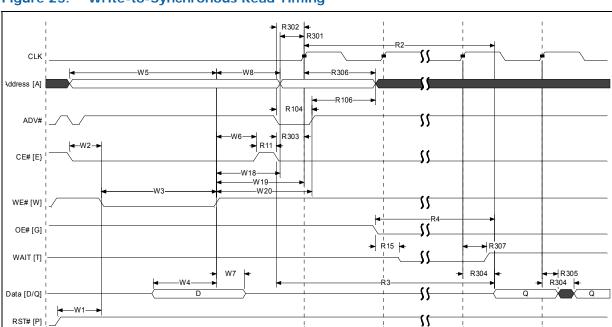

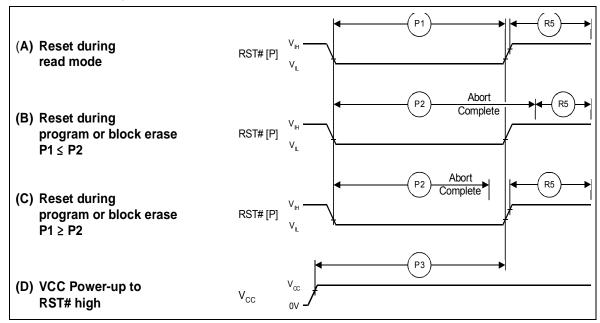

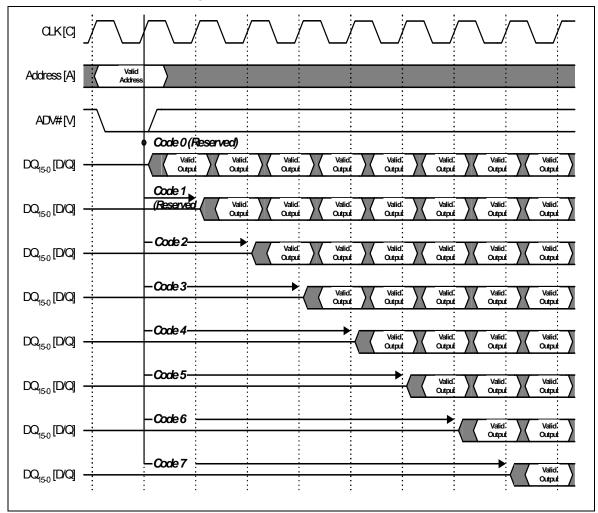

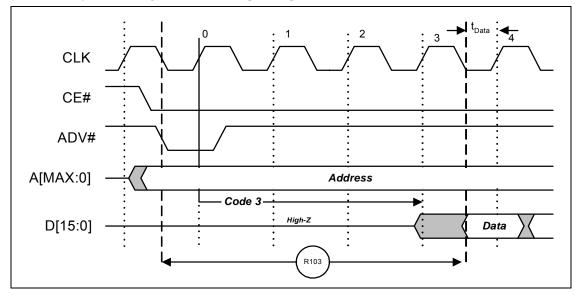

|                                                                |                                                                                                                       |                                      | 128-Mbit                  | 45                                | 155                  | 45                       | 220                      |                                                                                                                                           | $V_{CC} = V_{CC}Max$<br>$V_{CCQ} = V_{CCQ}N$                                                                                                  | lax                                                                                                                                 |       |