3 1 1992

# 2046 486DX/486SX/386DX Single Chip AT

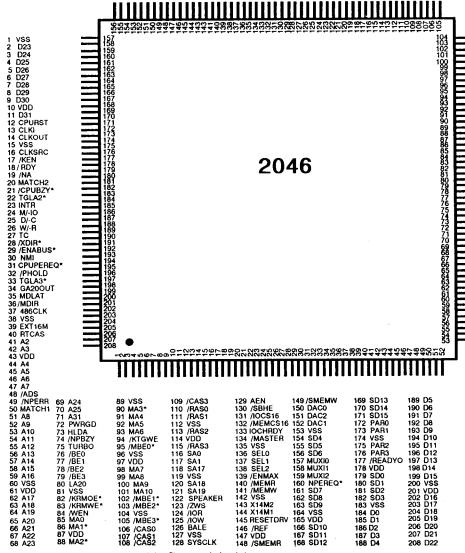

The ACC Micro 2046 single chip AT is designed for system designers to build a high performance 486DX/486SX/386DX AT systems. The 2046 single chip AT supports a local CPU bus, a system memory bus, and compatible AT buses. The AT bus clock can be synchronous or asynchronous to the CPU clock to support compatible AT bus timing. The built-in peripheral controller and on chip direct mapped cache controller add flexibility for designers to design high performance systems for different requirements.

#### Features

- 100% IBM PC/AT compatible

- \* Supports 486DX up to 50 Mhz

- Supports 486SX and 487SX

- Supports Intel Low Power 486DX/SX

- Supports 386DX up to 40 MHz

- Supports 387 and Weitek 4167/3167 numerical coprocessors

- Supports 1x or 2x system clock

- Integrated flexible direct mapped cache controller for up to 2048KB

- Supports posted write or write-through cache operation

- Supports 3 programmable non-cacheable ranges

- Supports 64 MB DMA address space

- \* Supports one to four memory banks of 32 bit DRAM using 256K,1M or 4M DRAMs allowing 64 Mbytes on system board.

- Operates with page mode or two/four way page interleaved mode

- \* Programmable DRAM timing parameters

- \* Programmable slow refresh

- Supports hidden refresh

- \* Support Dynamic Memory remapping

- Unused RAS and CAS lines can be disabled

- Supports shadow RAM for video and system BIOS

- Supports 8 or 16 bit wide BIOS ROMs in 128K or 64K EPROM space

- Supports single ROM

- \* Supports 512K ROM size

- Middle BIOS can be disabled

- \* Bus "quiet" mode assures that slot bus signal lines are driven only during slot accesses

- Port B and NMI logic

- Internal switching and programmable CLK2 for sleep mode operation (can be divided by 2/4/8/16)

- \* Fast reset/Fast gate A20 (Port 92)

- Support for PC/AT compatible and turbo modes

- Independent ISA Bus control

- Parity generation and detection logic

- Integrated Peripheral Functions: 2x8237, 2 x 8259, 1 x 8254.

- Bus conversion between D.SD and XD.

- Data latches and buffers included

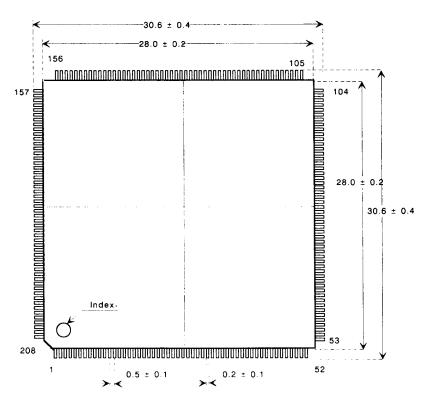

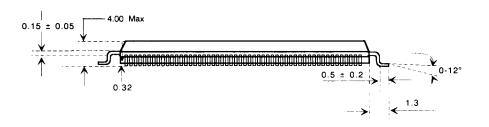

- 208-pin PQFP device

Rev.1.2 ACC Microelectronics Corporation 2500 Augustine Dr. Santa Clara, CA 95054 1

Phone: (408) 980-0622 FAX: (408) 980-0626 Copyright 1992 ACC Microelectronics Corporation

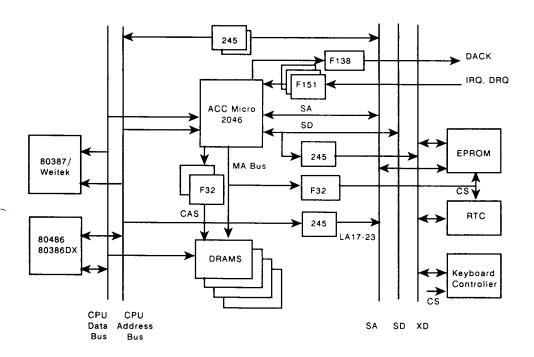

# 2046 System Block Diagram 486/386DX Without Cache Application

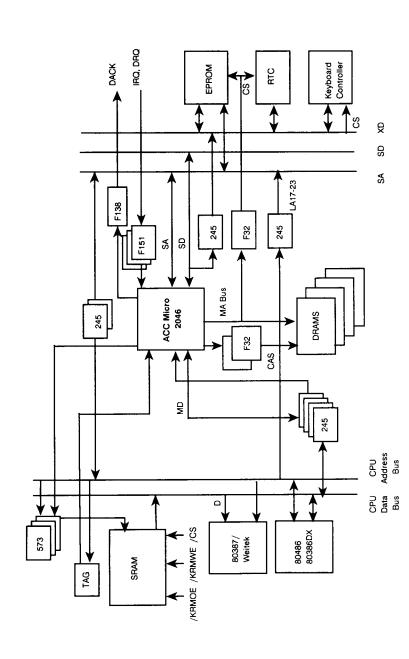

486/386DX with Cache Application 2046 System Block Diagram

2046

# **Functional Description**

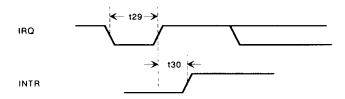

## Interrupt Controllers

There are two programmable interrupt controllers for the 2046. They are fully compatible with Intel's 8259 controller, providing up to 15 interrupt sources (14 external and 1 internal). The internal line connects to the 8254 Counter 0 output.

These interrupt controllers prioritize interrupt requests to the CPU.

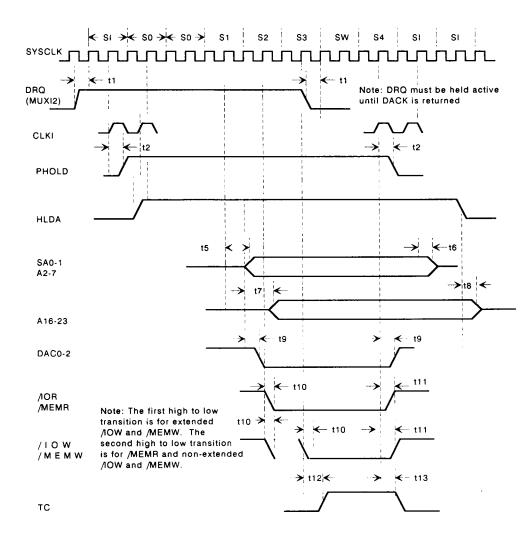

#### DMA

The 2046 has two DMA controllers, compatible with the Intel 8237, which provide a total of seven external DMA channels.

Combined with the Memory Mapper, each DMA channel has a 24-bit address output to access data throughout the 64 megabyte system address space. Channel 0 through channel 3 support 8-bit peripherals, transferring data to or from an 8 or 16-bit memory. Each channel can transfer data in 64 Kbyte pages. Channel 4 is used for cascading and is not available externally. Channel 5 through channel 7 support 16-bit I/O adapters, transferring data a word at a time. These channels can transfer in 128 Kbyte pages.

All address latching functions for DMA operation are done inside the 2046. Configuration register 0Ah, bit 1, and bit 0, provide address bits 24 and 25 for 64M Byte DMA address.

#### Features include

- Address increment or decrement.

- Seven independent DMA channels with independent auto initialization for each channel

- Each DMA request can be controlled individually to enable or disable.

## **Memory Mapper**

The 2046 has a built-in equivalent logic to the 74LS612, generating the upper address bits during a DMA cycle.

8237

# Source Memory Mapper (for DMA Channels 0 - 3)

Address A23.... A16 A15.... A0

(for DMA Channels 5 - 7)

A23 .... A17 A16.... A1 Address

# Timer/Counter

The 2046 provides three internal counters which are compatible with the 8254. The clock input for each counter is tied to a clock of 1.19 MHz, which is derived by dividing the 14.318 MHz

# ACC Micro "

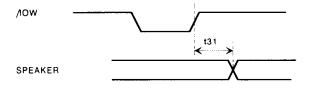

crystal input by 12. The output of Counter 0 is connected to the IRQ0 input of interrupt controller 1. Counter 1 initiates a refresh cycle and Counter 2 generates sound waveforms for the speaker.

#### Features:

- \* Three independent 16-bit counters

- Count binary or BCD

# 2046 I/O Address Map

The 2046 I/O address decode is fully compatible to the IBM PC/AT requirements. The 2046 has decoded the I/O address range from 000 to 0FF to allow users to use the I/O areas not used by the IBM PC/AT.

| Hex Range | Device                        |

|-----------|-------------------------------|

| 000-00F   | DMA controller 1, 8237A-5     |

| 020-021   | Interrupt controller 1,       |

|           | 8259A,Master                  |

| 040-043   | Timer, 8254                   |

| 060-064   | 8042 (Keyboard)               |

| 070-071   | Real-time clock, NMI (non-    |

|           | maskable interrupt) mask      |

| 080-08F   | DMA page register, 74LS612    |

| 092       | Alternative Gate A20 and FAST |

|           | RESET Register.               |

| 0A0-0A1   | Interrupt controller 2, 8259A |

| 0C0-0DF   | DMA controller 2, 8237A-5     |

| 0F0       | Clear Math Coprocessor Busy   |

| 0F1       | Reset Math Coprocessor        |

| 0F2       | 2046 Configuration Register   |

|           | Index                         |

| 0F3       | 2046 Configuration Register   |

|           | Data                          |

| 0F8-0FF   | Math Coprocessor              |

#### PIO

The PIO is the system configuration to control the speaker port. It also has circuitry to detect refresh. This condition can be read back as Bit 4 of I/O Port 61h.

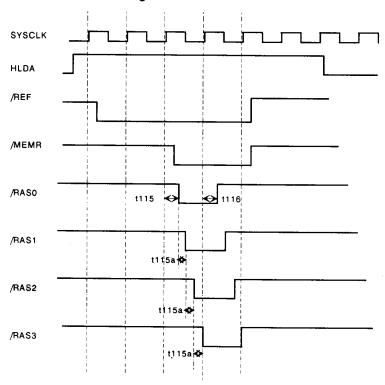

## Refresh Generation Logic

Refresh circuitry contains an 8-bit counter for address SA0-7 during a refresh. In addition, three more address counter bits are presented inside the 2046 to support refresh for DRAMs up to 4M bits.

# Refresh/DMA Arbitration Logic

The 2046 contains circuitry to control a refresh cycle.

There are two possible sources for a hold request to the CPU. Either the DMA controller issues a hold request or the output of Counter 1 in the 8254 makes a low to high transition. The HOLD line is active when either source is requesting a hold. The hold request from the DMA controller is sampled on the rising edge of the DMA clock and the request from the timer is sampled on the falling edge of the DMA clock

If the DMA controller's hold wins the arbitration, the HOLD is asserted, and it waits for a signal back from the CPU. When the DMA controller is finished, it negates its hold request signal to the arbiter. The arbitration then switches to a REFRESH cycle if there is a pending hold from the Counter/Timer, otherwise the arbiter inactivates the HOLD line and returns control to the CPU.

If a refresh cycle wins the arbitration, the HOLD is asserted and the 2046 pulls the /REFRESH pin low. /REFRESH remains low

for four SYSCLK rising edges. On the fourth rising edge of SYSCLK, the HOLD line is inactivated. However, if there is a pending hold request from the DMA controller on the fourth rising edge of SYSCLK, the REFRESH cycle is extended for one more SYSCLK cycle. The hold request arbiter then acknowledges the hold request from the DMA controller.

by an I/O error or by a parity error. Port B indentifies the source of the error. At power up, the NMI signal is masked off. NMI is enabled by writing to I/O address 070 hex with Bit 7 low; NMI is disabled by writing to I/O addresss 070 hex with Bit 7 high.

# **NMI and Port B Logic**

The 2046 contains non-maskable interrupt (NMI) signal generation logic. An NMI can be caused

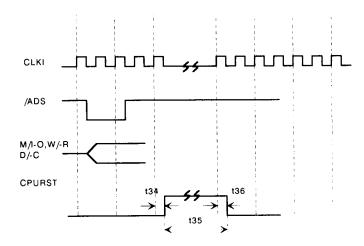

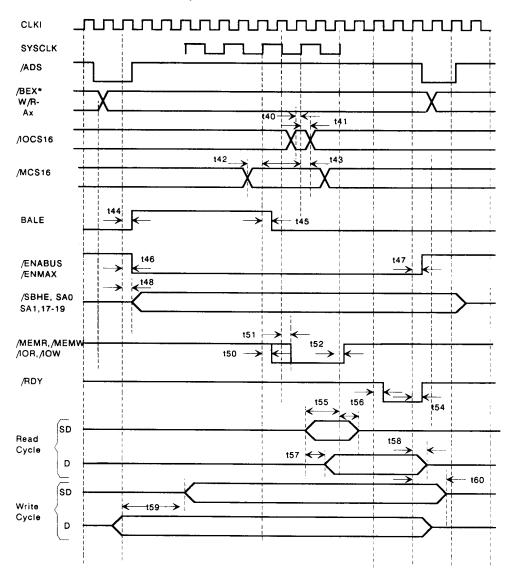

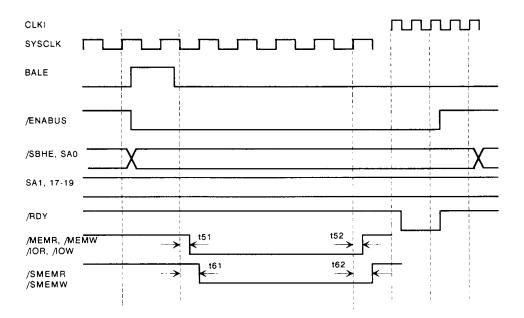

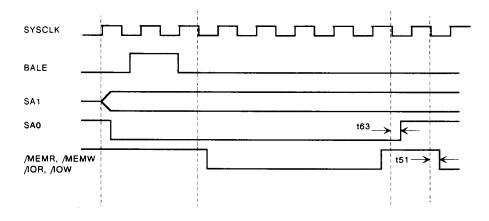

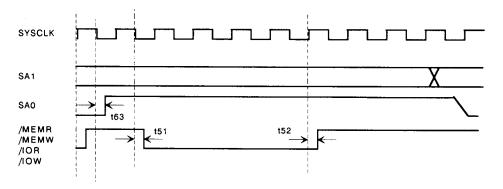

## **Bus Controller and Converter**

The D/-C, W/-R and M/-IO signals carry data from the CPU, announcing a bus cycle and defining its type. Tables 1.1a and 1.1b list and define the different types of bus cycles.

Table 1.1a ACC Micro 2046 386DX Bus Cycle Definitions

| M/-IO  | D/-C   | W/-R   | Bus Cycle Type                                                                                                                                                      |

|--------|--------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0      | 0      | 0      | Interrupt acknowledge                                                                                                                                               |

| 0      | 0      | 1      | Does not occur                                                                                                                                                      |

| 0      | 1      | 0      | I/O data read.                                                                                                                                                      |

| 0      | 1      | 1      | I/O data write.                                                                                                                                                     |

| 1      | 0      | 0      | Memory code read.                                                                                                                                                   |

| 1      | 0      | 1      | Halt if Address = 2; Shutdown if Address = 0<br>(/BE0 High (/BE0 Low<br>/BE1 High /BE1 High<br>/BE2 Low /BE2 High<br>/BE3 High /BE3 High<br>A2-A31 Low) A2-A31 Low) |

| 1<br>1 | 1<br>1 | 0<br>1 | Memory data read.<br>Memory data write.                                                                                                                             |

# ACC Micro

Table 1.1b ACC Micro 2046 486 Bus Cycle Definitions

| M/-IO | D/-C | W/-R | Bus Cycle Type                                                                          | -                                                                                          |

|-------|------|------|-----------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|

| 0     | 0    | 0    | Interrupt acknowledge                                                                   |                                                                                            |

| 0     | 0    | 1    | Halt if Address = 2;<br>(/BE0 High<br>/BE1 High<br>/BE2 Low<br>/BE3 High<br>A2-A31 Low) | Shutdown if Address = 0<br>(/BE0 Low<br>/BE1 High<br>/BE2 High<br>/BE3 High<br>A2-A31 Low) |

| 0     | 1    | 0    | I/O data read.                                                                          | ,                                                                                          |

| 0     | 1    | 1    | I/O data write.                                                                         |                                                                                            |

| 1     | 0    | 0    | Memory code read.                                                                       |                                                                                            |

| 1     | 0    | 1    | Does not occur.                                                                         |                                                                                            |

| 1     | 1    | 0    | Memory data read.                                                                       |                                                                                            |

| 1     | 1    | 1    | Memory data write.                                                                      |                                                                                            |

The bus controller has four operation modes.

#### AT CPU Mode

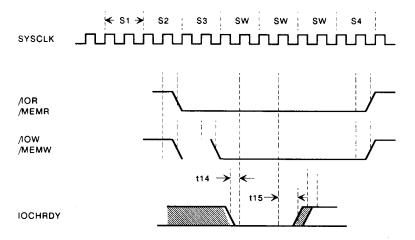

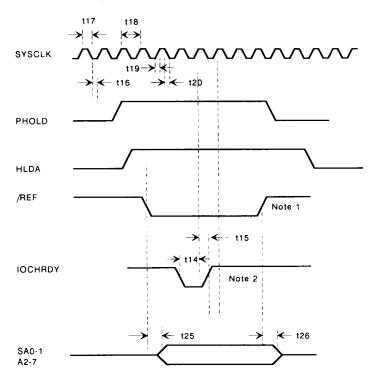

This mode is active when HLDA is low. The CPU bus controller generates /IOR, /IOW, /INTA, /MEMR, and /MEMW signals.

#### DMA Mode

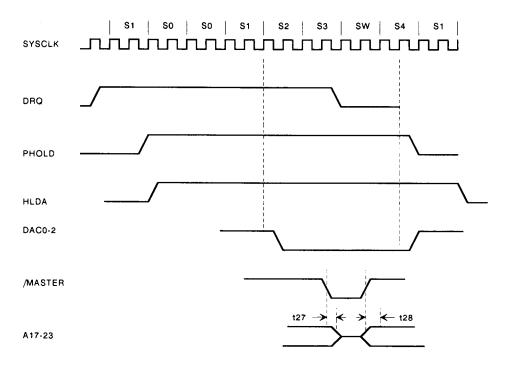

DMA mode is active if HLDA and AEN are active. The DMA controller drives the /IOR, /IOW, /MEMR, and /MEMW signals.

#### Refresh Mode

Refresh mode is active when HLDA and /REFRESH are active. /MEMR becomes active at this time to perform a refresh on both AT bus and local DRAM.

#### Master Mode

Master mode is active when HLDA is active and a card in the AT slot pulls /MASTER low. The card controls system address, data line and control line.

#### **Bus Conversion**

The 2046 contains logic to convert between 16-bit and 8-bit data accessing. During a bus conversion cycle, the AT bus command strobe (/MEMR, /MEMW, /IOR, or /IOW) is activated two times.

#### **CPU Interface**

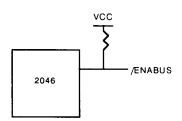

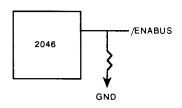

The 2046 supports the 486DX/SX and 386DX CPUs. The CPU interface selection is determined by detecting a pull up or pull down resister on pin 29 (/ENABUS) during the reset period. A pull down resister on pin 29 will trigger the 2046 operating in the 486 mode. A pull up resister on pin 29 will trigger the 2046 operating in the 386DX mode.

386DX mode configuration

486 mode configuration

#### 80387 Interface Control

The 80387 interfaces directly to the 386DX with the error-reporting logic built in the 2046. A coprocessor error is sent to the 2046, generating an interrupt request to the CPU, followed by a service request. A write operation to I/O port 0F0 will clear the interrupt request.

#### **Clock Generator**

The 2046 Clock Generator provides clock signals to support internal and external timing requirements. It provides clock outputs for the CPU, the NPU, and the Keyboard Controller. Clock signals are generated from three clock sources. A 14.318 MHz crystal is connected to X14M1 and X14M2 to generate a 14.318 MHz frequency. An alternative external oscillator (16 MHz) is connected to pin EXT16M to provide an optional 16 MHz input clock for the AT Bus. CLKSRC input is one or two times of the CPU operation clock providing turbo mode operation in single phase or double phase clock mode respectively. CLKSRC is driven by an external oscillator. The AT Bus clock can be derived from three places. It can be generated by dividing down the CLKSRC to an approximated 16M frequency, or it can be generated by dividing the 14.318M frequency down to half (to 7.15M), or it can be generated from the external 16M directly.

# ACC Micro

#### Clock Mode Selection

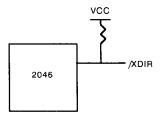

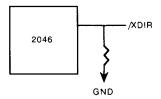

The 2046 supports both single phase clock and double phase clocks. The clock phase is determined by detecting a pull up or pull down resister on pin 28 (/XDIR) during reset period. A pull-up resister on pin 28 will trigger the 2046 to operate in double phase clock. A pull down resister on pin 28 will trigger the 2046 to operate in single phase clock.

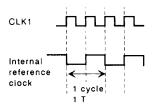

Double phase clock

Single phase clock

The double phase clock has a clock source which is two times of the CPU operation clock. In double phase clock, every cycle consists of two CLKI periods. Double phase clock can be used for both the 486DX/SX systems or 386DX systems. In the 486 mode, the 2046 provides a dedicated 486CLK which is a half of the

CLKSRC for 486 CPU. The 2046 double phase clock operation supports both page interleaved mode and page mode memory controller.

#### Double phase clock

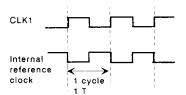

The single phase clock has a clock source which is one times of the CPU operation clock. In single phase clock, every CLKI input period becomes one completed cycle. Single phase clock is used primarily for the 486 systems. Either CLKOUT or 486CLK can be used as 486 CPU clock input. The 2046 in single phase clock mode only supports a page mode memory controller.

Single phase clock

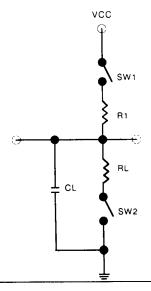

#### **Turbo Speed Control Logic**

The CPU clock frequency can be switched between CLKSRC and the AT clock. The frequency switch can be generated through either hardware or software. A TURBO pin is provided to support a front panel turbo speed switch. TURBO high selects CLKSRC as the CPU clock. TURBO low selects AT Bus clock as the CPU clock.

For power conservation, a standby mode clock control is provided. A system needs to preselect the standby frequency first, then an intelligent BIOS will monitor the activity of the system. If all pre-defined conditions of the standby mode are satisfied, the system will go into the standby mode by programming bit 3 of register 8h to 1 or if Turbo/Sleep bit has been set to 1, the Turbo pin low will force the system into sleep mode.

The standby mode CPU operating frequency can be pre-set by programming bit 2-0 of configuration register 8h. If AT Bus clock source is at 16 MHz, the standby frequencies output of CLKOUT are set as follows:

| Bit 2 | Bit 1 | Bit 0 | Frequency |

|-------|-------|-------|-----------|

| 0     | 0     | 0     | 16 MHz    |

| 1     | 0     | 0     | 8 MHz     |

| 1     | 0     | 1     | 4 MHz     |

| 1     | 1     | 0     | 2 MHz     |

| 1     | 1     | 1     | 1 MHz     |

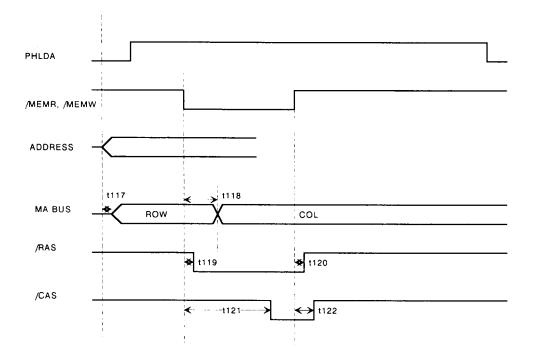

# Memory Controller

The Memory Controller is a key feature of the 2046. This versatile circuit provides complete control of up to 64 megabytes of system DRAM. In any control mode, it generates up to four Row Address Strobes (/RAS0-3) and one Memory Write Enable signal (/WEN). The Memory Controller also provides the interface to transfer control to a DMA controller or an AT Bus master.

#### **Memory Control Modes**

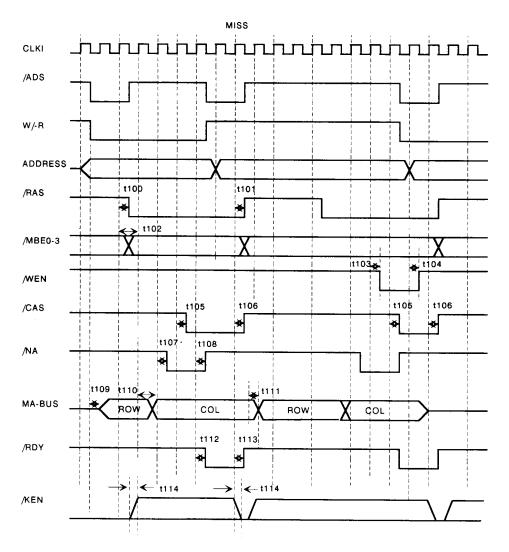

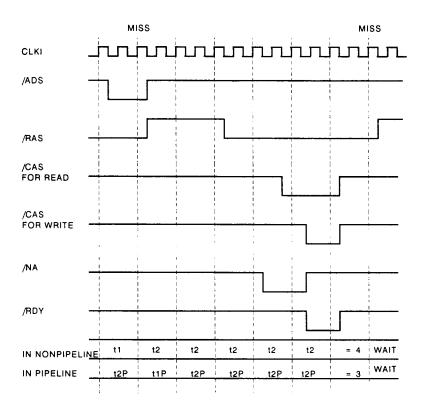

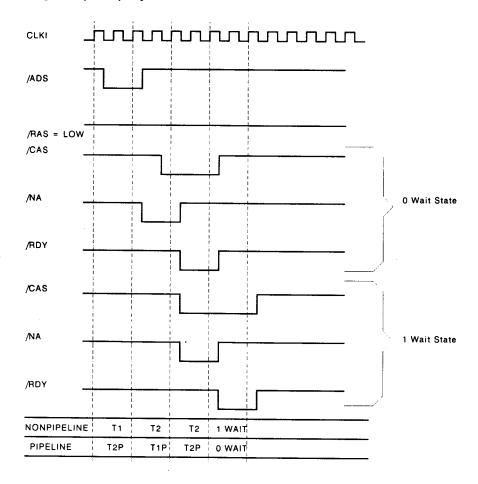

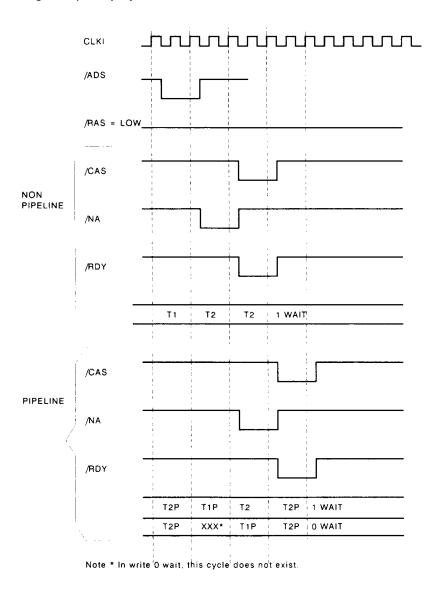

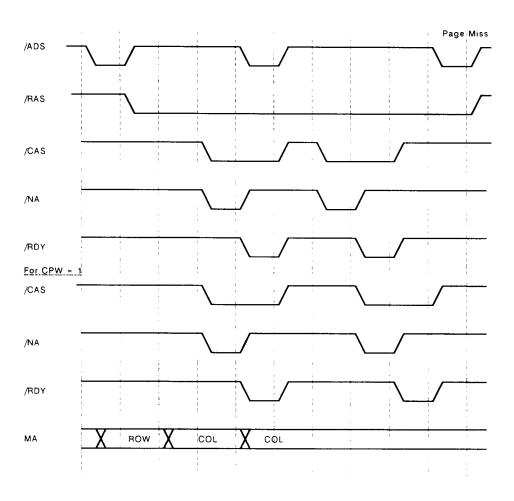

The 2046 features two memory control modes: Page Interleaved Mode and Page Mode. These options provide flexibility and optimize system performance. Both will be running at 0 wait state when a page hit occurs in pipeline mode. With Page Interleaved mode, a minimum of three wait states are asserted when a memory miss occurs. Mode select is done by programming the power up select register, Register 5h, bit 4.

## Page Interleaved Mode

The 2046 implements a 4-way and 2-way page interleaved memory controller, providing optimum system performance for high speed CPUs. The Page Interleaved Memory Controller operates on two principles: Page Mode Memory access, which is much faster than random access, and the sequential and localized patterns it follows. The Page Interleaved Memory Controller organizes the memory array into interleaved pages by banks, operating up to four banks simultaneously in Page mode. Each bank of memory consists of 36 bits of DRAM (four 8-bit bytes plus four parity bits).

# ACC Micro

The size of a memory page is determined by the type of DRAM installed. The page sizes are a result of the physical architecture of the DRAM. Once page interleaved mode is selected, a row can be kept active (/RAS low) almost indefinitely (up to 10uS), allowing any number of column accesses along that same row. Each row, and any intersecting column access along that same row, is defined as a "Page Hit." This results in a zero wait state access. If any subsequent memory access selects a new row, it is defined as a "Page Miss" and results in a minimum of three wait state access.

The organization and operation of the memory array is dependent on the type and quantity of memory installed (See "Configuration Registers" section). Memory performance is improved when a greater number of open pages, up to four, are used. This provides a larger and more flexible "zero wait state" work space. The open page on each bank retains the last row address selected on that particular bank.

The RAS precharge time can be programmed to 2 or 3 cycles by programming bits 1 and 3 of Register 1h. One or two more wait states can also be inserted in read or write cycles to utilize slower DRAM in the cache system.

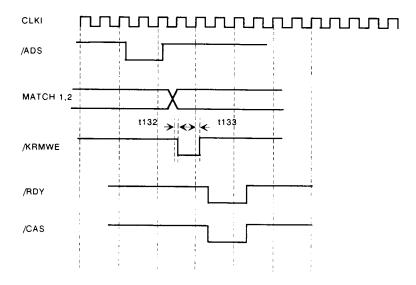

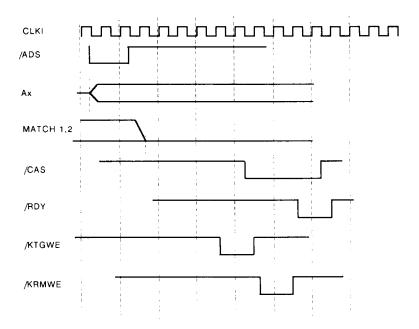

# Page Mode

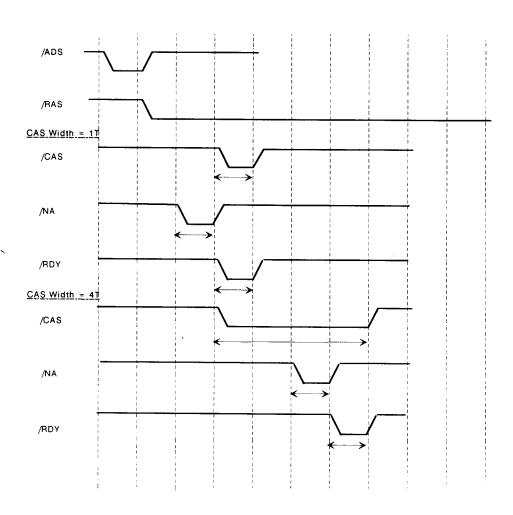

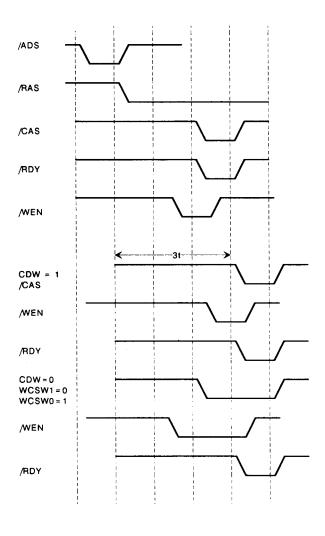

Page mode provides even more flexibility for high speed cache system. In page mode operation, four RAS are generated, but only one will be activated at any time. Logically four banks behave as one large bank of memory. All the DRAM parameters can be programmed including RAS precharge time, RAS to CAS delay, CAS precharge time, CAS width for read and write cycles. All these parameters can be programmed on a cycle by cycle basis. Please refer to Register 0Bh page mode setup.

# Memory Control Mode and CPU Clock Mode

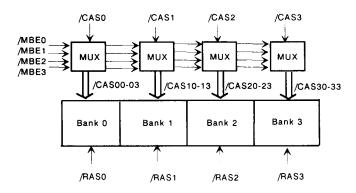

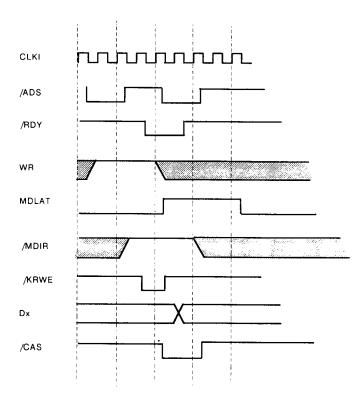

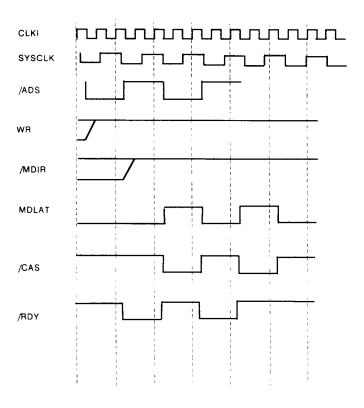

In double phase clock mode, the 2046 can operate in either Page Interleaved mode or Page mode. Four CAS are generated from the 2046, one for each bank which should be logically anded with the four byte enable signals  $\text{MBE}_\chi$  to generate individual CAS for every byte in that bank. Refer to the double phase clock memory controller application diagram (Fig. 1.1a).

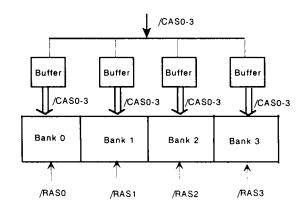

In single phase clock mode, the 2046 operates in Page mode. One CAS is provided for each byte. Totally four CAS are generated and are shared by all banks. Refer to the single phase clock mode memory controller application diagram (Fig. 1.1b).

Figure 1.1a Memory Controller Application Diagram in Double Phase Clock

Figure 1.1b Memory Controller Application Diagram in Single Phase Clock

# **Memory Mapping**

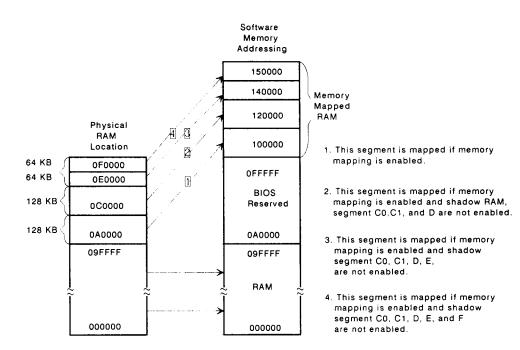

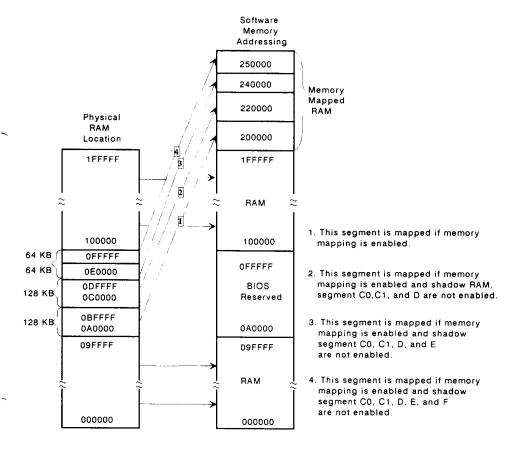

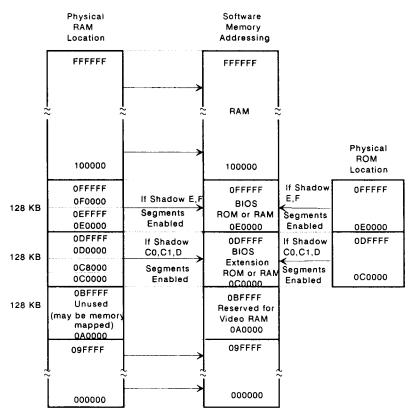

Memory Mapping translates system RAM within the 640 KB to 1MB range, which is reserved for the system ROM and BIOS application, to an accessible address range above the physical RAM space. For example, if 4 MB of memory are installed, and the memory mapping feature is on, the DRAMs in the 640 KB to 1MB range are mapped to an address immediately above 4 MB.

Memory Mapping is enabled by bit 7 of register 0 in the configuration registers. When Shadow RAM is enabled simultaneously with Memory Mapping, the quantity of RAM available for Memory Mapping is reduced.

If Shadow RAM segment F is enabled, 320KB of RAM can be mapped. If Shadow segment E is enabled, 256KB of RAM can be mapped. If any of the segments C0, C1, or D are enabled, 128 KB of RAM can be mappped. The mapping function can only be used in memory configurations 0, 1, 2, 3, and 4 in page interleaved mode and all memory options, except option 24, in page mode.

Figure 1.2 Memory Mapping for a 1 MB System

#### Shadow RAM

Shadow RAM provides an option to transfer BIOS or video-extension BIOS program codes into system RAM. This option provides significant performance improvement for applications requiring intensive BIOS calls.

Shadow RAM implements an alternate BIOS source by copying the complete EPROM

program code into system RAM. This is referred to a "shadowing" because the DRAM and EPROM are both located at the same physical address space. This change is transparent to the rest of the system. ROM can be disabled, allowing the RAM to respond in its place. The advantage of this procedure is that DRAM access time is typically much faster than EPROM access time.

Figure 1.3 Memory Mapping for a 2 MB System

The 2046 Shadow RAM is configured in five independent segments: 00C0000 to 00C7FFF (Shadow C0), 00C8000 to 00CFFFF (Shadow C1, 00D0000 to 00DFFFF (Shadow D), 00E0000 to 00EFFFF (Shadow E), and 00F0000 to 00FFFFF (Shadow F), as shown in Fig. 1.4. Each segment can be enabled for shadow operation individually or simultaneously.

Enabling a Shadow RAM segment requires two steps. The "shadow enable" configuration bit for the segment to be shadowed must be set to allow the transfer of code from EPROM to DRAM. The second step sets the "Shadow Read Only" configuration bit of the corresponding segment to protect the Shadow RAM.

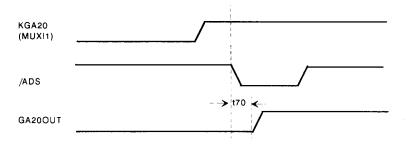

## OS/2 Optimization

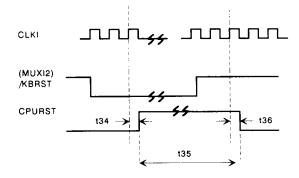

The 2046 implements OS/2 optimization, which is a more efficient way to switch back and forth between real and protected modes in an OS/2 environment when frequent DOS calls are made. Conventional methods require the processor to communicate with the keyboard controller in switching to protected mode and activating gate A20.

With OS/2 optimization, the 2046 allows control of software CPU reset and A20 gating through Port 92h.

Figure 1.4 ACC Micro 2046 Shadow RAM Address Map

# Configuration Register Port 92h, Fast A20 Gate, and Alternative RESET Control

| Bit | Function            |

|-----|---------------------|

| 7-2 | Reserved            |

| 1   | A20 Gate            |

| 0   | Alternate CPU reset |

Bit 1 This bit controls CPU address bit A20. When set to 1, it enables A20. When set to 0, this bit makes the A20 Signal inactive, thus preventing the Address bus from going beyond the 0FFFFFh boundary in Real Mode. Although it has the same function as the keyboard controller's GATE-A20 signal, it is much faster because it is just a simple I/O write operation. Default is 0.

Bit 0 By setting this bit to 1, application softwares can reinitialize the microprocessor and switch the operation from Protected Mode to Real Mode. Setting this bit does not reset the whole system, it only affects the CPU. This reset function is the same as that of the keyboard controller's "KBRST" signal. However, it provides a faster reset sequence. This bit can be read by application software to determine if it is a hot rest or cold boot. It can only be set to 0 by writing a 0 to bit 0 of the register or by power up. Default is 0.

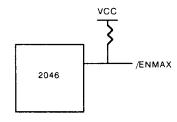

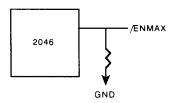

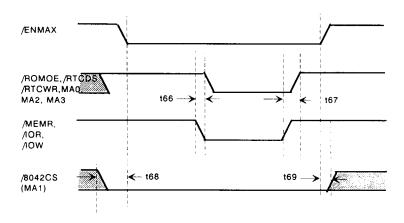

# 8-bit/16-bit ROM Options

The 2046 supports both 8-bit and 16-bit ROM Data buses. It is configured by a pull-up or a pull-down resistor on pin 139 ENMAX# as demonstrated below:

#### 8-bit ROM configuration

#### 16-bit ROM configuration

The 16-bit ROM is treated as a 16-bit Bus memory. It can be accessed more efficiently and it takes less time to finish a cycle.

The 8-bit ROM is located in the local I/O Bus and treated as an AT Bus device. Due to its narrow data path and long cycle, the performance of ROM cycles will not be as efficient as that of the 16-bit option. However, as the 2046 provides BIOS shadow capability, this inefficiency can be avoided by moving the BIOS code from the 8-bit ROM to a 32-bit local RAM.

# 128K/64K ROM BIOS Range

The ROM BIOS range can be set to two different sizes--64K or 128K--to accommodate various application requirements. Refer to configuration 0h definition to configure the size of the ROM BIOS Range.

# Staggered Refresh Logic

The 2046 refresh logic works to perform a periodic refresh for both system DRAM and extended RAM on the AT Bus. The 2046 initiates a refresh cycle by driving its /REFRESH output low, and driving the refresh address onto the MA Bus, simultaneously generating staggered refresh pulses on the four RAS outputs. The RAS outputs are staggered to reduce the current drain caused by the refresh operation.

During each refresh cycle, the 2046 drives the current refresh address onto the AT address bus. This provides the refresh address for extended memory.

# **Direct Mapped Cache Controller**

The 2046 supports a high performance cache system by using the built-in direct mapped cache controller or a dedicated cache controller, such as Intel's 82385 or 82395. A cache system contains a copy of frequently used code and address from main memory in a zero wait state SRAM. The program locality is such that, in most cases, the system can fetch the needed data and codes from the cache. The cache system reduces the average memory access to nearly zero wait state and increases the whole system's performance dramatically.

The built-in 2046 direct mapped cache controller arranges the tags in such a way that each address in the main memory corresponds to a single cache directly. This keeps the

design simple and reduces the cost of a high performance cache system.

In a 486 AT system, if the internal cache of 486 is enabled, the 2046 direct mapped cache can be used as secondary cache to further improve the system performance especially in a multi-user, multi-task environment.

#### Posted Write and Write Through

The 2046 cache controller supports writethrough and post write cache update options to prevent old data from being used.

The write-through option is the simplest way to keep cache coherent. In a cache write hit cycle, the memory controller will update the DRAM at the same time that it is written to the cache. The 2046 cache controller default mode is write-through mode.

The 2046 also supports posted write cache system by programming configuration register 4h, bit 7 to enable posted write operation. This posted write option allows the data to be buffered before updating to the main memory. The system performance is therefore increased, since the processor can start a new cycle before the write cycle to the main memory is completed.

#### Cache Burst and Line Size

The 2046 supports a flexible line size structure and cache burst. The 2046 supports 32 bit, 64 bit or, 128 bit line sizes. Configuration register 4h, bits 2 and 1 determine the line size. In the case of a cache read hit cycle, the 2046 will pull the burst ready signal, /BRDY, low and fill the 486 internal cache lines quickly. A 128 bit line size requires only 5 cycles to fill the cache lines. A 64 bit line size requires 3 cycles.

# **ACC Micro**

In the case of a read miss cycle, the 2046 burst mode will generate four continuous DRAM read cycles for a 128 bit line size to fill both 486 internal and external cache. For a 64 bit line size, the 2046 burst mode will generate two burst cycles instead of four.

#### **Cache Memory Organization Examples**

The 2046 Direct Mapped Cache architecture is so flexible that a cost effective cache system can be organized to suit each system manufacturer's specific needs.

Designers can use either off-the-shelf Tag RAMS or standard fast SRAM coupled with comparators to compare the tag address to determine a hit or a miss.

#### Example 1:

Design a 32K cache for an 8 Mbyte cacherange.

Cacheable Range:

8 Mbyte (A2-A22)

Line size:

32 bit Address index to TAG RAM: A2-A14

TAG field:

A15-A22

TAG RAM required:

one 8K x 8 four 8K x 8

Data RAM required: DRAM size:

8 Mbyte

Since the cacheable range is 8 Mbyte, it is recommended that the DRAM size not exceed the cacheable size.

#### Example 2:

Design a 64K cache for a 16 Mbyte cache range

Cacheable Range:

16 Mbyte (A3-A23)

Line size:

64 bit

Address Index to TAG RAM: A3-A15 TAG field:

A16-A23

TAG RAM required:

one 8K x 8

Data RAM required:

eight 8K x 8

16 Mbyte

DRAM size:

#### Example 3:

Design a 128K cache for a 32 Mbyte cache range

Cacheable Range:

32 Mbyte (A4-A24)

2046

Line size:

128 bit Address Index to TAG RAM: A4-A16

TAG field:

A17-A24 One 8K x 8

TAG RAM required: Data RAM required:

sixteen 8K x 8

DRAM size:

32 Mbyte

#### Example 4:

Design a 128K cache for a 16 Mbyte cache range

Cacheable Range:

16 Mbyte (A4-A23)

Line size:

Address Index to TAG RAM: A4-A16 TAG field:

A17-A23

TAG RAM required:

one 8K x 8

Data RAM required:

sixteen 8K x 8

DRAM size:

16 Mbyte

# TAG RAM and Data RAM Speed Requirement

| System<br>Speed       | 25 MHz | 33 MHz | 40 MHz |

|-----------------------|--------|--------|--------|

| DRAM<br>speed         | 80 ns  | 80 ns  | 80 ns  |

| DRAM<br>wait<br>speed | 0      | 1      | 1      |

| SRAM                  | 30 ns  | 25 ns  | 20 ns  |

| TAG<br>RAM            | 25 ns  | 20 ns  | 16 ns  |

# Cache RAM circuit example

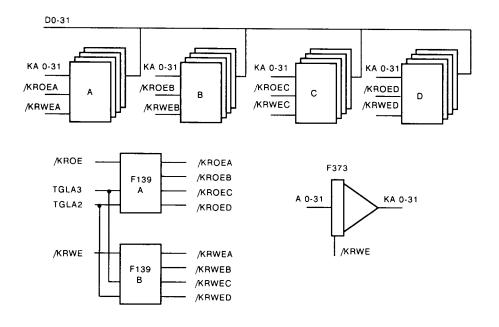

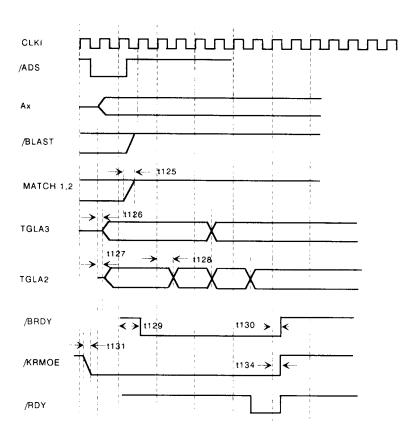

The 2046 has two different cache RAM application circuits depending on the CPU clock running mode.

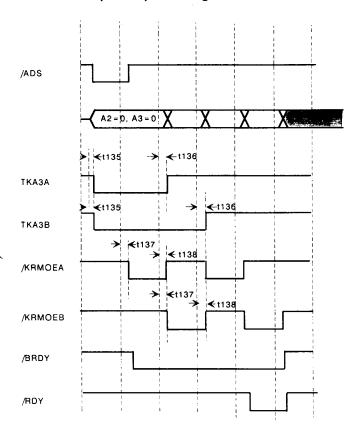

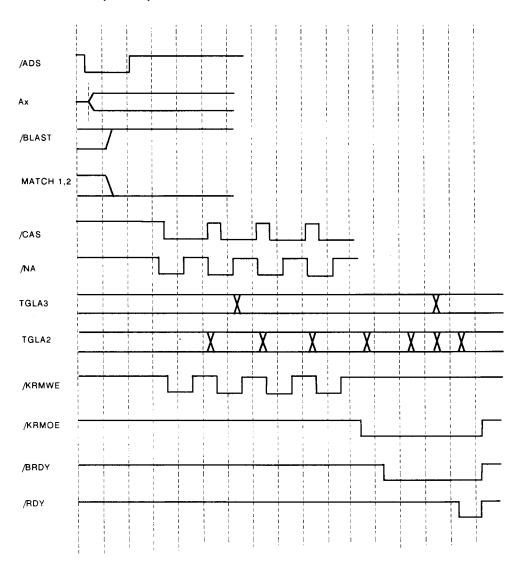

In double phase clock mode, the 2046 supports four banks of cache RAM. Signals /KROE, /KRWE, TGLA2, and TGLA3 will be multiplexed to generate the necessary control signals (/KROE A-D and /KRWE A-D) for each

bank of cache RAM. Please refer to Figure 1.5, cache RAM application circuit in double phase clock mode.

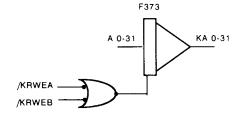

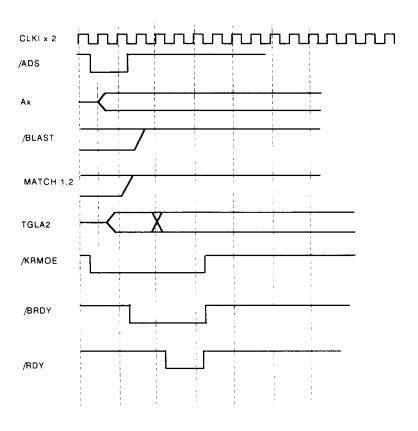

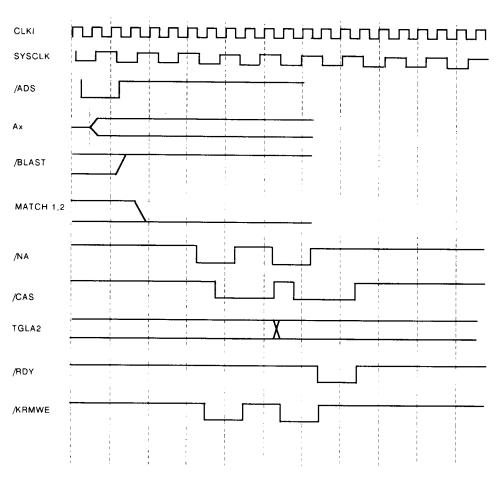

In single phase clock mode, the 2046 supports two bank interleaved cache RAM memory. Cache RAM enable signals /KROE A-B and /KRWE A-B are generated by 2046 directly. Please refer to Figure 1.6.

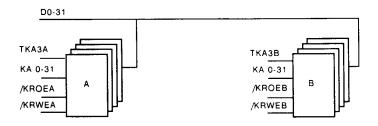

Fig. 1.5 Cache RAM application circuit in double phase clock mode

Fig. 1.6 Cache RAM application circuit in single phase clock mode

#### Non-Cacheable Area

The 2046 built-in cache controller allows three programmable blocks to be defined as non-cacheable area. The three non-cacheable block sizes are defined by configuration register, Ch, Eh, 10h, 0Ch and 0Eh, bits 0-3. The block size can be 16K, 32K, 64K, 128K, 256K, 512K, or 1Mbyte. The starting address of the non-cacheable block are defined by configuration registers Dh, Fh, 11h, 0Ch, 0Dh, 0Eh, and 0Fh respectively which set the non-cacheable address bits from A14 to A25.

Non-cacheable locations are necessary for memory-mapped I/O device, network interface board, dual port memory, hard disk controller, or any other memory that should not be cached

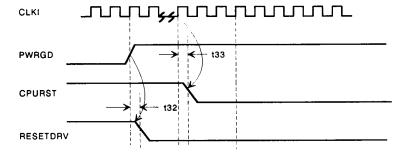

#### **Reset and Shutdown Logic**

The reset and shutdown logic contains the circuitry for the RESETDRV and CPURSTsignals. Reset circuitry generates two resets. One is for the general system reset with power on and the other is for the CPU, or for taking the CPU out of protected mode when a warm software reset request is generated by the 8042 keyboard controller.

The CPURST signal generates a system reset and is synchronized to CPUCLK. When the keyboard reset signal is generated from the 8042 keyboard controller (called a warm reset), CPURST is activated to reset the CPU. CPURST is asserted for at least sixteen CPUCLK cycles and then deactivated for proper CPU operation.

# Suspend and Resume Function

The 2046 along with the power management chip ACC Micro 2020 supports a power conservation feature-- Suspend and Resume. Necessary hardware is provided to monitor the activity of power hungry devices such as microprocessor, fixed disk drive, LCD display, etc. All defined register bits in the 2046 and the 2020 are readable and writeable to support this feature.

Through software task, a device can be powered off when no activity is detected for a reasonable length of time which can be programmed in set-up program. The device then can be powered back on to the same state as the last power off when it is desired. This suspend and resume capability minimizes system's battery power consumption.

# **Configuration Registers**

The 2046 contains configuration registers which provide a variety of functions. These functions are concerned with system initialization, software control of advanced memory control and power saving features. For system initialization, these configuration registers implement a no-cost, no-space alternative to system board DIP switches. For advanced memory control, these registers provide maximum flexibility and convenience for programming. Configuration registers are programmed with an indirect addressing scheme using I/O addresses F2 and F3. I/O address F2 contains the write-only configuration index register. F2 selects the corresponding

configuration register accessed at I/O address F3. To write a value of "E8" into configuration register 2Ah, the configuration index register at I/O address F2 must first be written with a value of "2A," then register at I/O address F3 with a value of "E8."

Configuration registers are selected by the configuration index register at I/O address F2. Table 1.3 contains a summary of configuration registers 0h - 1Ch.

Table 1.3 ACC 2046 Configuration Registers 0h-1Ch

| PEN MIDRO<br>MROW<br>KSHEN<br><br>FW BMW0<br>M8 M386<br> | S<br>N SHRD<br>  | ENROM<br>TIMEOUT<br>ESHF<br>DISPCK<br>BURST<br>E EPMSEO | < me<br><br>ESHE<br>/NPWS<br>KB486 | mory configu<br><br>ESHD<br>/NPSEQ<br>< cache lii                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ENRAS<br>ESHC<br>/WETK | ENRD<br>ESHC0<br>/E387                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|----------------------------------------------------------|------------------|---------------------------------------------------------|------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| KSHEN<br><br>FW BMW0<br>M8 M386<br>                      | SHRD<br><br>K1WS | ESHF<br>DISPCK<br>BURST                                 | ESHE<br>/NPWS                      | /NPSEQ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | ESHC<br>/WETK          | ESHC0<br>/E387                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| <br>FW BMW0<br>M8 M386<br>                               | <br>K1WS         | DISPCK<br>BURST                                         | /NPWS                              | /NPSEQ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | /WETK                  | /E387                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| M8 M386<br>                                              | –                | BURST                                                   | ,                                  | ,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ,                      | ,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| M8 M386<br>                                              | –                |                                                         | KB486                              | < cache li                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | · .                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                                          | PHASE2           | EPMSEQ                                                  |                                    | > 040116 III                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | ne siżė>               | <b>ECACHE</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                                          |                  |                                                         |                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | SLREF1                 | SLREF0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                          |                  | <                                                       | Bus clock                          | select and d                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | ivider                 | >                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                          |                  | <                                                       | MUX clock                          | select and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | divider                | >                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                          |                  |                                                         | ENSLM                              | < SLM free                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | quency div             | isor >                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                          |                  |                                                         |                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ENPW                   | EKBRS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                          |                  |                                                         |                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ENA25                  | ENA24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| V1 RPW0                                                  | CPW              | CPT                                                     | RCSW1                              | RCS0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | WCSW1                  | WCSW0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 7 CA16                                                   | CA15             | CA14                                                    | BST3                               | BST2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | BST1                   | BST0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |