SN74LV8154

Features

- 1 Can Be Used as Two 16-Bit Counters or a Single 32-Bit Counter

- 8-bit counter read bus

- 2-V to 5.5-V VCC Operation

- Maximum tpd of 25 ns at 5 V (RCLK to Y)

- Typical VOLP (Output Ground Bounce)

< 0.7 V at VCC = 5 V, TA = 25°C

- Typical VOHV (Output VOH Undershoot)

> 4.4 V at VCC = 5 V, TA = 25°C

- Ioff Supports Partial-Power-Down Mode Operation

- Latch-Up Performance Exceeds 250 m A

Per JESD 17

- ESD Protection Exceeds JESD 22

- 2000-V Human Body Model (A114-A)

- 200-V Machine Model (A115-A)

- 1000-V Charged-Device Model (C101)

2 Applications

- Up Counters

- Dual Up Counters

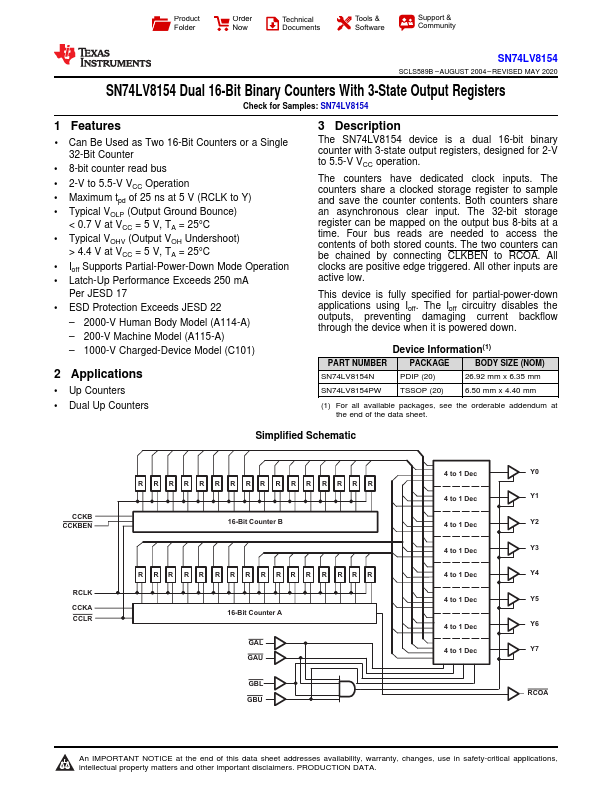

3 Description

The SN74LV8154 device is a dual 16-bit binary counter with 3-state output registers, designed for 2-V to 5.5-V VCC operation.

The counters have dedicated clock inputs. The counters share a clocked storage register to sample and save the counter contents. Both counters share an asynchronous clear input. The 32-bit storage register can be mapped on the output bus 8-bits at a time. Four...