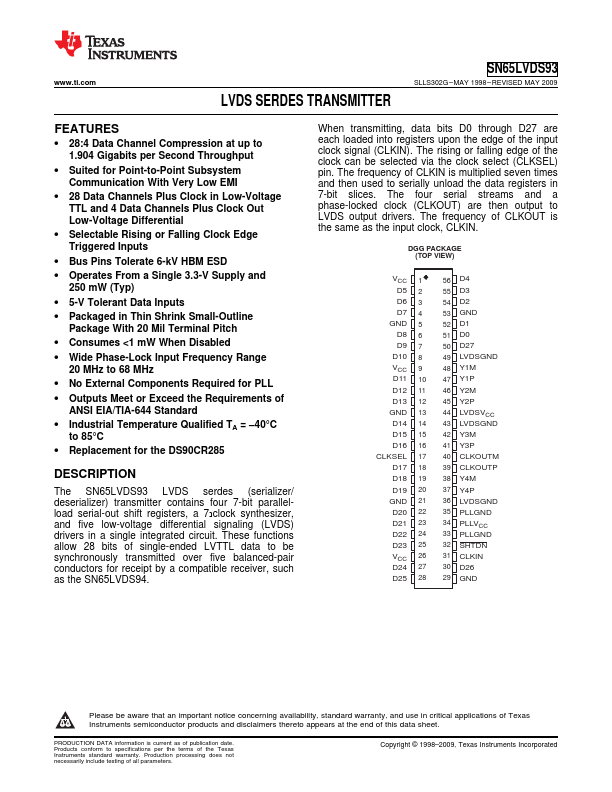

SN65LVDS93 Key Features

- 28:4 Data Channel pression at up to 1.904 Gigabits per Second Throughput

- Suited for Point-to-Point Subsystem munication With Very Low EMI

- 28 Data Channels Plus Clock in Low-Voltage TTL and 4 Data Channels Plus Clock Out Low-Voltage Differential

- Selectable Rising or Falling Clock Edge Triggered Inputs

- Bus Pins Tolerate 6-kV HBM ESD

- Operates From a Single 3.3-V Supply and

- 5-V Tolerant Data Inputs

- Packaged in Thin Shrink Small-Outline

- Consumes <1 mW When Disabled

- Wide Phase-Lock Input Frequency Range