D2012

DESCRIPTION

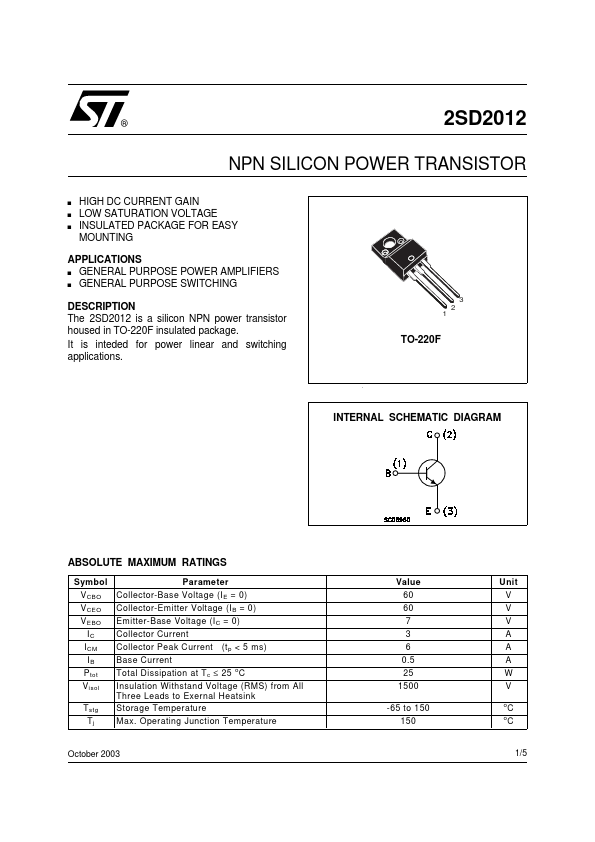

The 2SD2012 is a silicon NPN power transistor housed in TO-220F insulated package. It is inteded for power linear and switching applications.

3 2 1

TO-220F

INTERNAL SCHEMATIC DIAGRAM

ABSOLUTE MAXIMUM RATINGS

Symbol VCBO VCEO VEBO IC ICM IB Ptot Visol

Tstg Tj

Parameter Collector-Base Voltage (IE = 0) Collector-Emitter Voltage (IB = 0) Emitter-Base Voltage (IC = 0) Collector Current Collector Peak Current (tp < 5 ms) Base Current Total Dissipation at Tc ≤ 25 o C Insulation Withstand Voltage (RMS) from All Three Leads to Exernal Heatsink Storage Temperature Max. Operating Junction Temperature

October 2003

Value 60 60 7 3 6 0.5 25

-65 to 150 150

Unit V V V A A A W V o C o C

1/5

2SD2012

THERMAL DATA

Rthj-case Thermal Resistance Junction-case

Max

5 o C/W

ELECTRICAL CHARACTERISTICS (Tcase = 25 o C unless otherwise specified)

Symbol

Parameter

Test Conditions

ICBO

Collector Cut-off Current (IE = 0)

IEBO

Emitter Cut-off Current (IC = 0)

V(BR)CEO∗ Collector-Emitt...