74LS195

DESCRIPTION

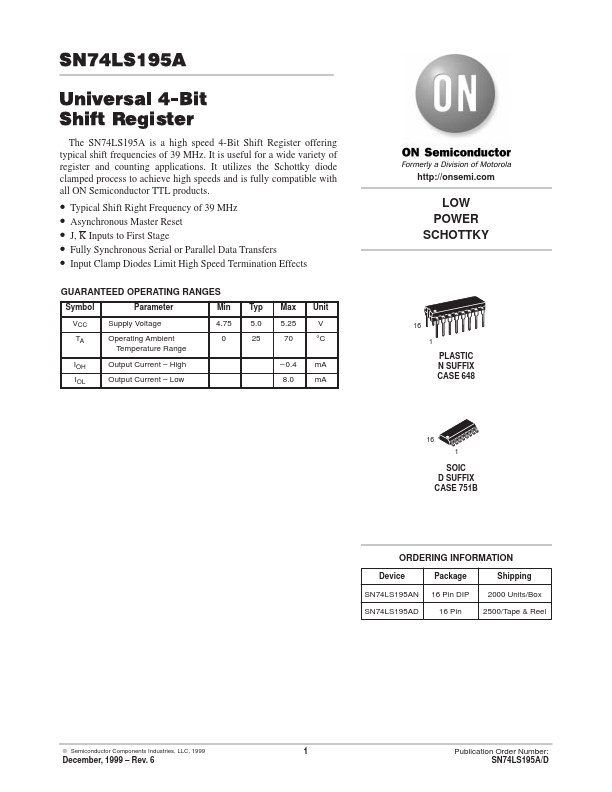

The Logic Diagram and Truth Table indicate the functional characteristics of the LS195A 4-Bit Shift Register. The device is useful in a wide variety of shifting, counting and storage applications. It performs serial, parallel, serial to parallel, or parallel to serial data transfers at very high speeds. The LS195A has two primary modes of operation, shift right (Q0 Q1) and parallel load which are controlled by the state of the Parallel Enable (PE) input. When the PE input is HIGH, serial data enters the first flip-flop Q0 via the J and K inputs and is shifted one bit in the direction Q0 Q1 Q2 Q3 following each LOW to HIGH clock transition. The JK inputs provide the flexibility of the JK type input for special applications, and the simple D type input for general applications by tying the two pins together. When the PE

³

³

³ ³ input is LOW, the LS195A appears as four mon clocked D flip-flops. The data on the parallel inputs P0, P1, P2, P3 is transferred to the...