GP2021

DESCRIPTION

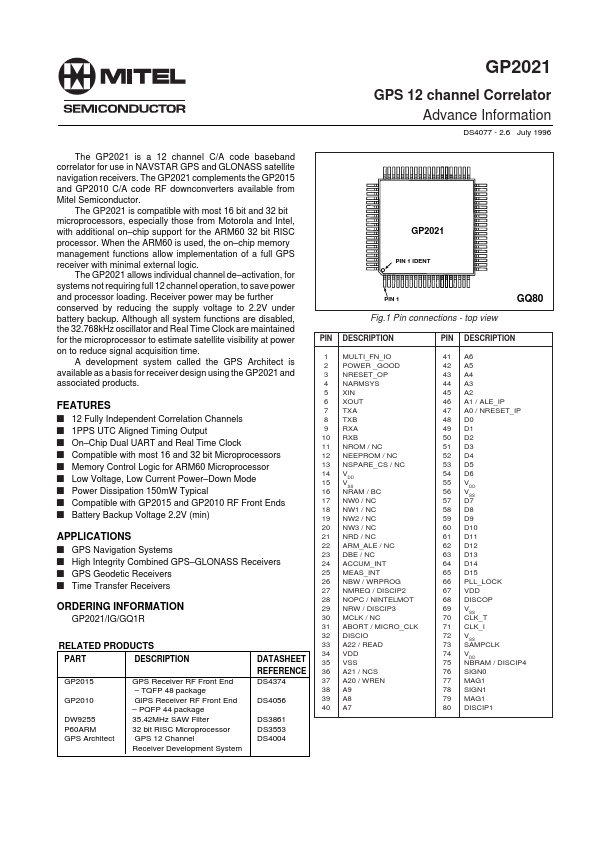

MULTI_FN_IO POWER _GOOD NRESET_OP NARMSYS XIN XOUT TXA TXB RXA RXB NROM / NC NEEPROM / NC NSPARE_CS / NC VDD VSS NRAM / BC NW0 / NC NW1 / NC NW2 / NC NW3 / NC NRD / NC ARM_ALE / NC DBE / NC ACCUM_INT MEAS_INT NBW / WRPROG NMREQ / DISCIP2 NOPC / NINTELMOT NRW / DISCIP3 MCLK / NC ABORT / MICRO_CLK DISCIO A22 / READ VDD VSS A21 / NCS A20 / WREN A9 A8 A7 PIN 41 42 43 44 45 46 47 48 49 50 51 52 53 54 55 56 57 58 59 60 61 62 63 64 65 66 67 68 69 70 71 72 73 74 75 76 77 78 79 80 DESCRIPTION

A6 A5 A4 A3 A2 A1 / ALE_IP A0 / NRESET_IP D0 D1 D2 D3 D4 D5 D6 VDD VSS D7 D8 D9 D10 D11 D12 D13 D14 D15 PLL_LOCK VDD DISCOP VSS CLK_T CLK_I VSS SAMPCLK VDD NBRAM / DISCIP4 SIGN0 MAG1 SIGN1 MAG1 DISCIP1

FEATURES s 12 Fully Independent Correlation Channels s 1PPS UTC Aligned Timing Output s On- Chip Dual UART and Real Time Clock s patible with most 16 and 32 bit Microprocessors s Memory Control Logic for ARM60 Microprocessor s Low Voltage, Low Current Power- Down Mode s Power Dissipation 150m W...