PL130-09

DESCRIPTION

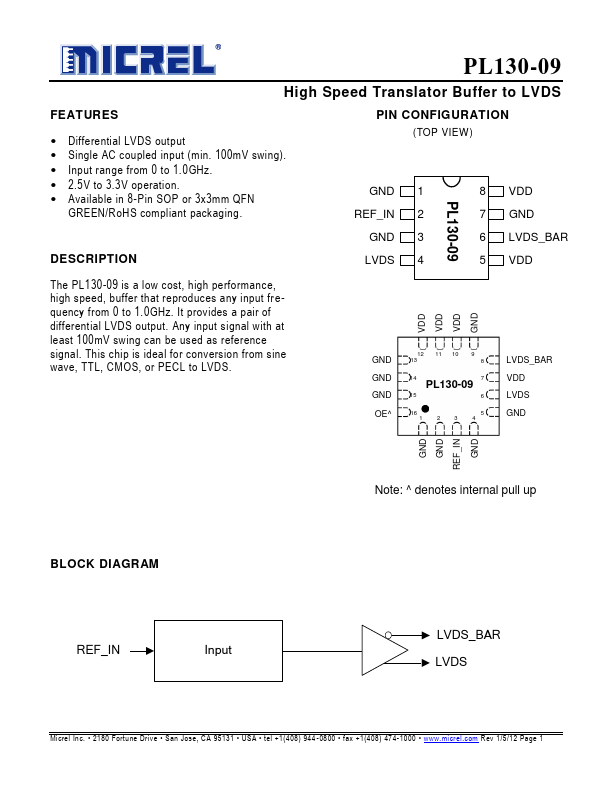

LVDS 4

5 VDD

The PL130-09 is a low cost, high performance, high speed, buffer that reproduces any input frequency from 0 to 1.0GHz. It provides a pair of differential LVDS output. Any input signal with at least 100m V swing can be used as reference signal. This chip is ideal for conversion from sine wave, TTL, CMOS, or PECL to LVDS.

VDD VDD VDD GND

GND GND GND OE^

12 11 10 13

9 8

14 7

15 6

16 5 123 4

LVDS_BAR VDD LVDS GND

GND GND REF_IN GND

Note: ^ denotes internal pull up

BLOCK DIAGRAM

REF_IN

Input

LVDS_BAR LVDS

Micrel Inc.

- 2180 Fortune Drive

- San Jose, CA 95131

- USA

- tel...