CD40103BMS

Description

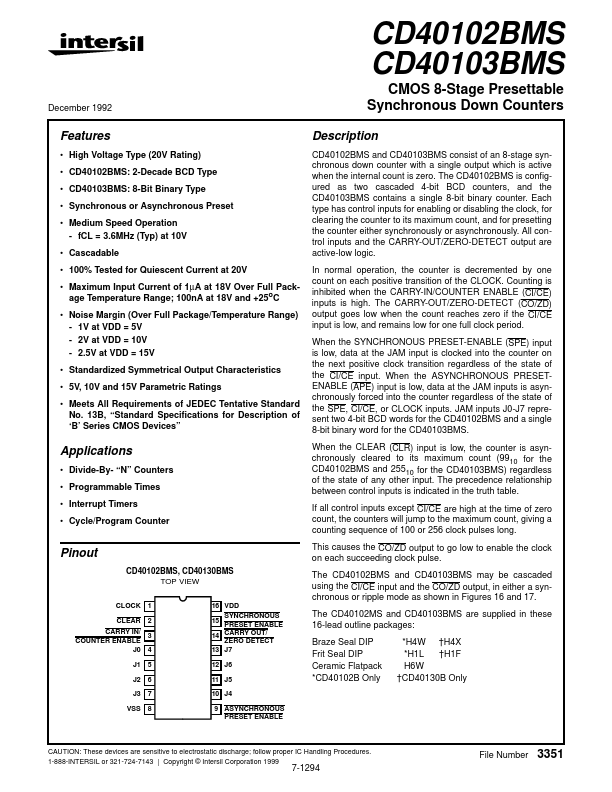

CD40102BMS and CD40103BMS consist of an 8-stage synchronous down counter with a single output which is active when the internal count is zero. The CD40102BMS is configured as two cascaded 4-bit BCD counters, and the CD40103BMS contains a single 8-bit binary counter. Each type has control inputs for enabling or disabling the clock, for clearing the counter to its maximum count, and for presetting the counter either synchronously or asynchronously. All control inputs and the CARRY-OUT/ZERO-DETECT output are active-low logic. In normal operation, the counter is decremented by one count on each positive transition of the CLOCK. Counting is inhibited when the CARRY-IN/COUNTER ENABLE (CI/CE) inputs is high. The CARRY-OUT/ZERO-DETECT (CO/ZD) output goes low when the count reaches zero if the CI/CE input is low, and remains low for one full clock period. When the SYNCHRONOUS PRESET-ENABLE (SPE) input is low, data at the JAM input is clocked into the counter on the next positive...