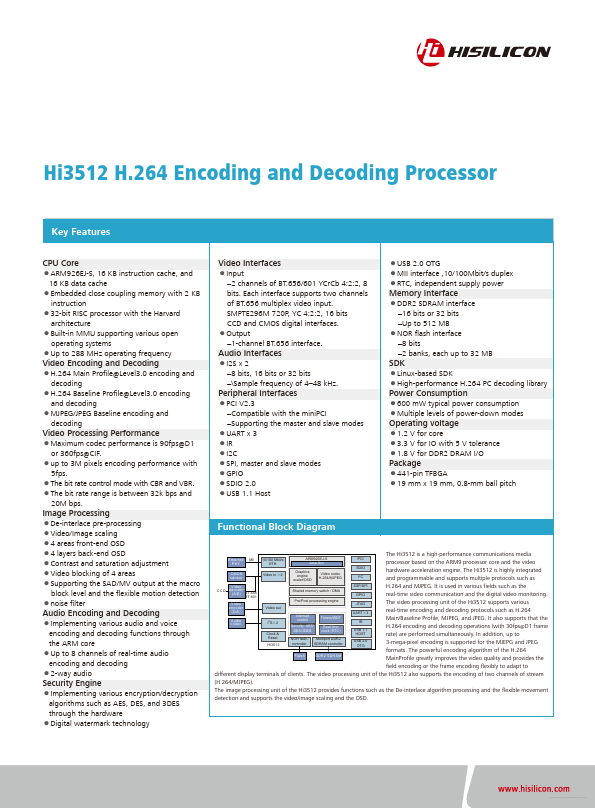

HI3512

Features

CPU Core

- ARM926EJ-S, 16 KB instruction cache, and 16 KB data cache

- Embedded close coupling memory with 2 KB instruction

- 32-bit RISC processor with the Harvard architecture

- Built-in MMU supporting various open operating systems

- Up to 288 MHz operating frequency

Video Interfaces

- Input

- 2 channels of BT.656/601 YCr Cb 4:2:2, 8 bits. Each interface supports two channels of BT.656 multiplex video input. SMPTE296M 720P, YC 4:2:2, 16 bits CCD and CMOS digital interfaces.

- Output

- 1-channel BT.656 interface.

- USB 2.0 OTG

- MII interface ,10/100Mbit/s duplex

- RTC, independent supply power

Memory Interface

- DDR2 SDRAM interface

- 16 bits or 32 bits

- Up to 512 MB

- NOR flash interface

- 8 bits

- 2 banks, each up to 32 MB

Audio Interfaces

- I2S x 2

- 8 bits, 16 bits or 32 bits

- Sample frequency of 4- 48 k Hz.

Video Encoding and Decoding

- H.264 Main Profile@Level3.0 encoding and decoding

- H.264 Baseline Profile@Level3.0 encoding and decoding

- MJPEG/JPEG Baseline encoding and...