S1216AATA-75-E

Description

The EDS1216AATA is a 128M bits SDRAM organized as 2,097,152 words × 16 bits × 4 banks. All inputs and outputs are synchronized with the positive edge of the clock. It is packaged in 54-pin plastic TSOP (II).

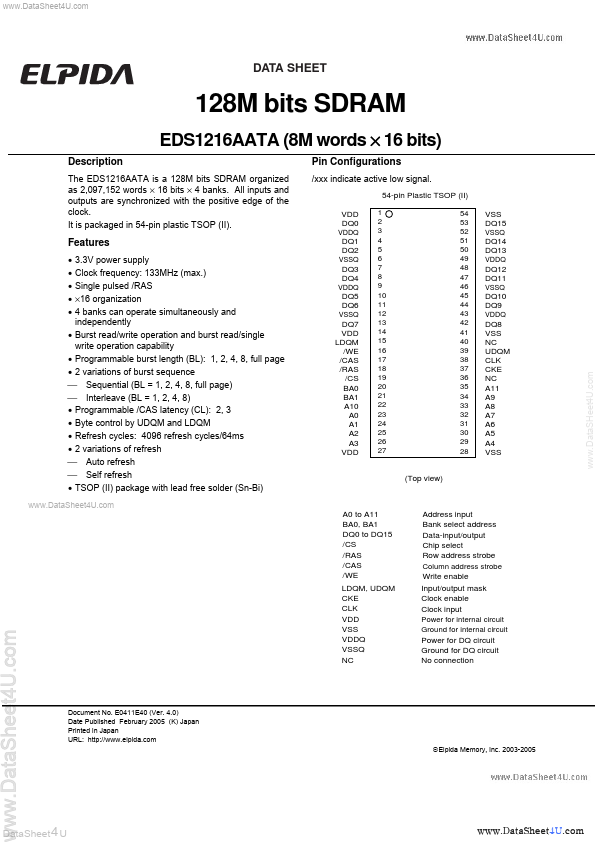

Pin Configurations

/xxx indicate active low signal.

54-pin Plastic TSOP (II) VDD DQ0

VDDQ

Features

- -

- -

- 3.3V power supply Clock frequency: 133MHz (max.) Single pulsed /RAS ×16 organization 4 banks can operate simultaneously and independently

- Burst read/write operation and burst read/single write operation capability

- Programmable burst length (BL): 1, 2, 4, 8, full page

- 2 variations of burst sequence Sequential (BL = 1, 2, 4, 8, full page) Interleave (BL = 1, 2, 4, 8)

- Programmable /CAS latency (CL): 2, 3

- Byte control by UDQM and LDQM

- Refresh cycles: 4096 refresh cycles/64ms

- 2 variations of refresh Auto refresh Self refresh

- TSOP (II) package with lead free solder (Sn-Bi)

..

DQ1 DQ2

VSSQ

DQ3 DQ4

VDDQ

DQ5 DQ6

VSSQ

(Top view) ww..

A0 to...