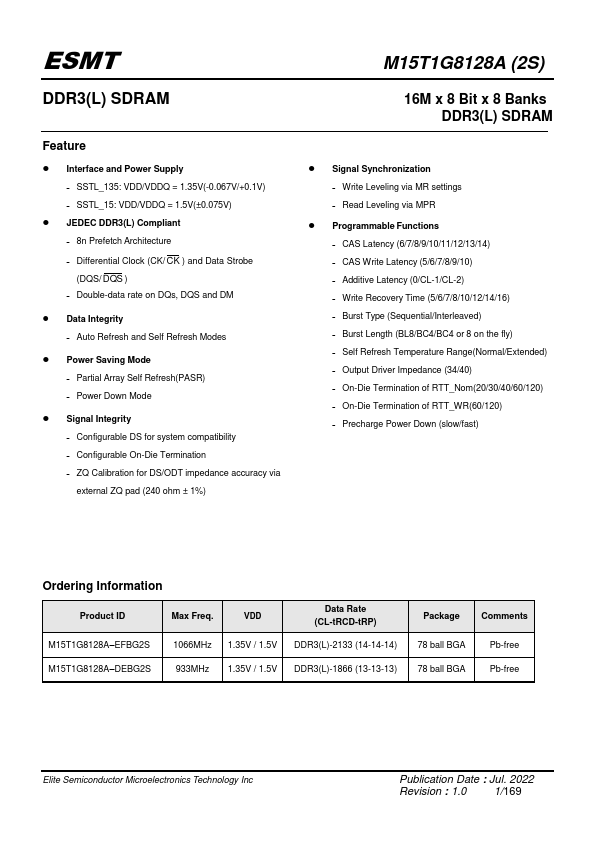

M15T1G8128A

Feature

- Interface and Power Supply ˗ SSTL_135: VDD/VDDQ = 1.35V(-0.067V/+0.1V) ˗ SSTL_15: VDD/VDDQ = 1.5V(±0.075V)

- JEDEC DDR3(L) pliant ˗ 8n Prefetch Architecture ˗ Differential Clock (CK/ CK ) and Data Strobe (DQS/ DQS ) ˗ Double-data rate on DQs, DQS and DM

- Data Integrity ˗ Auto Refresh and Self Refresh Modes

- Power Saving Mode ˗ Partial Array Self Refresh(PASR) ˗ Power Down Mode

- Signal Integrity ˗ Configurable DS for system patibility ˗ Configurable On-Die Termination ˗ ZQ Calibration for DS/ODT impedance accuracy via external ZQ pad (240 ohm ± 1%)

M15T1G8128A (2S)

16M x 8 Bit x 8 Banks DDR3(L) SDRAM

- Signal Synchronization ˗ Write Leveling via MR settings ˗ Read Leveling via MPR

- Programmable Functions ˗ CAS Latency (6/7/8/9/10/11/12/13/14) ˗ CAS Write Latency (5/6/7/8/9/10) ˗ Additive Latency (0/CL-1/CL-2) ˗ Write Recovery Time (5/6/7/8/10/12/14/16) ˗ Burst Type (Sequential/Interleaved) ˗ Burst Length (BL8/BC4/BC4 or 8 on the fly) ˗ Self Refresh Temperature...