AT24C02 Datasheet Text

Features

- Medium-voltage and Standard-voltage Operation

- 5.0 (VCC = 4.5V to 5.5V)

- 2.7 (VCC = 2.7V to 5.5V)

- Internally Organized 128 x 8 (1K), 256 x 8 (2K), 512 x 8 (4K), 1024 x 8 (8K) or 2048 x 8 (16K)

- Two-wire Serial Interface

- Schmitt Trigger, Filtered Inputs for Noise Suppression

- Bi-directional Data Transfer Protocol

- 100 kHz (2.7V) and 400 kHz (5V) patibility

- Write Protect Pin for Hardware Data Protection

- 8-byte Page (1K, 2K), 16-byte Page (4K, 8K, 16K) Write Modes

- Partial Page Writes are Allowed

- Self-timed Write Cycle (5 ms max)

- High-reliability

- Endurance: 1 Million Write Cycles

- Data Retention: 100 Years

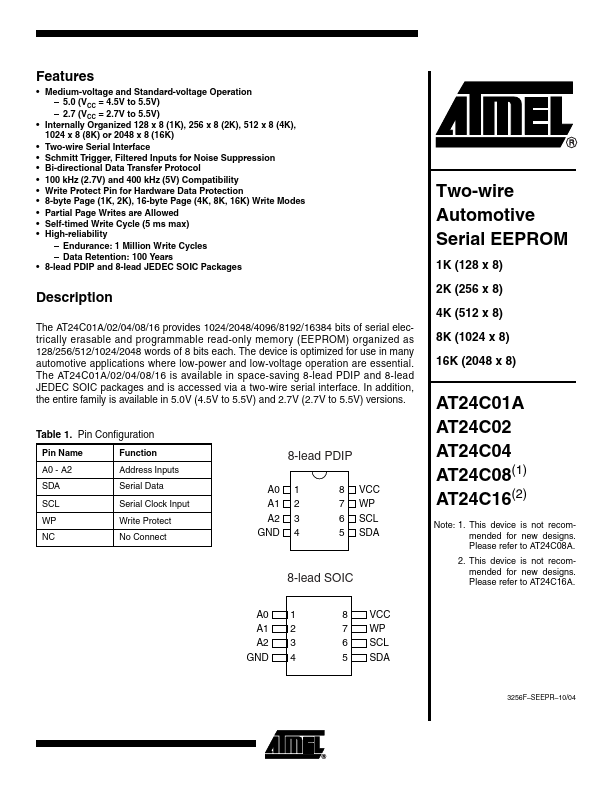

- 8-lead PDIP and 8-lead JEDEC SOIC Packages

Description

The AT24C01A/02/04/08/16 provides 1024/2048/4096/8192/16384 bits of serial electrically erasable and programmable read-only memory (EEPROM) organized as 128/256/512/1024/2048 words of 8 bits each. The device is optimized for use in many automotive applications where low-power and low-voltage operation are essential. The AT24C01A/02/04/08/16 is available in space-saving 8-lead PDIP and 8-lead JEDEC SOIC packages and is accessed via a two-wire serial interface. In addition, the entire family is available in 5.0V (4.5V to 5.5V) and 2.7V (2.7V to 5.5V) versions.

Table 1. Pin Configuration

Pin Name

Function

A0

- A2

Address Inputs

SDA

Serial Data

SCL

Serial Clock Input

WP...