S2052

FEATURES

- Functionally pliant with ANSI X3T11 Fibre Channel physical and transmission protocol standards and IEEE 802.3Z Gigabit Ethernet Applications

- Transmitter incorporates phase-locked loop (PLL) providing clock synthesis from low-speed reference

- Receiver PLL configured for clock and data recovery

- 1250 and 1062 Mb/s operation

- 10-bit parallel TTL patible interface

- 800m W typical power dissipation

- +3.3V power supply

- Low-jitter serial PECL patible interface

- Lock detect

- Local loopback

- 64 PQFP package

- Fibre Channel framing performed by receiver

- Continuous downstream clocking from receiver

- Drives 30m of Twinax cable directly

APPLICATIONS

High-speed data munications

- Workstation

- Frame buffer

- Switched networks

- Data broadcast environments

- Proprietary extended backplanes

- RAID drives

- Mass storage devices

GENERAL DESCRIPTION

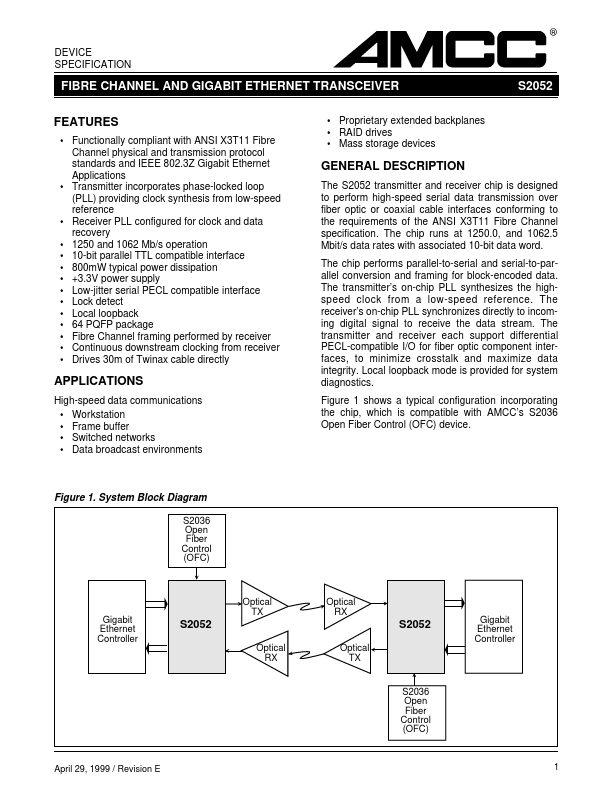

The S2052 transmitter and receiver chip is designed to perform high-speed serial data transmission over fiber optic or coaxial...