LTC6950

Overview

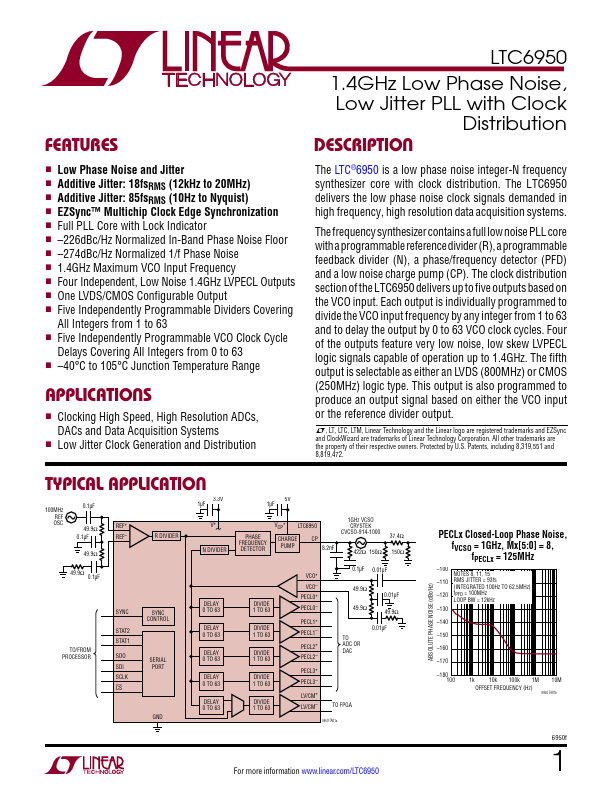

- Low Phase Noise and Jitter

- Additive Jitter: 18fsRMS (12kHz to 20MHz)

- Additive Jitter: 85fsRMS (10Hz to Nyquist)

- EZSync™ Multichip Clock Edge Synchronization

- Full PLL Core with Lock Indicator n -226dBc/Hz Normalized In-Band Phase Noise Floor n -274dBc/Hz Normalized 1/f Phase Noise

- 1.4GHz Maximum VCO Input Frequency

- Four Independent, Low Noise 1.4GHz LVPECL Outputs

- One LVDS/CMOS Configurable Output

- Five Independently Programmable Dividers Covering All Integers from 1 to 63

- Five Independently Programmable VCO Clock Cycle Delays Covering All Integers from 0 to 63 n -40°C to 105°C Junction Temperature Range