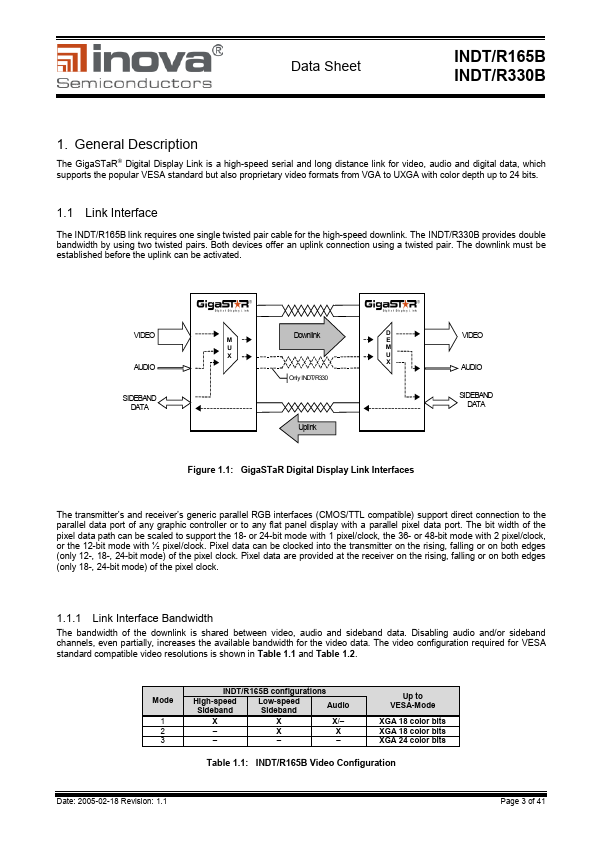

Description

3 1.1 Link Interface 3 1.1.1 Link Interface Bandwidth 3 1.2 Pixel Interface 4 1.2.1 General Information4 1.2.2 Pixel Interface Modes 5 1.2.3 Pixel Clock Sampling Modes 5 1.2.4 Pixel Data I/O Color Bit Mapping 7 1.3 Sideband Interface 8 1.3.1 General Information8 1.3.2 Low-speed Upstream Sideband Data Channel (SB0)9 1.3.3 High-speed Upstream Sideband Data Channel (SB1)9 1.3.4 Low-speed Downstream Sideband Data Channel (SB2) 9 1.3.5 High-speed Downstream Sideband Data Channel (SB3, SB4).

Features

- Supported VESA video resolutions:.

- INDT/R165B: VGA … XGA.

- INDT/R330B: VGA … UXGA.

- Flexible parallel graphics controller and LC-display interfaces:.

- 12-bit (½ pixel/clock).

- Tx only.

- 18- / 24-bit (1 pixel/clock).

- 36- / 48-bit (2 pixel/clock).

- Flexible pixel data clocking on rising/falling/both clock edges.

- Pixel Clock frequency: 24.

- 161 MHz.

- Easy adaptation to DVI and LDI/LVDS through standard inter.