Description

The M1025/26 is a VCSO (Voltage Controlled SAW Oscillator) based clock jitter attenuator PLL designed for clock jitter attenuation and frequency translation.

Features

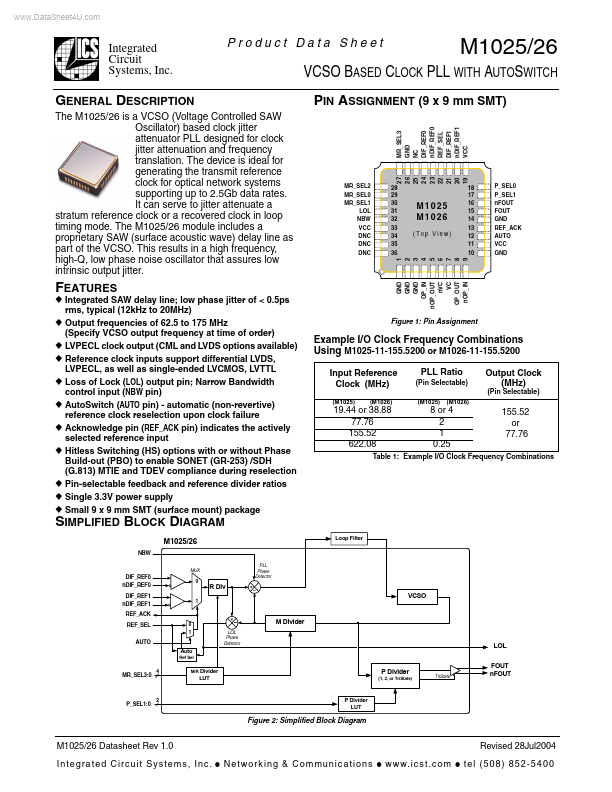

- Figure 1: Pin Assignment

Example I/O Clock Frequency Combinations Using M1025-11-155.5200 or M1026-11-155.5200

Input Reference Clock (MHz)

(M1025) (M1026)

GND GND GND OP_IN nOP_OUT nVC VC OP_OUT nOP_IN

1 2 3 4 5 6 7 8 9

PLL Ratio

(Pin Selectable)

(M1025) (M1026)

Output Clock (MHz)

(Pin Selectable)

19.44 or 38.88 77.76 155.52 622.08

8 or 4 2 1 0.25

155.52 or 77.76

Table 1: Example I/O Clock Frequency Combinations.

M1025_ICST.pdf

M1025_ICST.pdf