Description

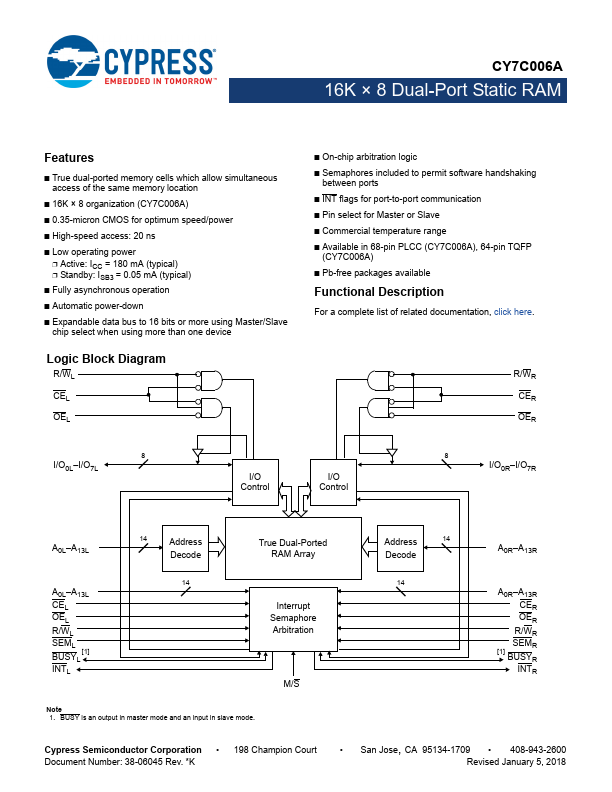

Architecture

The CY7C006A, CY7C007A, CY7C016A and CY7C017A consist of an array of 32K/16K words of 8 bits and 32K words of 9 bits each of dual-port RAM cells, I/O and address lines, and control signals (CE, OE, R/W).These control pins permit independent access for reads or writes to any location in memory.To handle simultaneous writes/reads to the same location, a BUSY pin is provided on each port.Two Interrupt (INT) pins can be utilized for port-to-port communication.Two Semaphore (SEM) co

Features

- True dual-ported memory cells which allow simultaneous access of the same memory location.

- 16K x 8 organization (CY7C006A)

w

w.

- 32K x 8 organization (CY7C007A).

- 16K x 9 organization (CY7C016A).

- 32K x 9 organization (CY7C017A).

- 0.35-micron CMOS for optimum speed/power.

- High-speed access: 12[1]/15/20 ns.

- Low operating power.

- Active: ICC = 180 mA (typical).

- Standby: ISB3 = 0.05 mA (typical).

- Full.