Description

s Programming support with Altera’s Master Programming Unit (MPU) or programming hardware from other manufacturers

s Additional design entry and simulation support provided by EDIF, LPM, Verilog HDL, VHDL, and other interfaces to popular EDA tools from manufacturers such as Cadence, Data I/O, Exemplar, Mentor Graphics, MINC, OrCAD, Synopsys, VeriBest, and Viewlogic

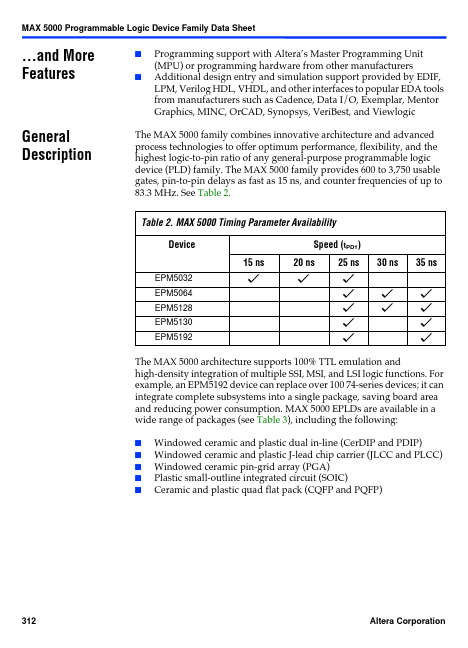

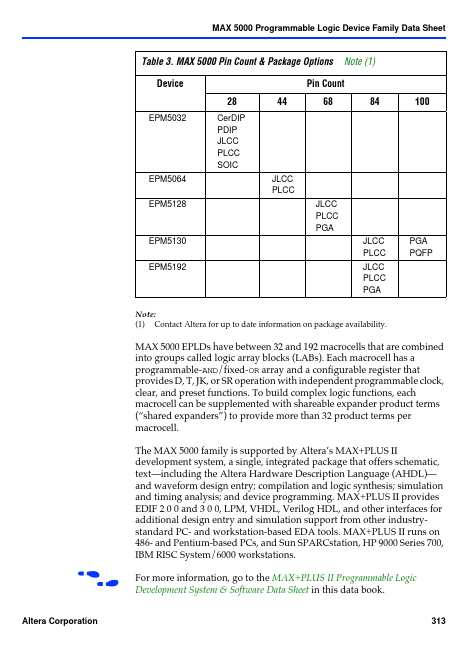

The MAX 5000 family combines innovative architecture and advanced process technologies to offer optimum performance, flexibility, a

Features

- s Advanced Multiple Array MatriX (MAX) 5000 architecture combining speed and ease-of-use of PAL devices with the density of programmable gate arrays

s Complete family of high-performance, erasable CMOS EPROM EPLDs for designs ranging from fast 28-pin address decoders to 100-pin LSI custom peripherals

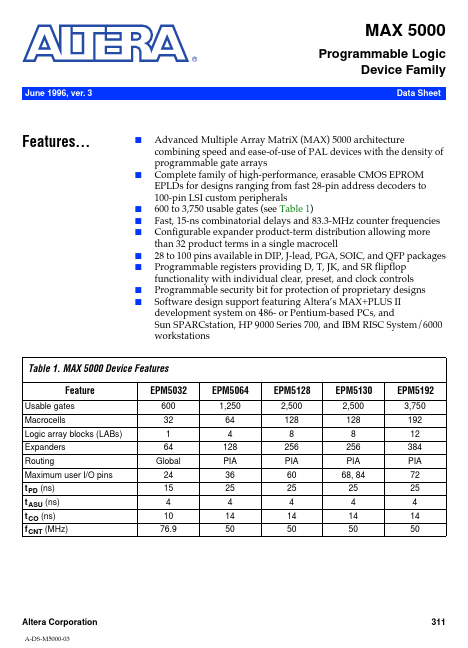

s 600 to 3,750 usable gates (see Table 1) s Fast, 15-ns combinatorial delays and 83.3-MHz counter frequencies s Configurable expander product-term distribution allowing more

than 32 product terms i.