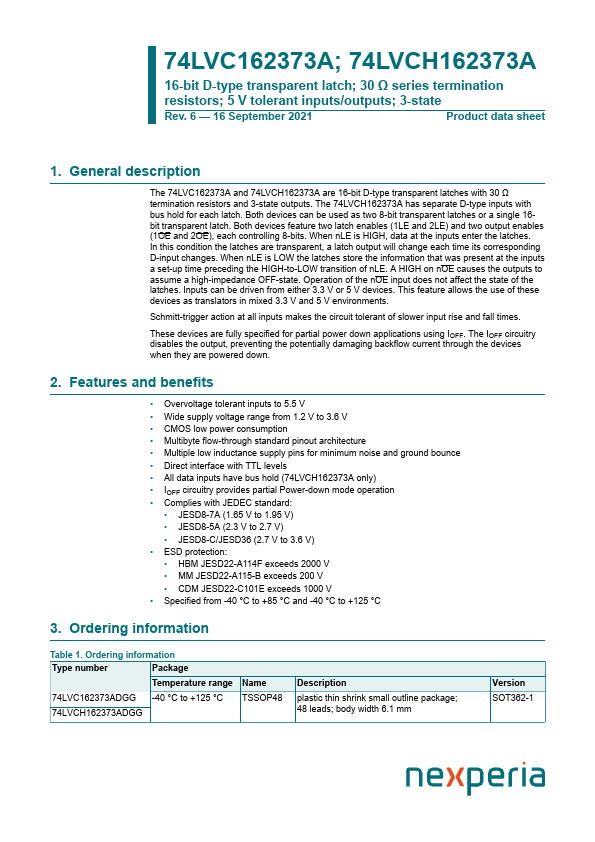

74LVCH162373A Overview

Description

The 74LVC162373A and 74LVCH162373A are 16-bit D-type transparent latches with 30 Ω termination resistors and 3-state outputs. The 74LVCH162373A has separate D-type inputs with bus hold for each latch.

Key Features

- Overvoltage tolerant inputs to 5.5 V

- Wide supply voltage range from 1.2 V to 3.6 V

- CMOS low power consumption

- Multibyte flow-through standard pinout architecture

- Multiple low inductance supply pins for minimum noise and ground bounce

- Direct interface with TTL levels

- All data inputs have bus hold (74LVCH162373A only)

- IOFF circuitry provides partial Power-down mode operation