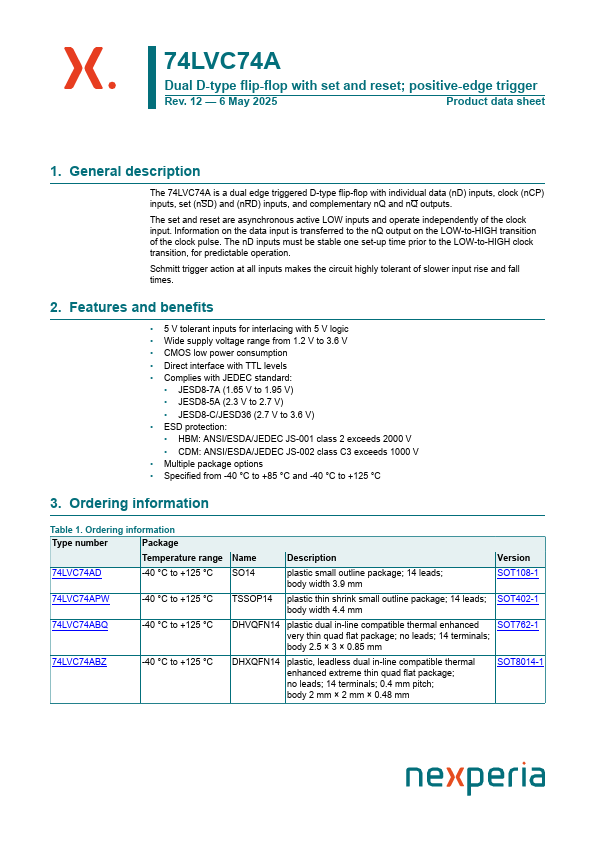

74LVC74A

Description

The 74LVC74A is a dual edge triggered D-type flip-flop with individual data (nD) inputs, clock (nCP) inputs, set (nSD) and (nRD) inputs, and plementary nQ and nQ outputs.

Key Features

- 5 V tolerant inputs for interlacing with 5 V logic

- Wide supply voltage range from 1.2 V to 3.6 V

- CMOS low power consumption

- Direct interface with TTL levels

- plies with JEDEC standard

- ESD protection

- HBM: ANSI/ESDA/JEDEC JS-001 class 2 exceeds 2000 V

- CDM: ANSI/ESDA/JEDEC JS-002 class C3 exceeds 1000 V

- Multiple package options

- Specified from -40 °C to +85 °C and -40 °C to +125 °C