74AVC16374-Q100 Overview

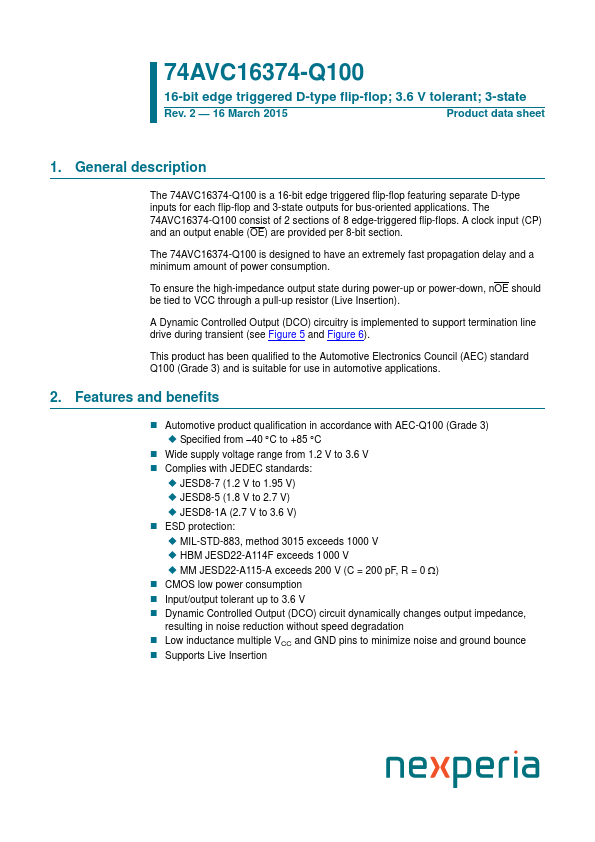

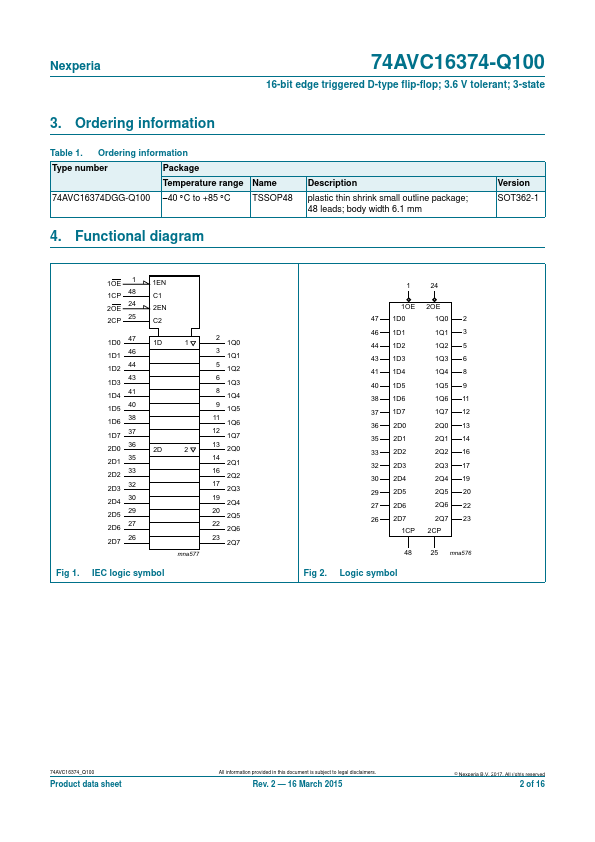

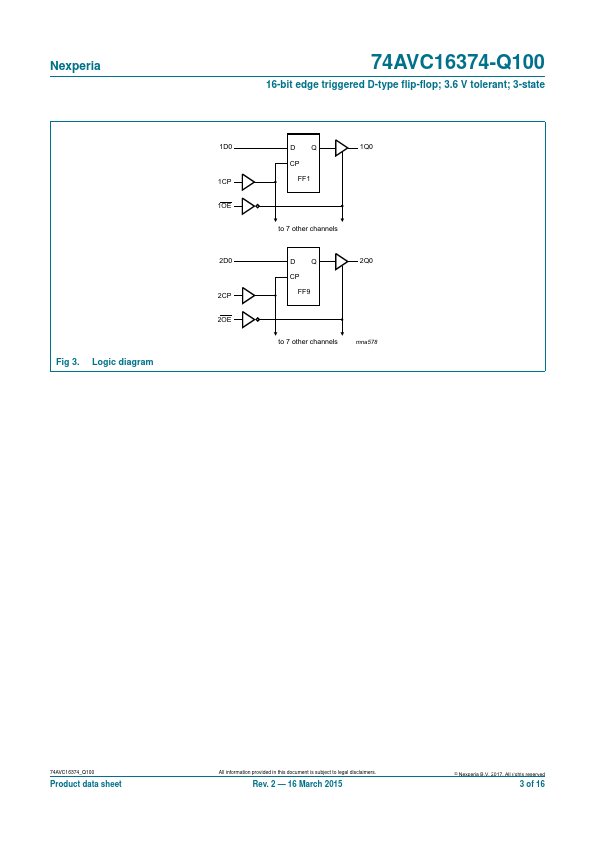

The 74AVC16374-Q100 is a 16-bit edge triggered flip-flop featuring separate D-type inputs for each flip-flop and 3-state outputs for bus-oriented applications. The 74AVC16374-Q100 consist of 2 sections of 8 edge-triggered flip-flops. A clock input (CP) and an output enable (OE) are provided per 8-bit section.

74AVC16374-Q100 Key Features

- Automotive product qualification in accordance with AEC-Q100 (Grade 3)

- Specified from 40 C to +85 C

- Wide supply voltage range from 1.2 V to 3.6 V

- plies with JEDEC standards

- JESD8-7 (1.2 V to 1.95 V)

- JESD8-5 (1.8 V to 2.7 V)

- JESD8-1A (2.7 V to 3.6 V)

- ESD protection

- MIL-STD-883, method 3015 exceeds 1000 V

- HBM JESD22-A114F exceeds 1000 V

74AVC16374-Q100 Applications

- Automotive product qualification in accordance with AEC-Q100 (Grade 3) Specified from 40 C to +85 C

- Wide supply voltage range from 1.2 V to 3.6 V

- plies with JEDEC standards