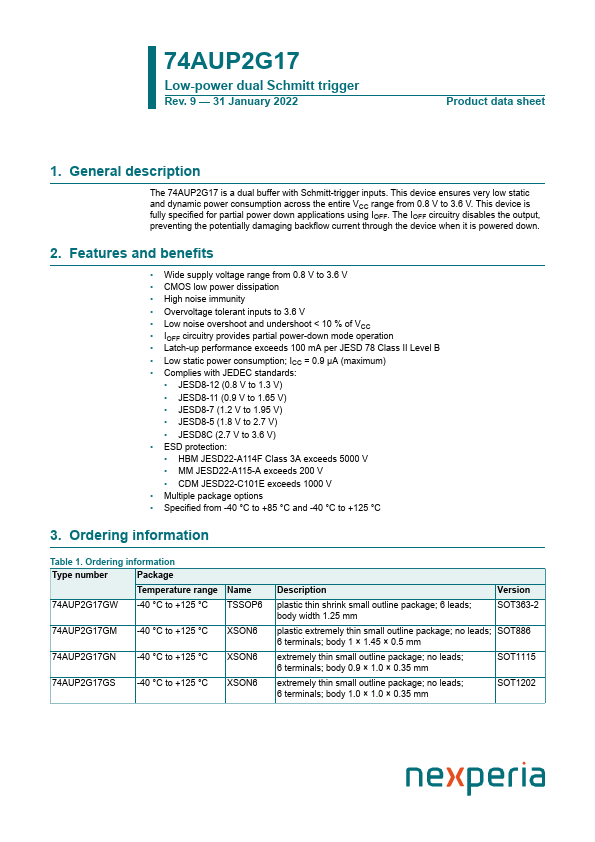

74AUP2G17 Description

The 74AUP2G17 is a dual buffer with Schmitt-trigger inputs. This device ensures very low static and dynamic power consumption across the entire VCC range from 0.8 V to 3.6 V. This device is fully specified for partial power down applications using IOFF.

74AUP2G17 Key Features

- Wide supply voltage range from 0.8 V to 3.6 V

- CMOS low power dissipation

- High noise immunity

- Overvoltage tolerant inputs to 3.6 V

- Low noise overshoot and undershoot < 10 % of VCC

- IOFF circuitry provides partial power-down mode operation

- Latch-up performance exceeds 100 mA per JESD 78 Class II Level B

- Low static power consumption; ICC = 0.9 μA (maximum)

- plies with JEDEC standards

- JESD8-12 (0.8 V to 1.3 V)

74AUP2G17 Applications

- Wide supply voltage range from 0.8 V to 3.6 V