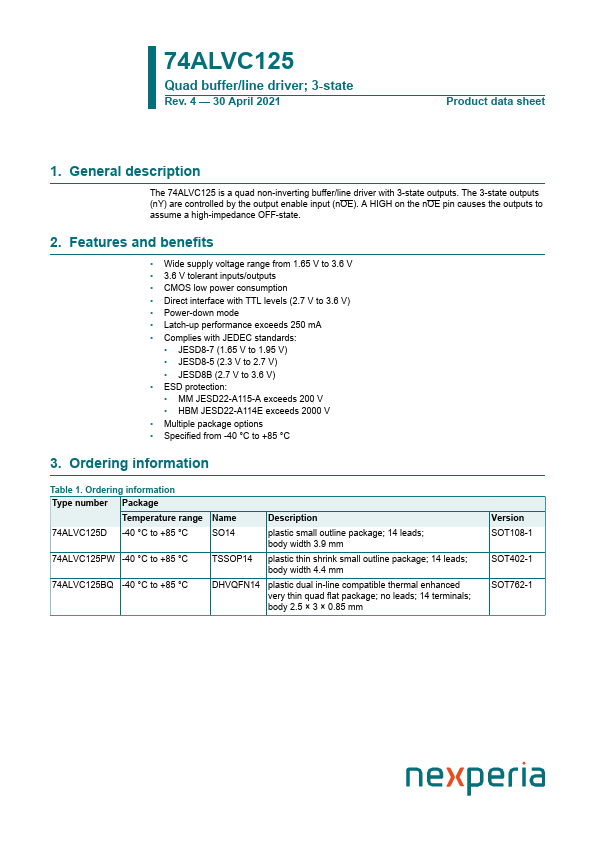

74ALVC125 Overview

Key Specifications

Package: TSSOP

Mount Type: Surface Mount

Pins: 14

Operating Voltage: 1.8 V

Description

The 74ALVC125 is a quad non-inverting buffer/line driver with 3-state outputs. The 3-state outputs (nY) are controlled by the output enable input (nOE).

Key Features

- Wide supply voltage range from 1.65 V to 3.6 V

- 3.6 V tolerant inputs/outputs

- CMOS low power consumption

- Direct interface with TTL levels (2.7 V to 3.6 V)

- Power-down mode