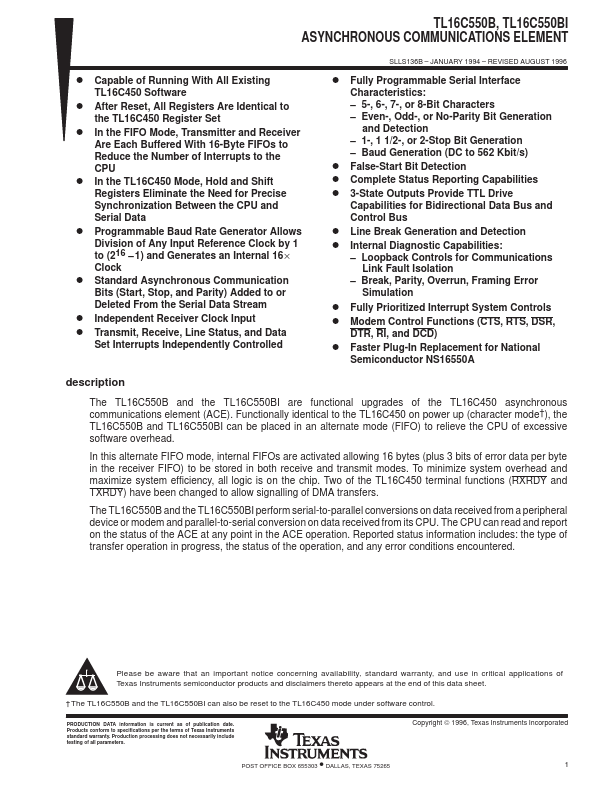

TL16C550B

description

The TL16C550B and the TL16C550BI are functional upgrades of the TL16C450 asynchronous munications element (ACE). Functionally identical to the TL16C450 on power up (character mode†), the TL16C550B and TL16C550BI can be placed in an alternate mode (FIFO) to relieve the CPU of excessive software overhead.

In this alternate FIFO mode, internal FIFOs are activated allowing 16 bytes (plus 3 bits of error data per byte in the receiver FIFO) to be stored in both receive and transmit modes. To minimize system overhead and maximize system efficiency, all logic is on the chip. Two of the TL16C450 terminal functions (RXRDY and TXRDY) have been changed to allow signalling of DMA transfers.

The TL16C550B and the TL16C550BI perform serial-to-parallel conversions on data received from a peripheral device or modem and parallel-to-serial conversion on data received from its CPU. The CPU can read and report on the status of the ACE at any point in the ACE operation. Reported status...