SN74LV10A

SN74LV10A is Triple 3-Input Positive-NAND Gate manufactured by Texas Instruments.

Features

- VCC operation of 2 V to 5.5 V

- Max tpd of 7 ns at 5 V

- Typical VOLP (Output Ground Bounce) <0.8 V at

VCC = 3.3 V, TA = 25°C

- Typical VOHV (Output VOH Undershoot) >2.3 V at

VCC = 3.3 V, TA = 25°C

- Ioff Supports Partial-Power-Down Mode Operation

- Latch-Up Performance Exceeds 100 m A Per JESD

78, Class II

2 Applications

- Alarm / tamper detect circuit

- S-R latch

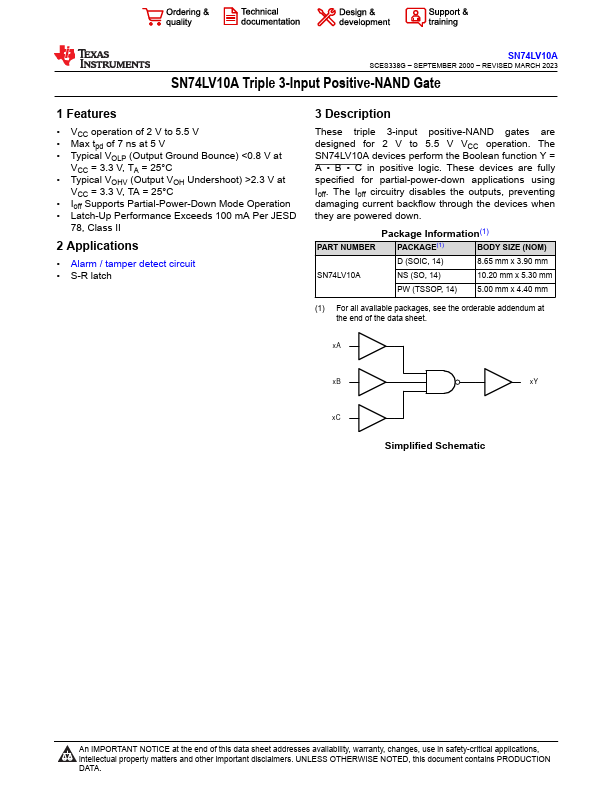

3 Description

These triple 3-input positive-NAND gates are designed for 2 V to 5.5 V VCC operation. The SN74LV10A devices perform the Boolean function Y = A

- B

- C in positive logic. These devices are fully specified for partial-power-down applications using Ioff. The Ioff circuitry disables the outputs, preventing damaging current backflow through the devices when they are powered down.

Package Information(1)

PART NUMBER

PACKAGE(1)

BODY SIZE (NOM)

D (SOIC, 14)

8.65 mm x 3.90 mm

NS (SO, 14)

10.20 mm x 5.30 mm

PW (TSSOP, 14)

5.00 mm x 4.40 mm

(1) For all available packages, see the orderable addendum at the end of the data sheet. x A x B x Y x C

Simplified Schematic

An IMPORTANT NOTICE at the end of this data sheet addresses availability, warranty, changes, use in safety-critical applications, intellectual property matters and other important disclaimers. UNLESS OTHERWISE NOTED, this document contains PRODUCTION DATA.

SCES338G

- SEPTEMBER 2000

- REVISED MARCH 2023

.ti.

Table of Contents

1 Features

1 2 Applications 1 3 Description

1 4 Revision History 2 5 Pin Configuration and Functions 3 6 Specifications 4

6.1 Absolute Maximum Ratings 4 6.2 ESD...