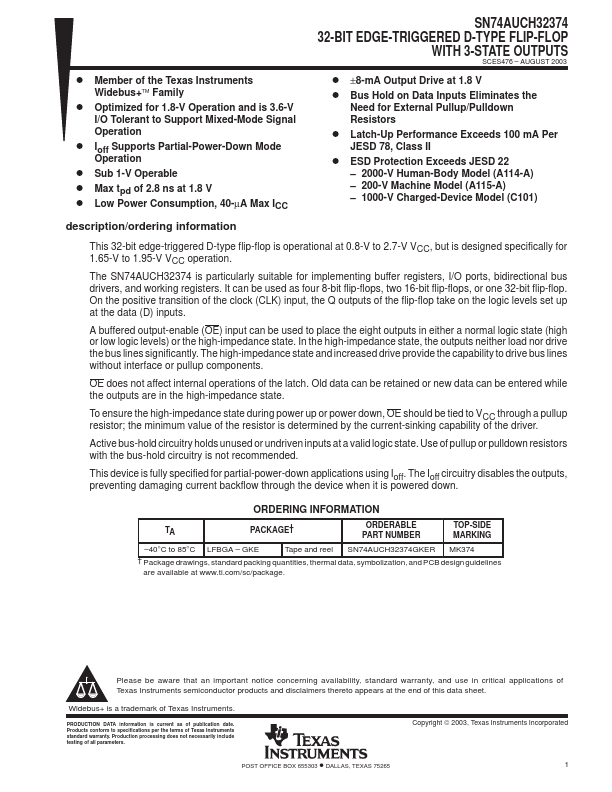

- Part: SN74AUCH32374

- Description: 32-BIT EDGE-TRIGGERED D-TYPE FLIP-FLOP

- Manufacturer: Texas Instruments

- Size: 281.21 KB

Related Texas Instruments Datasheets

| Part Number | Description |

|---|---|

| SN74AUCH32244 | 32-BIT BUFFER/DRIVER |

| SN74AUCH16244 | 16-BIT BUFFER/DRIVER |

| SN74AUCH16374 | 16-BIT EDGE-TRIGGERED D-TYPE FLIP-FLOP |

| SN74AUCH244 | OCTAL BUFFER/DRIVER |

| SN74AUCH245 | OCTAL BUS TRANSCEIVER |