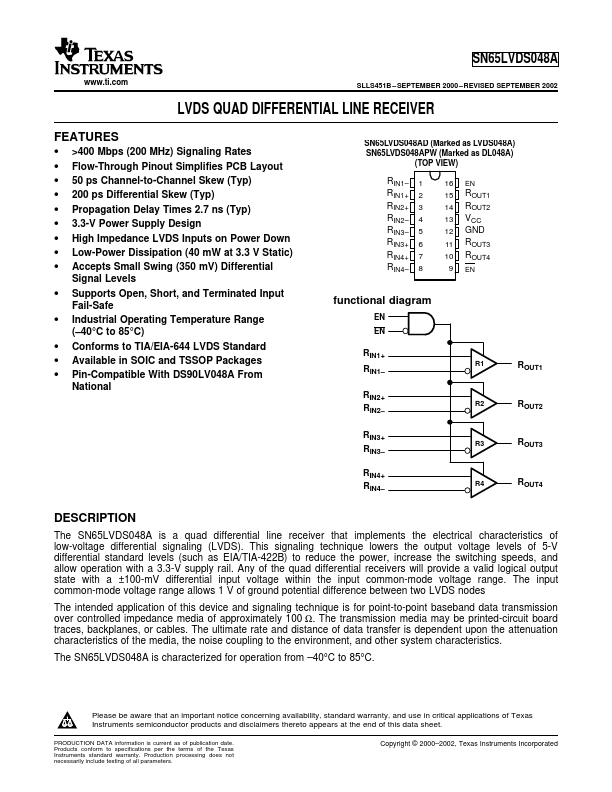

SN65LVDS048A

SN65LVDS048A is LVDS QUAD DIFFERENTIAL LINE DRIVER manufactured by Texas Instruments.

.ti.

SLLS451B

- SEPTEMBER 2000

- REVISED SEPTEMBER 2002

LVDS QUAD DIFFERENTIAL LINE RECEIVER

Features

- >400 Mbps (200 MHz) Signaling Rates

- Flow-Through Pinout Simplifies PCB Layout

- 50 ps Channel-to-Channel Skew (Typ)

- 200 ps Differential Skew (Typ)

- Propagation Delay Times 2.7 ns (Typ)

- 3.3-V Power Supply Design

- High Impedance LVDS Inputs on Power Down

- Low-Power Dissipation (40 mW at 3.3 V Static)

- Accepts Small Swing (350 mV) Differential

Signal Levels

- Supports Open, Short, and Terminated Input Fail-Safe

- Industrial Operating Temperature Range (- 40°C to 85°C)

- Conforms to TIA/EIA-644 LVDS Standard

- Available in SOIC and TSSOP Packages

-...