SN65DSI86-Q1

SN65DSI86-Q1 is MIPI DSI to eDP Bridge manufactured by Texas Instruments.

Product Folder

Sample & Buy

Technical Documents

Tools & Software

Support & munity

SLLSEJ5A

- JULY 2014

- REVISED DECEMBER 2015

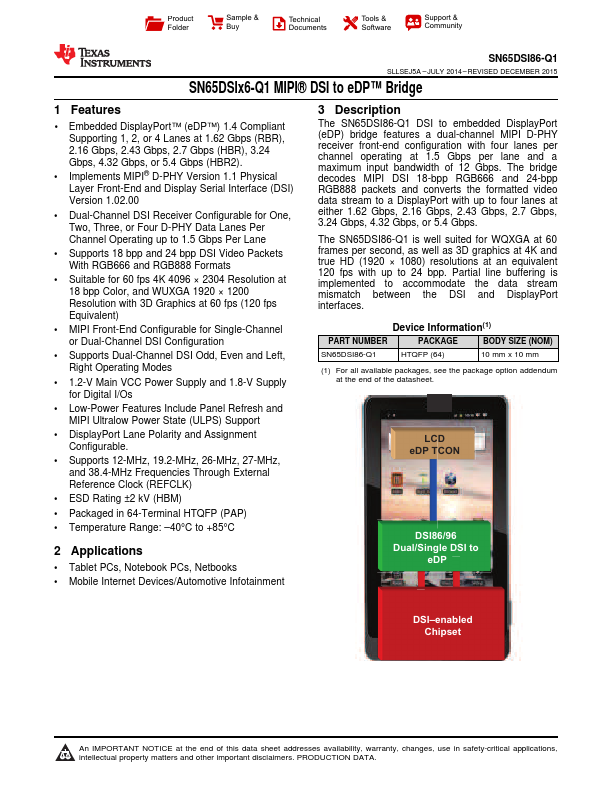

SN65DSIx6-Q1 MIPI® DSI to e DP™ Bridge

1 Features

- 1 Embedded Display Port™ (e DP™) 1.4 pliant Supporting 1, 2, or 4 Lanes at 1.62 Gbps (RBR), 2.16 Gbps, 2.43 Gbps, 2.7 Gbps (HBR), 3.24 Gbps, 4.32 Gbps, or 5.4 Gbps (HBR2).

- Implements MIPI® D-PHY Version 1.1 Physical Layer Front-End and Display Serial Interface (DSI) Version 1.02.00

- Dual-Channel DSI Receiver Configurable for One, Two, Three, or Four D-PHY Data Lanes Per Channel Operating up to 1.5 Gbps Per Lane

- Supports 18 bpp and 24 bpp DSI Video Packets With RGB666 and RGB888 Formats

- Suitable for 60 fps 4K 4096 × 2304 Resolution at 18 bpp Color, and WUXGA 1920 × 1200 Resolution with 3D Graphics at 60 fps (120 fps Equivalent)

- MIPI Front-End Configurable for Single-Channel or Dual-Channel DSI Configuration

- Supports Dual-Channel DSI Odd, Even and Left, Right Operating Modes

- 1.2-V Main VCC Power Supply and 1.8-V Supply for Digital I/Os

- Low-Power Features

Include Panel Refresh and MIPI Ultralow Power State (ULPS) Support

- Display Port Lane Polarity and Assignment Configurable.

- Supports 12-MHz, 19.2-MHz, 26-MHz, 27-MHz, and 38.4-MHz Frequencies Through External Reference Clock (REFCLK)

- ESD Rating ±2 k V (HBM)

- Packaged in 64-Terminal HTQFP (PAP)

- Temperature Range:

- 40°C to +85°C

2 Applications

- Tablet PCs, Notebook PCs, Netbooks

- Mobile Internet Devices/Automotive Infotainment

3...