Datasheet Summary

.ti.

SNAS625A

- SEPTEMBER 2013

- REVISED OCTOBER 2013

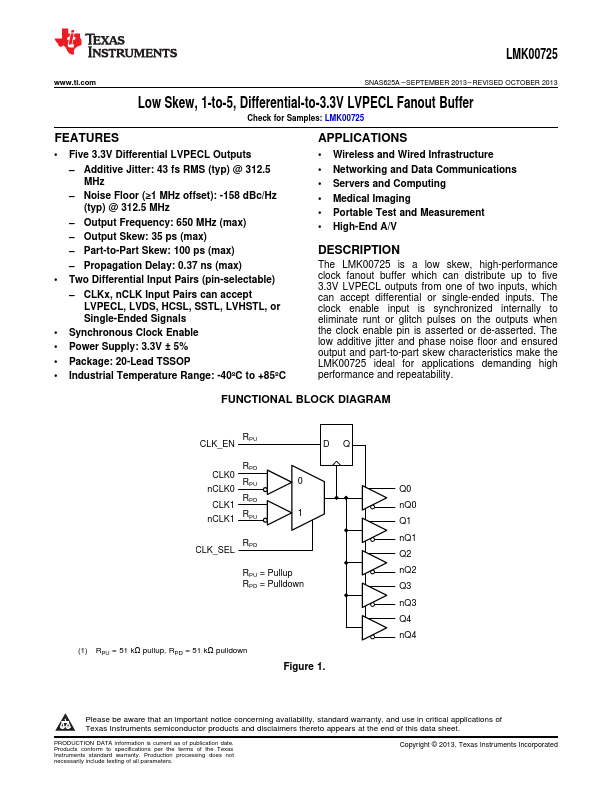

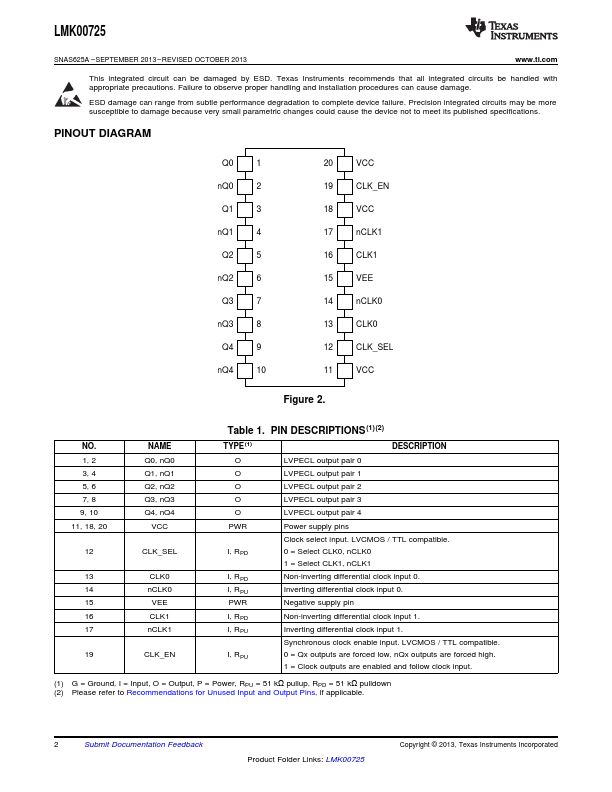

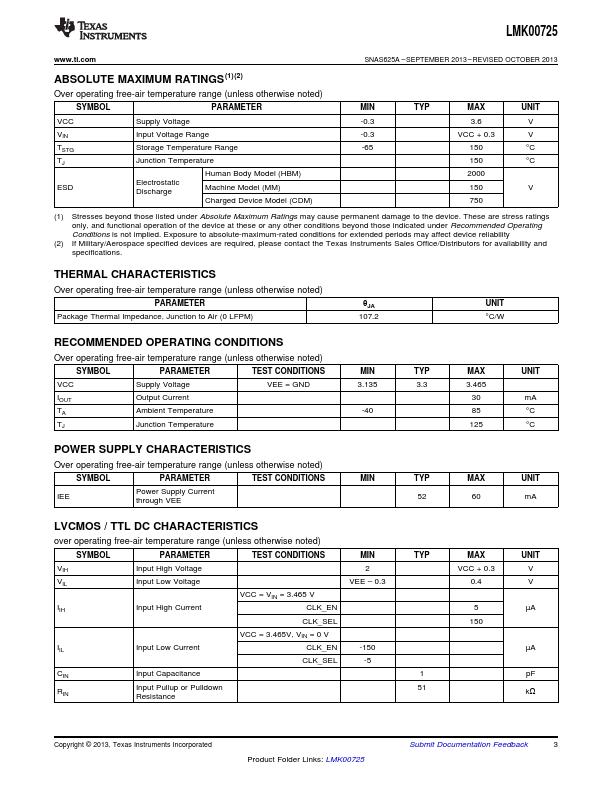

Low Skew, 1-to-5, Differential-to-3.3V LVPECL Fanout Buffer

Check for Samples: LMK00725

Features

- Five 3.3V Differential LVPECL Outputs

- Additive Jitter: 43 fs RMS (typ) @ 312.5 MHz

- Noise Floor (≥1 MHz offset): -158 dBc/Hz (typ) @ 312.5 MHz

- Output Frequency: 650 MHz (max)

- Output Skew: 35 ps (max)

- Part-to-Part Skew: 100 ps (max)

- Propagation Delay: 0.37 ns (max)

- Two Differential Input Pairs (pin-selectable)

- CLKx, nCLK Input Pairs can accept LVPECL, LVDS, HCSL, SSTL, LVHSTL, or Single-Ended Signals

- Synchronous Clock Enable

- Power Supply: 3.3V ± 5%

- Package: 20-Lead TSSOP

- Industrial Temperature...