DAC3152 Overview

Description

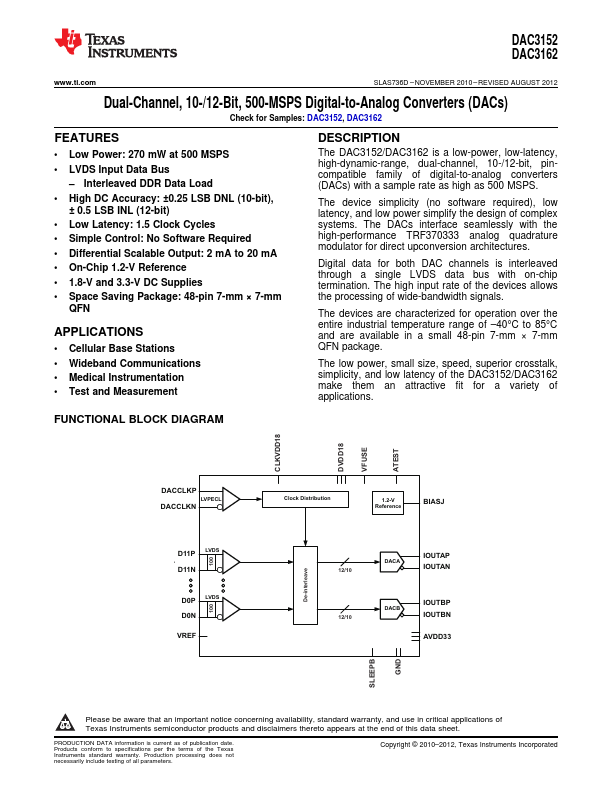

The DAC3152/DAC3162 is a low-power, low-latency, high-dynamic-range, dual-channel, 10-/12-bit, pincompatible family of digital-to-analog converters (DACs) with a sample rate as high as 500 MSPS. The device simplicity (no software required), low latency, and low power simplify the design of complex systems.

Key Features

- Low Power: 270 mW at 500 MSPS

- LVDS Input Data Bus – Interleaved DDR Data Load

- High DC Accuracy: ±0.25 LSB DNL (10-bit), ± 0.5 LSB INL (12-bit)

- Low Latency: 1.5 Clock Cycles

- Simple Control: No Software Required

- Differential Scalable Output: 2 mA to 20 mA

- On-Chip 1.2-V Reference

- 1.8-V and 3.3-V DC Supplies

- Space Saving Package: 48-pin 7-mm × 7-mm QFN