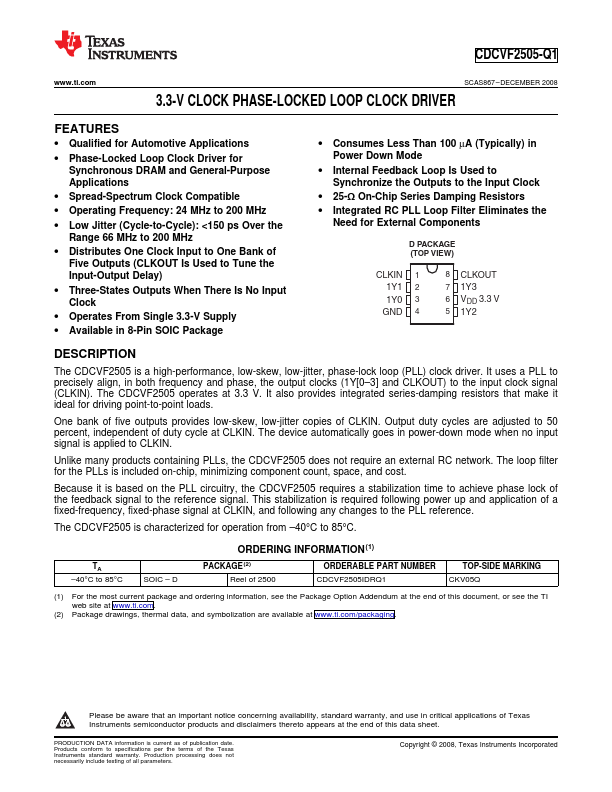

CDCVF2505-Q1 Overview

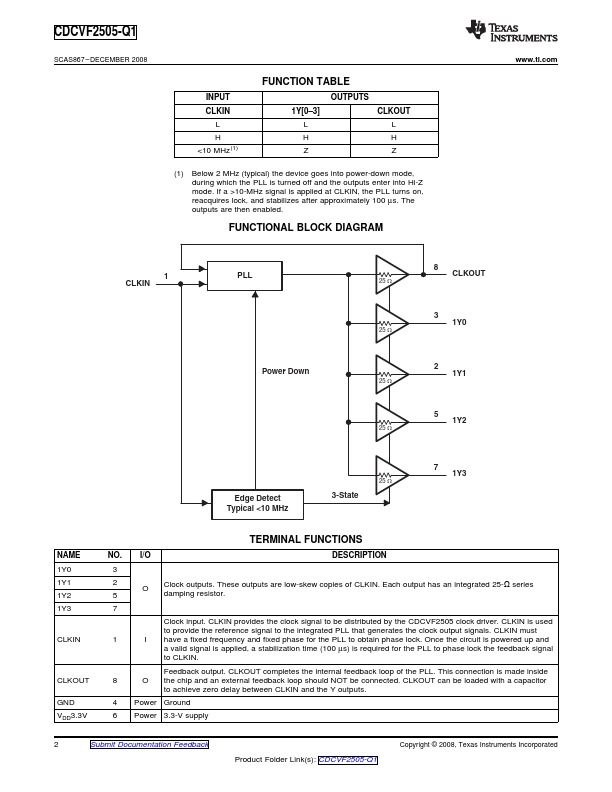

The CDCVF2505 is a high-performance, low-skew, low-jitter, phase-lock loop (PLL) clock driver. It uses a PLL to precisely align, in both frequency and phase, the output clocks (1Y[0 3] and CLKOUT) to the input clock signal (CLKIN). The CDCVF2505 operates at 3.3.

CDCVF2505-Q1 Key Features

- Qualified for Automotive

CDCVF2505-Q1 Applications

- Phase-Locked Loop Clock Driver for