CDCVF111

Overview

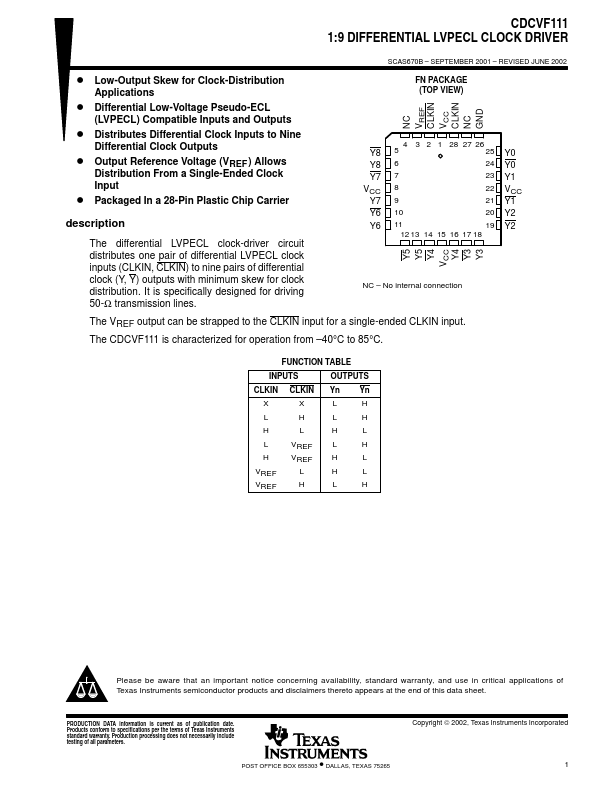

The differential LVPECL clock-driver circuit distributes one pair of differential LVPECL clock inputs (CLKIN, CLKIN) to nine pairs of differential clock (Y, Y) outputs with minimum skew for clock distribution. It is specifically designed for driving 50-Ω transmission lines.